1.ADC的定义

ADC即模拟数字转换器(英语:Analog-to-digital converter)是用于将模拟形式的连续信号转换为数字形式的离散信号的一类设备。

2.ADC输入的主要接口电路与选型

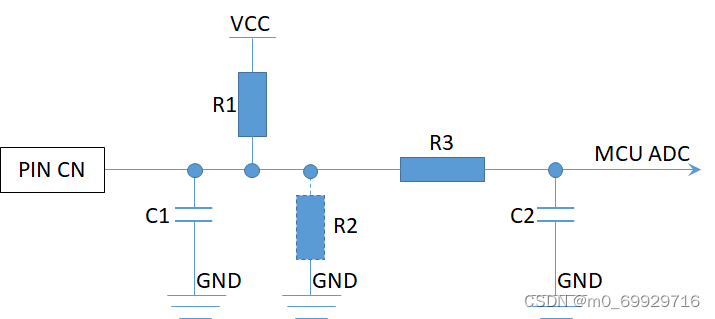

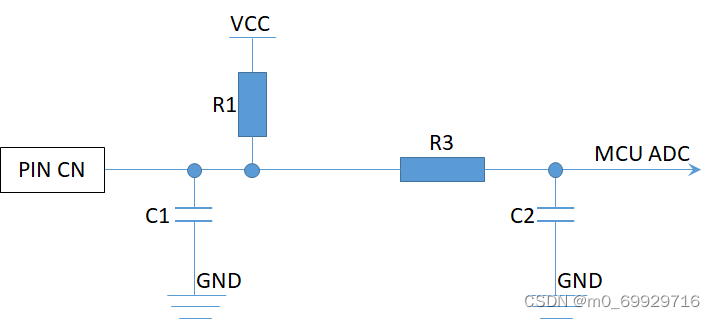

2.1.主要接口电路

其中:

C1为ESD(防静电)电容;

R1和R2分别为上拉和下拉电阻;

R3为限流电阻;

C2为低通滤波电容。

其中C1/R2的GND最好接数字地(DGND),C2的GND最好接模拟地(AGND),可有效的避免数字地波动对模拟地的影响,保证MCU采集模拟信号的稳定性。

2.2.主要元器件选型

下面逐个对各自选型进行介绍

2.2.1.ESD电容C1

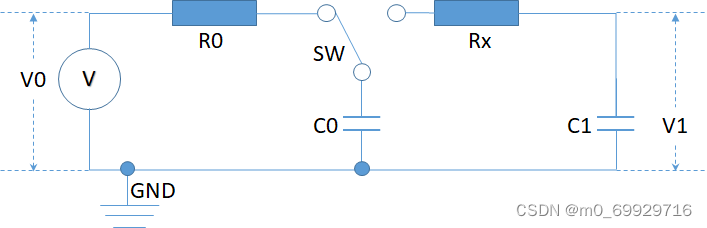

2.2.1.1. ESD放电电路

其中:

V0为放电电压;

R0为模拟人体阻抗;

Rx为模拟线束上阻抗

V1为V0放电后加在C1的电压

2.2.1.2.ESD电容计算

C0的等效阻抗为Z(C0)=1/(jwC0)

C1的等效阻抗为Z(C1)=1/(jwC1)

1)在C0充电时刻,C0两端的电压充满情况下等于V0:

2)C0放电情况下,Z(C0),Z(C1),Rx形成串联分压电路,但是Rx指线束的电阻,一般在几十毫欧,可或略。模型可等效为Z(C0)与Z(C1)形成串联分压电路。利用串联店里电流相等法则,计算式如下

V0/(Z(C0)+Z(C1))=V1/(Z(C1)

化简计算过程如下

V0/(1/(jwC0)+1/(jwC1))=V1/(1/(jwC1))

V0/(1/C0+1/C1)=V1/(1/C1)

最后导出

V1=V0*C0/(C0+C1)

1)实际案例计算

以AEC-Q200试验方法要求,C0=150pF 。假设ESD静电要求是+-2KV,一般C1不同封装下的耐压值最大是+-200V,可计算出

C1=V0*C0/V1-C0=2000V*150pF/200V-150pF=1.35nF.

假设ESD静电要求是+-4KV,那么C1就要配置大点的3.85nF.

2)那么C1是不是配置越大越好,答案是否定的。

如果设置过大,正常工作时,上拉1到VCC的电阻R1会与C1形成低通滤波,会导致针脚实际输入的电压因为给C1充电或放电一直未充满或一直未放干净,导致MCU ADC采样的电压值不准确以及采样速度,影响实际功能。C1原则上选取值小于C2或与C2处于同一个数量级。

2.2.2.R1/R2电阻选择(仅以上拉情况R1举例,R2基本同理)

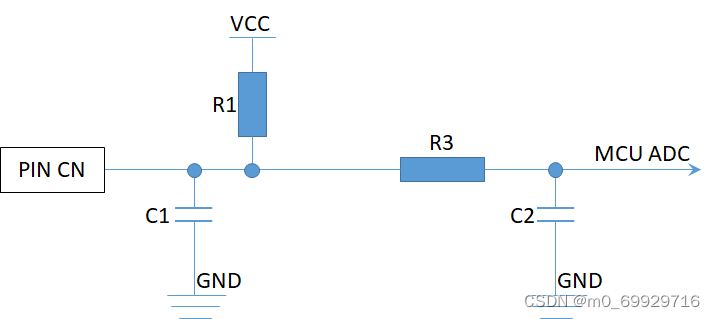

2.2.2.1. 主要接口电路

2.2.2.2. R1电阻计算

前提:外部传感器无特殊要求的情况下(后续文章会讲到传感器的特殊要求)

主要考虑封装与功率。

各主要电阻封装的功率情况如下

0201 1/20W

0402 1/16W

0603 1/10W

0805 1/8W

1206 1/4W

举例选用0603封装,假设系统供电是Vbat=9~16V,根据公式P=U*U/R1得出:R1=U*U/P

0603电阻最大功耗1/10W,但是我们不能以最大1/10W去计算,需要留余量,一般是1/10W*75%.

对于U(电压),我们需要考虑PIN对12V短路或对地短路情况,我们可以发现对电源短路情况下,R1的压降最大,所以R1(Min)=U*U/P=(16-5)*(16-5)/(1/10*75%)=1613ohm

即R1最小选择1613ohm,那么可以取比较接近的标准电阻值,如2kohm

笔者注:为了简化计算,未考虑VCC,温漂情况下的误差。

2.2.3.R3电阻选择

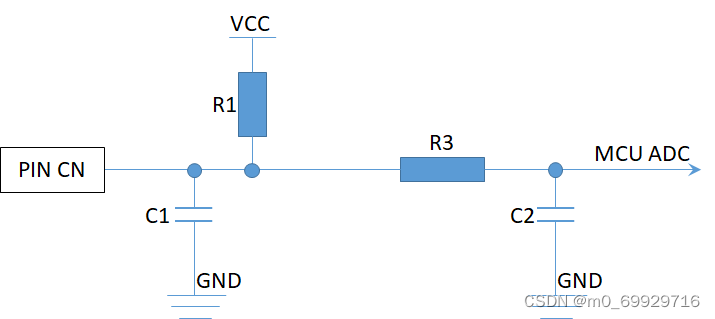

2.2.3.1. 主要接口电路

2.2.3.2. R3电阻计算

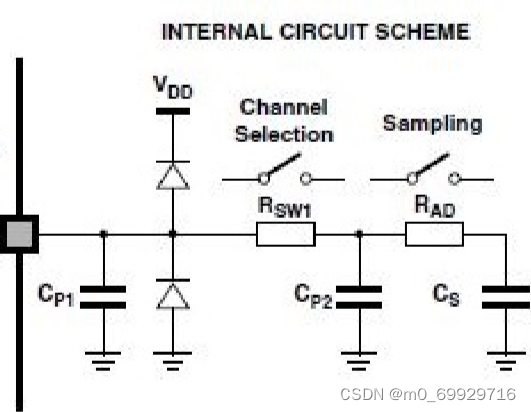

介绍R3电阻计算之前,先介绍MCU ADC的功能。ADC的采样电路如下,其中在电路内部有上下两个嵌位二极管,以硅管为例,在ADC端口可以嵌位到-0.7V~5.7V(VDD假设为5V供电).

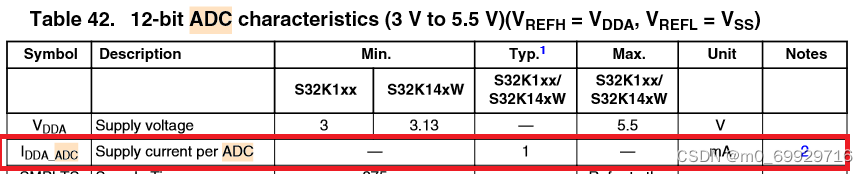

以NXP FS32K1xx系列为例,假设一5V供电,可以看出流过嵌位二极管的电流要小于1mA,设计来说,应当留有余量,实际流过嵌位二极管的电流要控制在50%~10%之间,举例50%如下

输入电压按短路电源的9~16V,嵌位二极管以硅管为例计算:

R3=(Vbat-0.7V-VDD)/1mA*50%=(16V-0.7V-5)/0.5mA=20.6kohm

可选择常规电阻21kohm

另外,反算下功耗是否满足:

P=(0.5*0.001)*(0.5*0.001)*21*1000=5.25mW<1/20W(@0402封装),所以可以选用0402封装或更大的封装

2.2.4.C2电容选择

2.2.4.1. 主要接口电路

2.2.4.2. C2电容计算

主要考虑低通滤波常数。假设设计要求滤波常数小于1ms,那么R3*C2<1ms,紧接2.2.3 R3计算可知:C2<1ms/R3=1ms/21k=47.6nF,那么可选择常规值47nF或22nF

4950

4950

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?