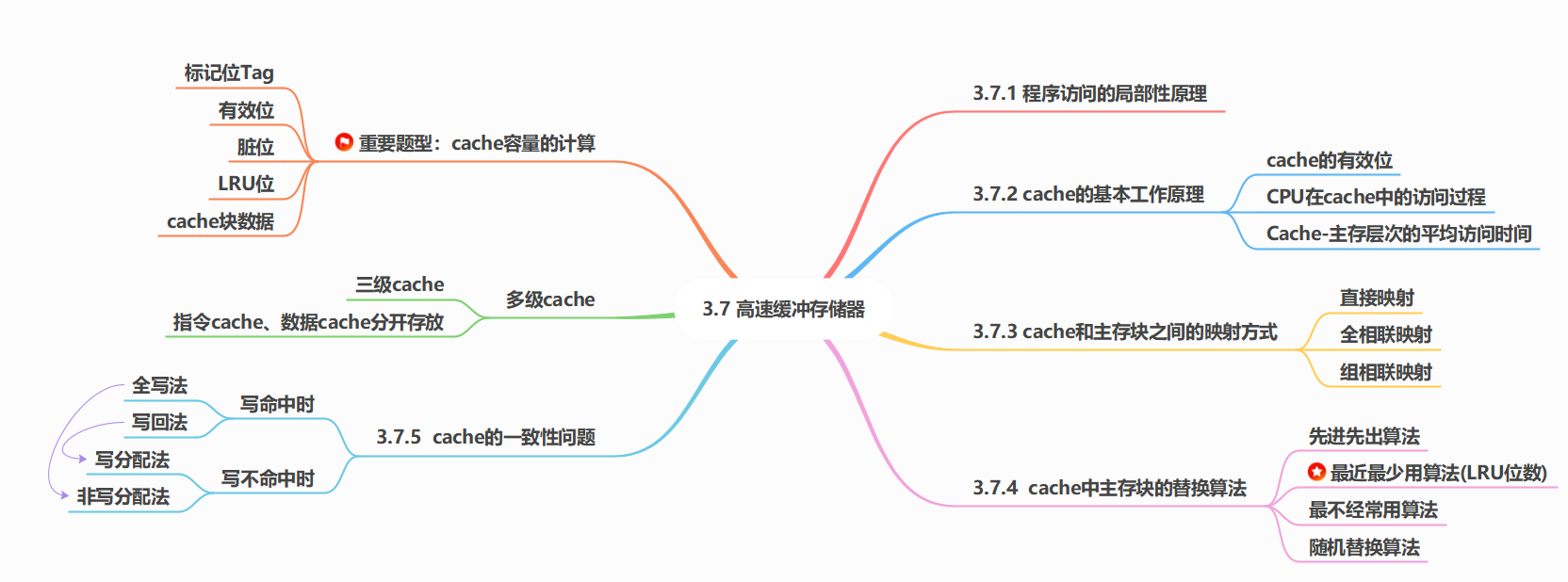

3.7 高速缓冲存储器

除了上一节介绍的并行存储器结构技术可以缓解CPU和主存之间的速度匹配问题以外,在CPU和主存之间设置高速缓冲寄存器Cache也可以提高CPU访问指令和数据的速度。

3.7.1 程序访问的局部性原理⭐️

对大量典型程序运行情况分析的结果表明,在较短时间间隔内,程序产生的地址往往集中在存储空间的一个很小范围,这种现象称为程序访问的局部性。这种局部性可细分为时间局部性和空间局部性。

时间局部性是指被访问的某个存储单元在一个较短的时间间隔内很可能又被访问。

空间局部性是指被访问的某个存储单元的邻近单元在一个较短的时间间隔内很可能也被访问。

出现程序访问的局部性特征的原因不难理解:

- 程序是由指令和数据组成的,指令在主存按顺序存放,其地址连续,循环程序段或子程序段通常被重复执行,因此,指令具有明显的访问局部化特征;

- 数据在主存一般也是连续存放,特别是数组元素,常常被按序重复访问,因此,数据也具有明显的访问局部化特征。

订阅专栏 解锁全文

订阅专栏 解锁全文

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?