第1章 第2章 逻辑函数及其简化

第4章 组合逻辑电路

一、中规模元器件

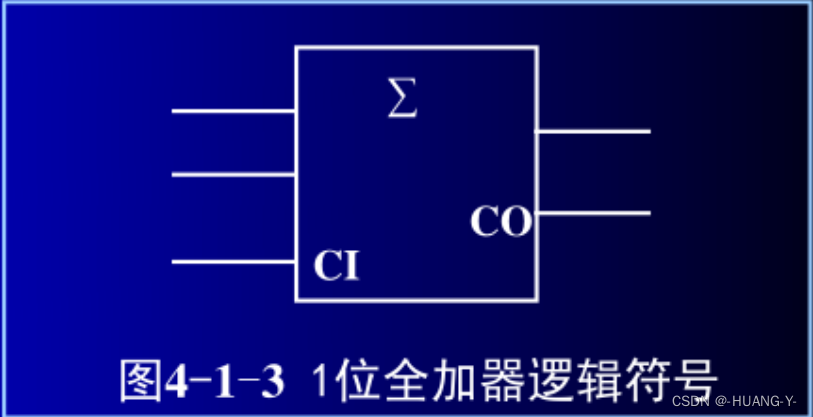

全加器

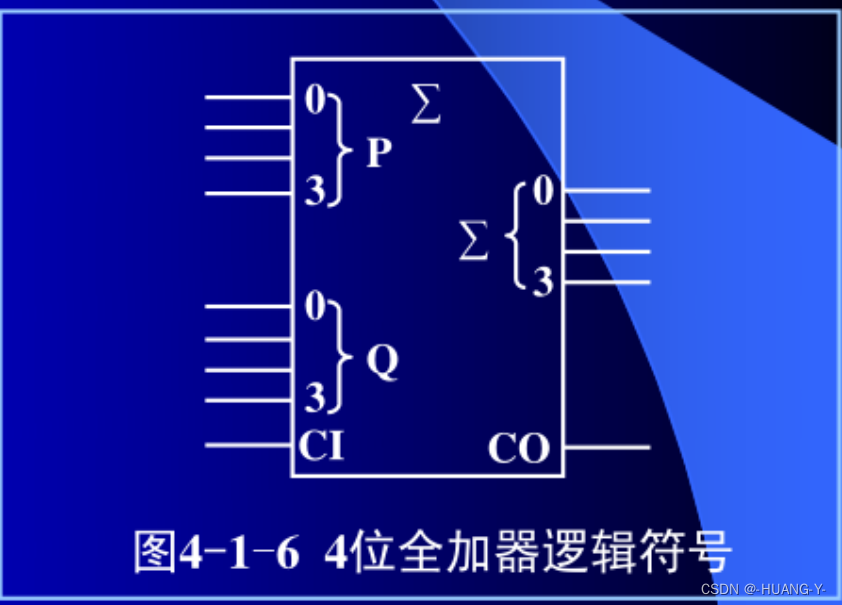

逻辑符号:

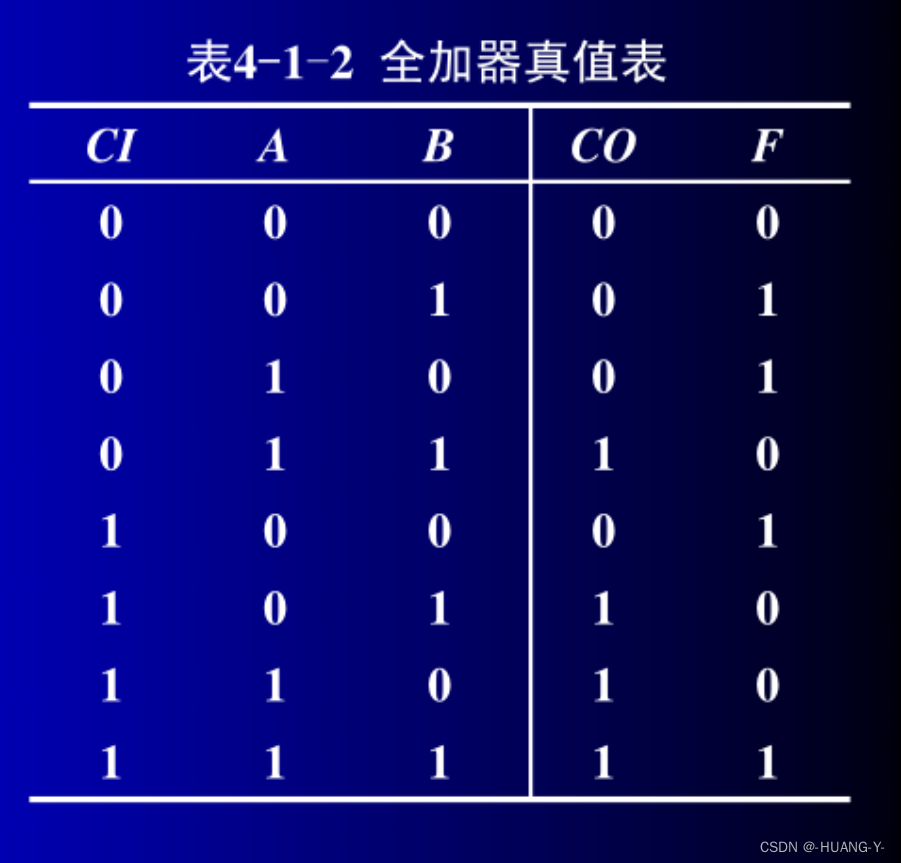

真值表:

CI为外界进位输入,CO为当前进位输出,F为本位相加之和。

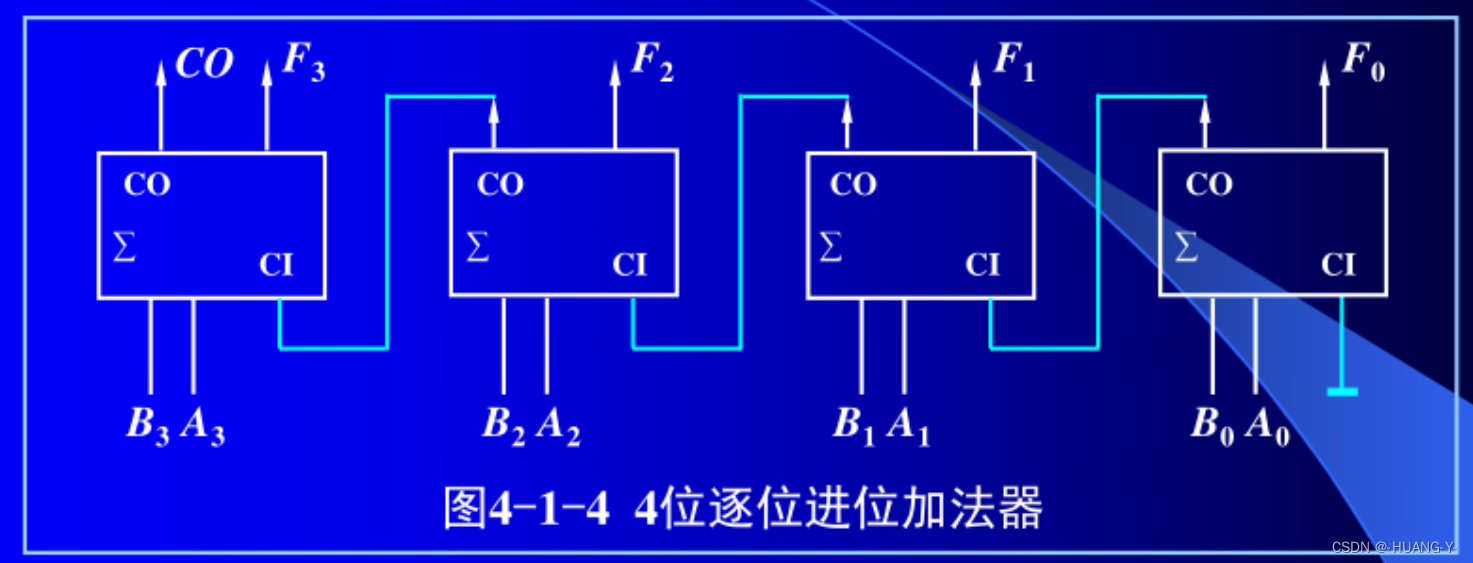

串行进位加法器:

超前进位加法器:

编码器

定义:用二进制数(输出)表示十进制数(输入)。输入端子N与输出端子n的关系: 。

。

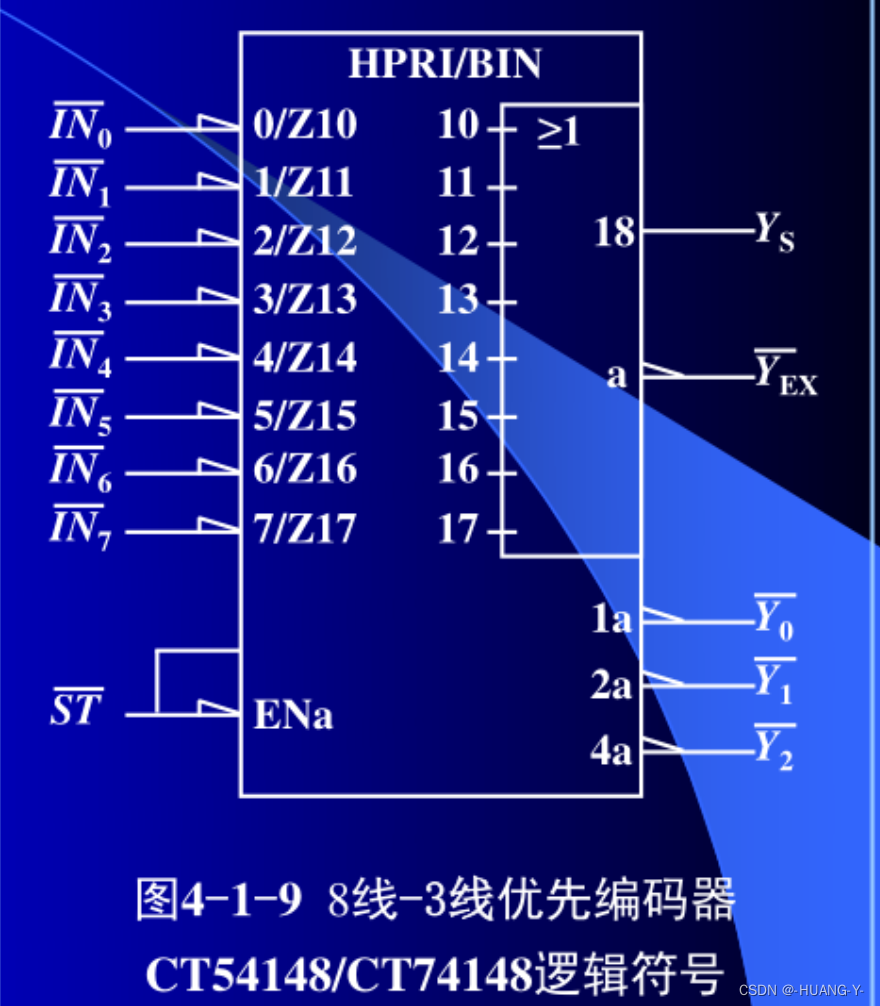

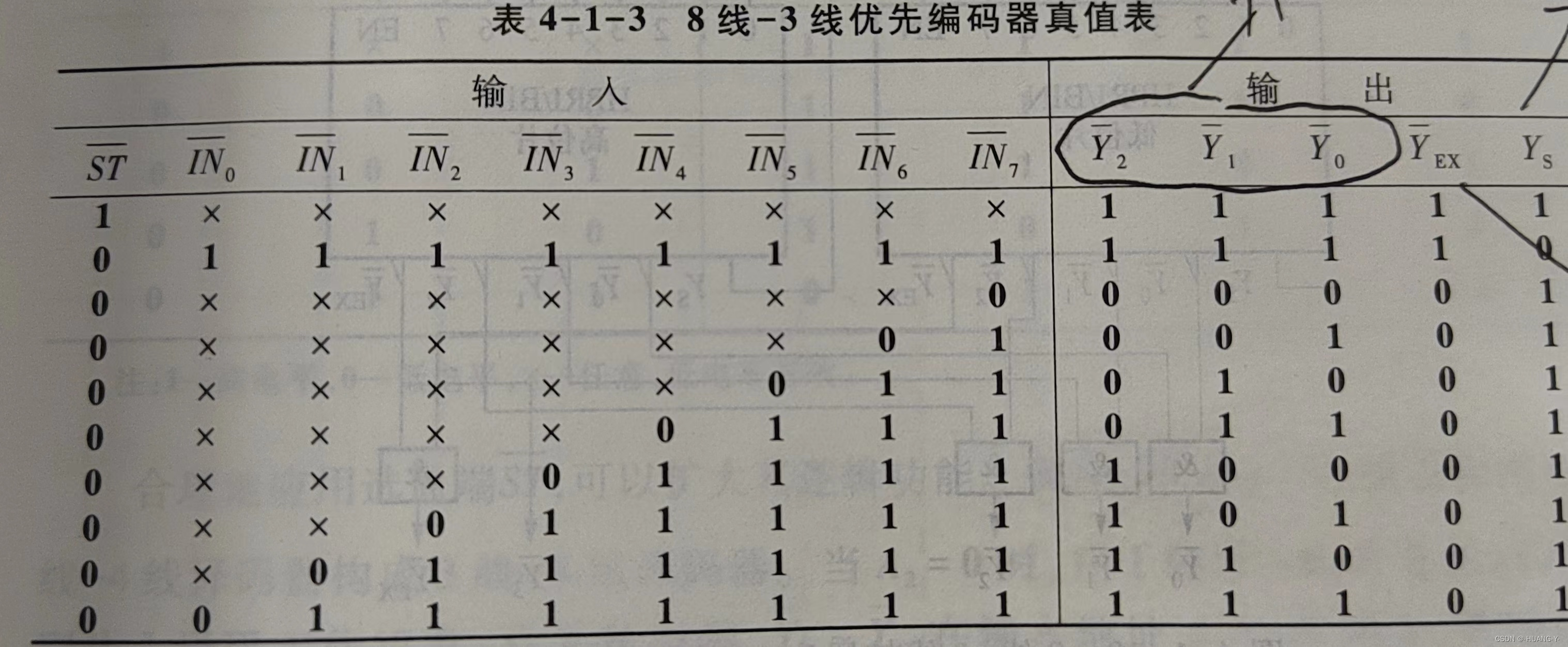

8线-3线优先编码器:

真值表:

提示:优先级高位到低位,以01为例,无论前面输入为何,输出01。

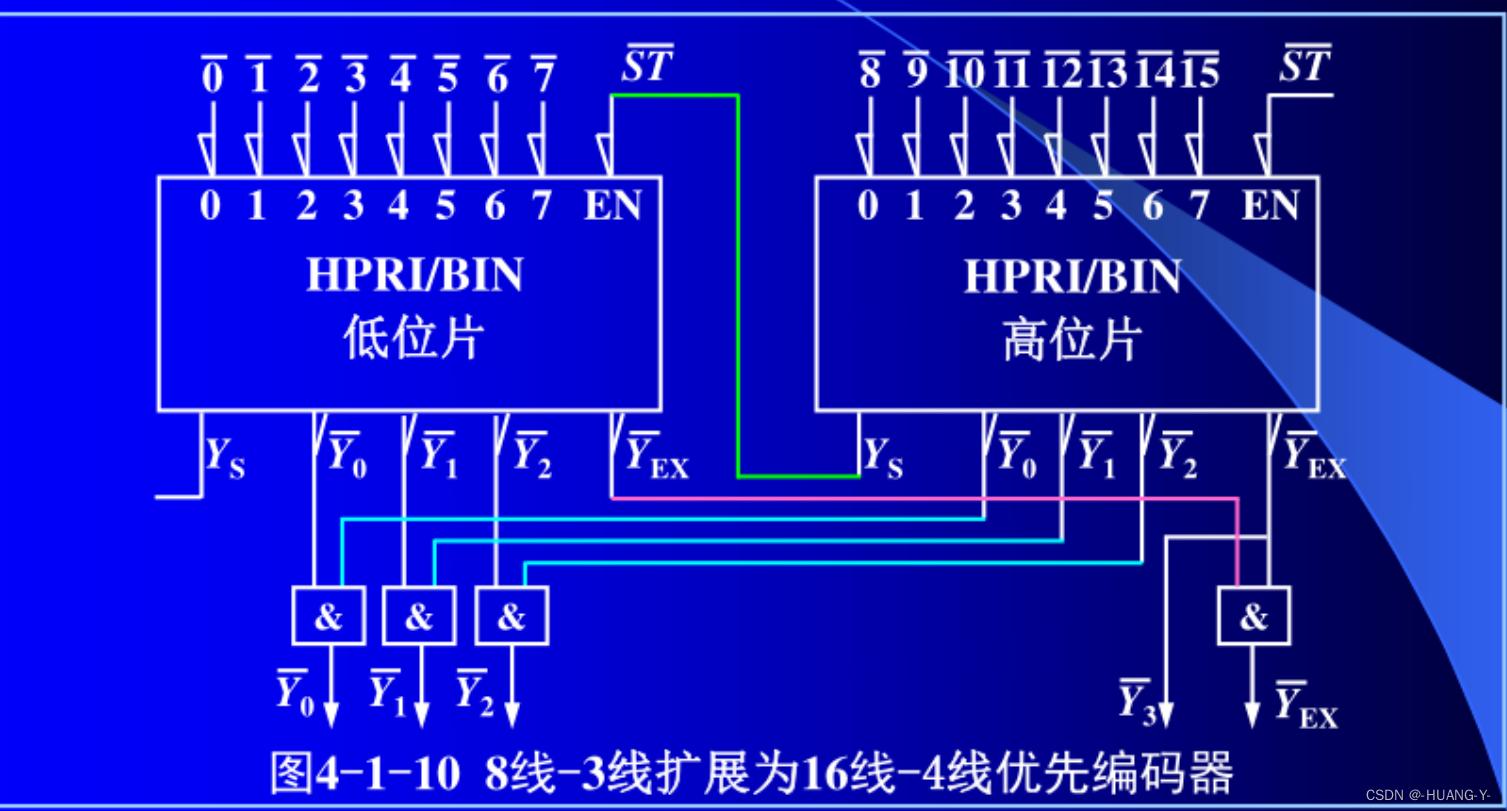

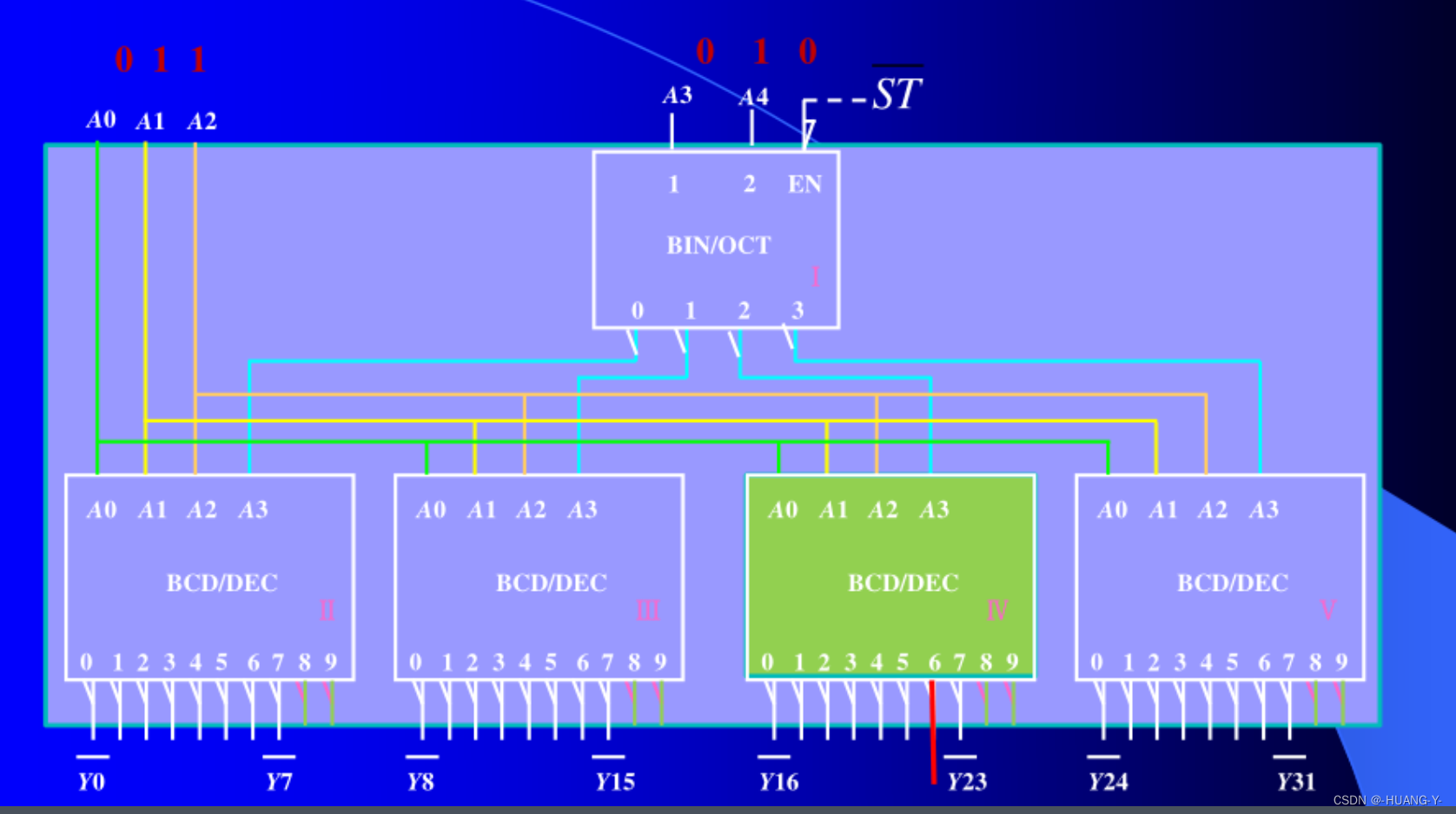

8线-3线优先编码器扩展为16线-4线优先编码器:

关键 :

1、输出低电平有效与门合二为一,输出高点平有效或门合二为一;

2、低位片的ST与高位片YS相连;

3、两片YES与门相连输出;

4、高位片YES直接输出,作为最高位,区分高、低位输出;

译码器

定义:二进制(输入)翻译为十进制(输出)。输入n与输出N满足: 。

。

译码器输出与最小项的关系:

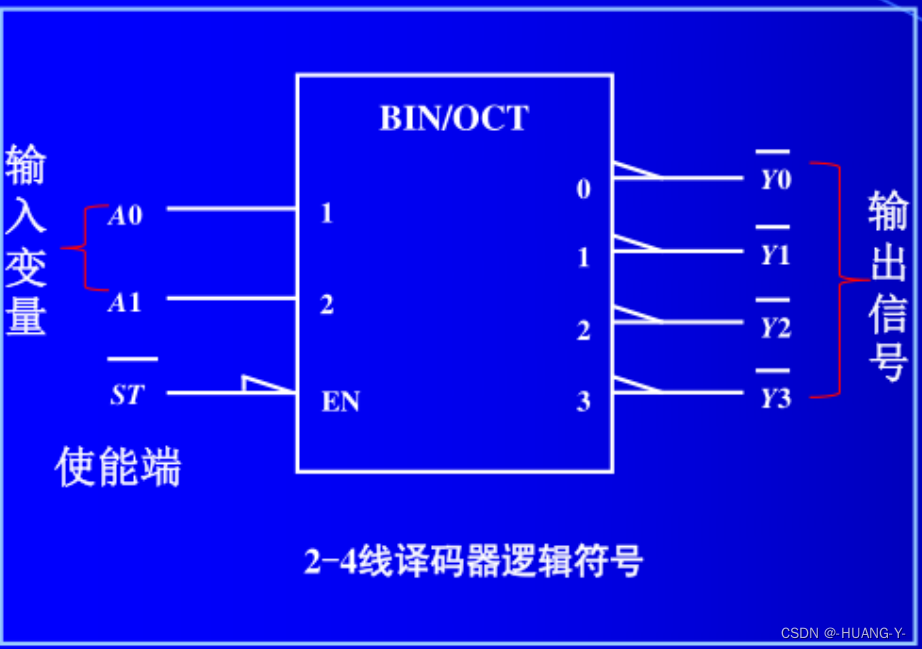

2-4线译码器:

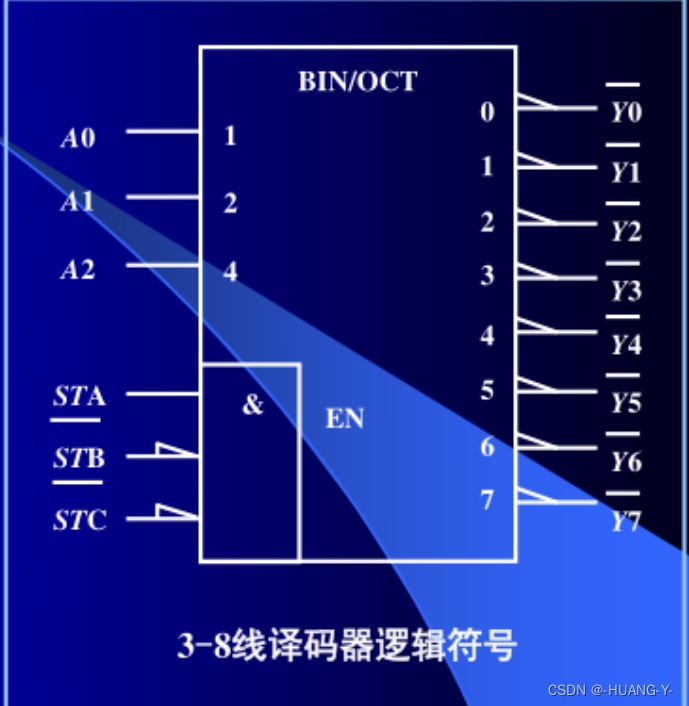

3-8线译码器:

三个选通信号——便于扩展。

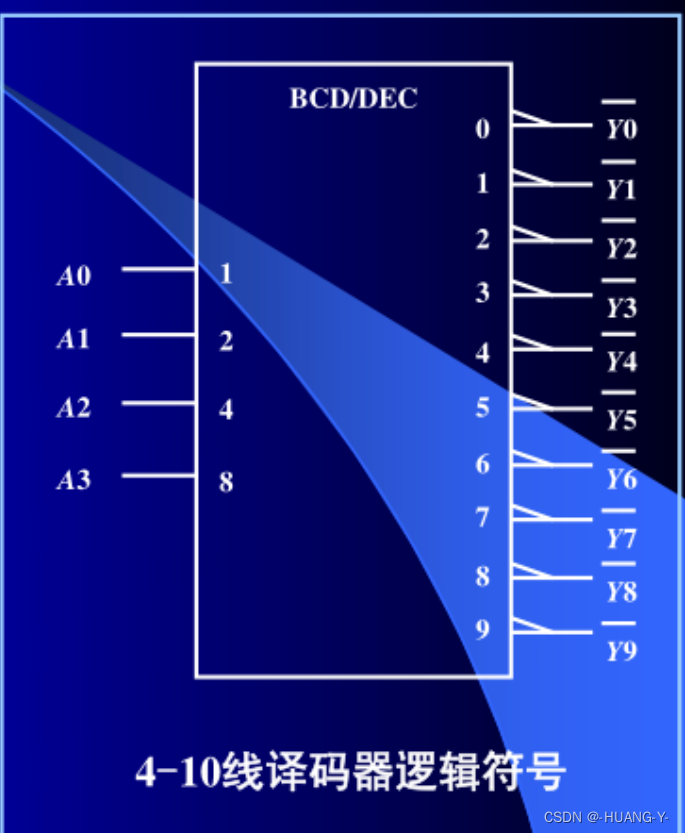

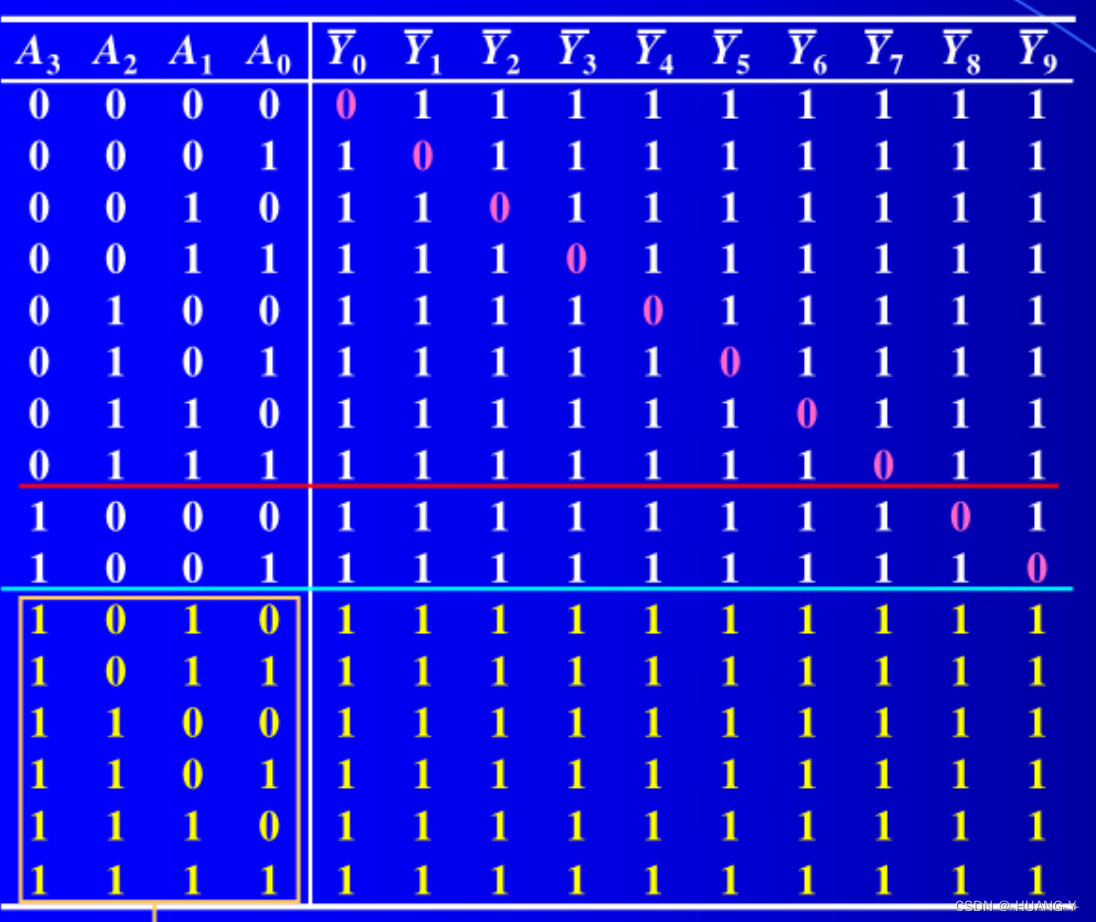

4-10线译码器:

真值表:

A3可改为使能端,将4-10线译码器改为3-8线译码器。

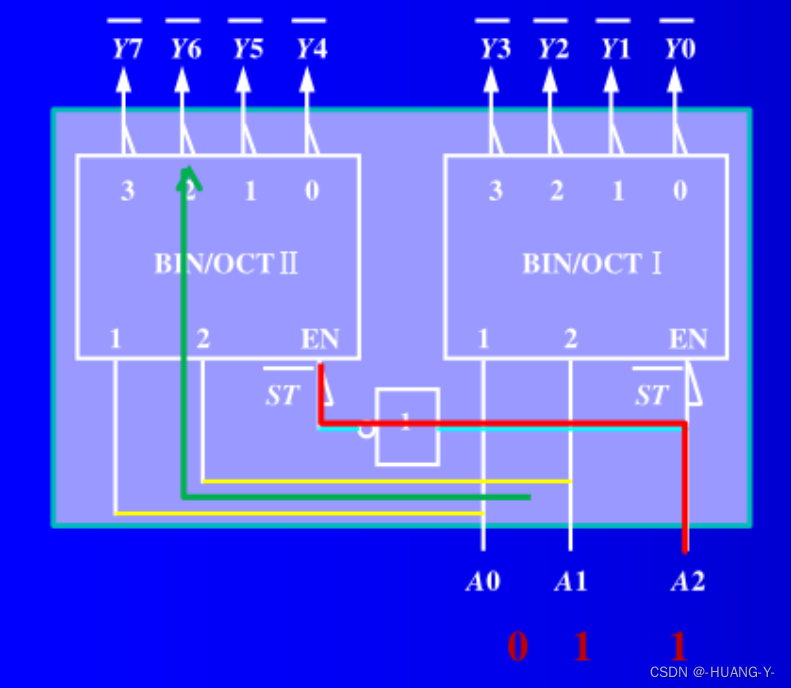

2-4线译码器扩展为3-8线译码器:

注:一般来说,新增输入端为最高位,且是原芯片的使能端。

2-4线译码器和 4-10线译码器扩展成5-32线译码器:

应用:地址译码,数据分配器。

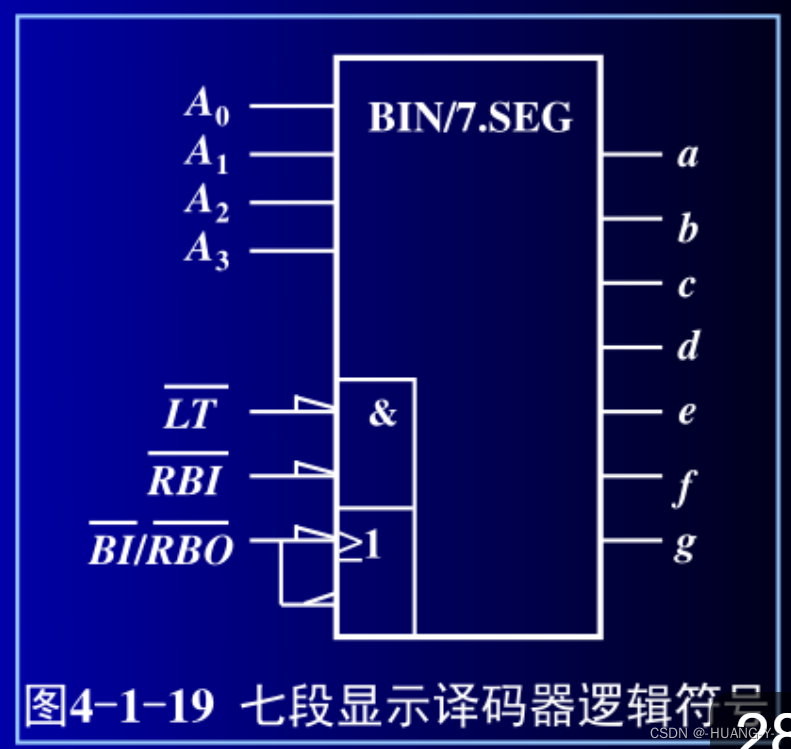

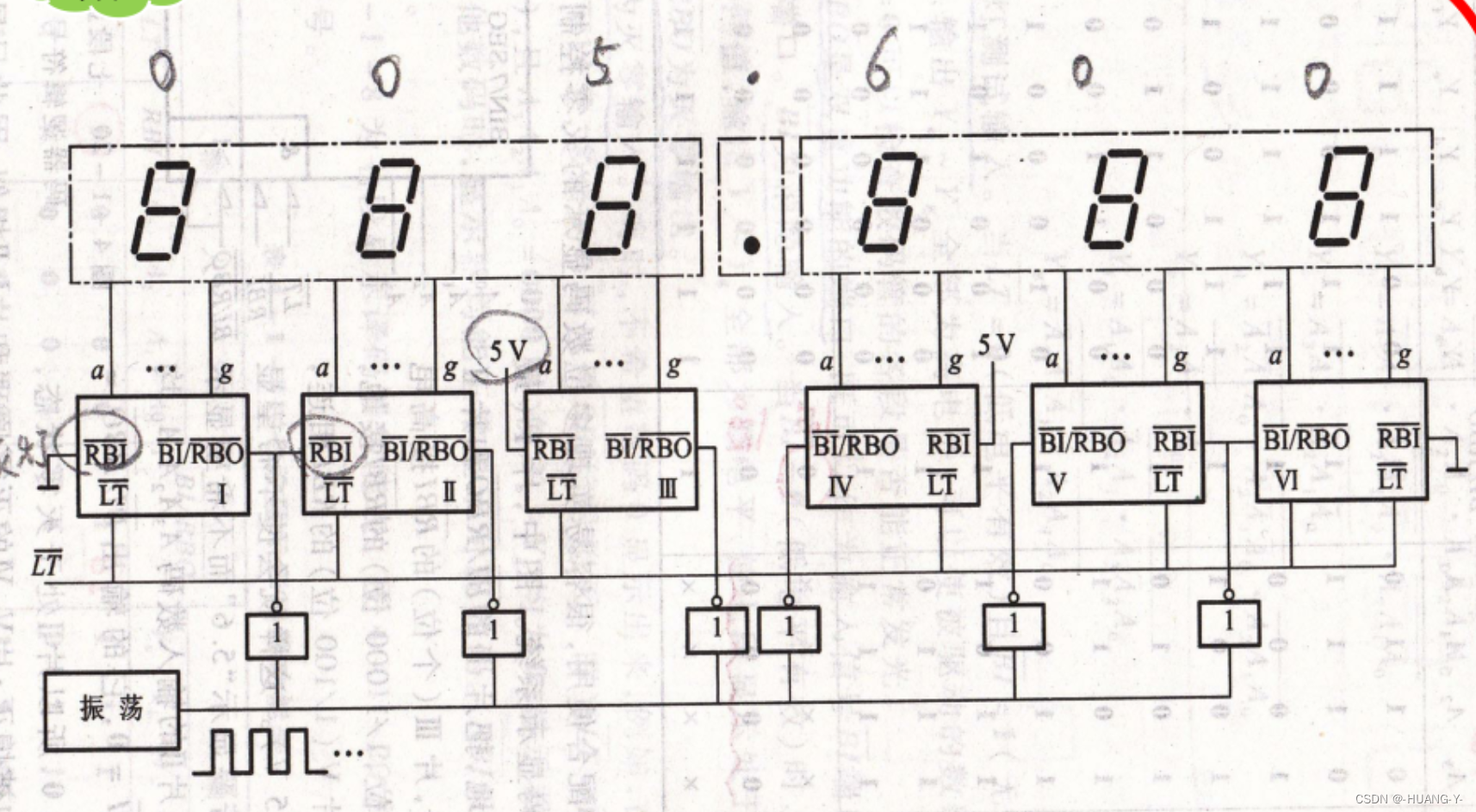

七段显示译码器:

LT灯测试输入,使灯全亮;RBI灭零输入;BI消隐输入,使灯熄灭;RBO灭零输出。

灭零实际应用:

注:灯测试接1。

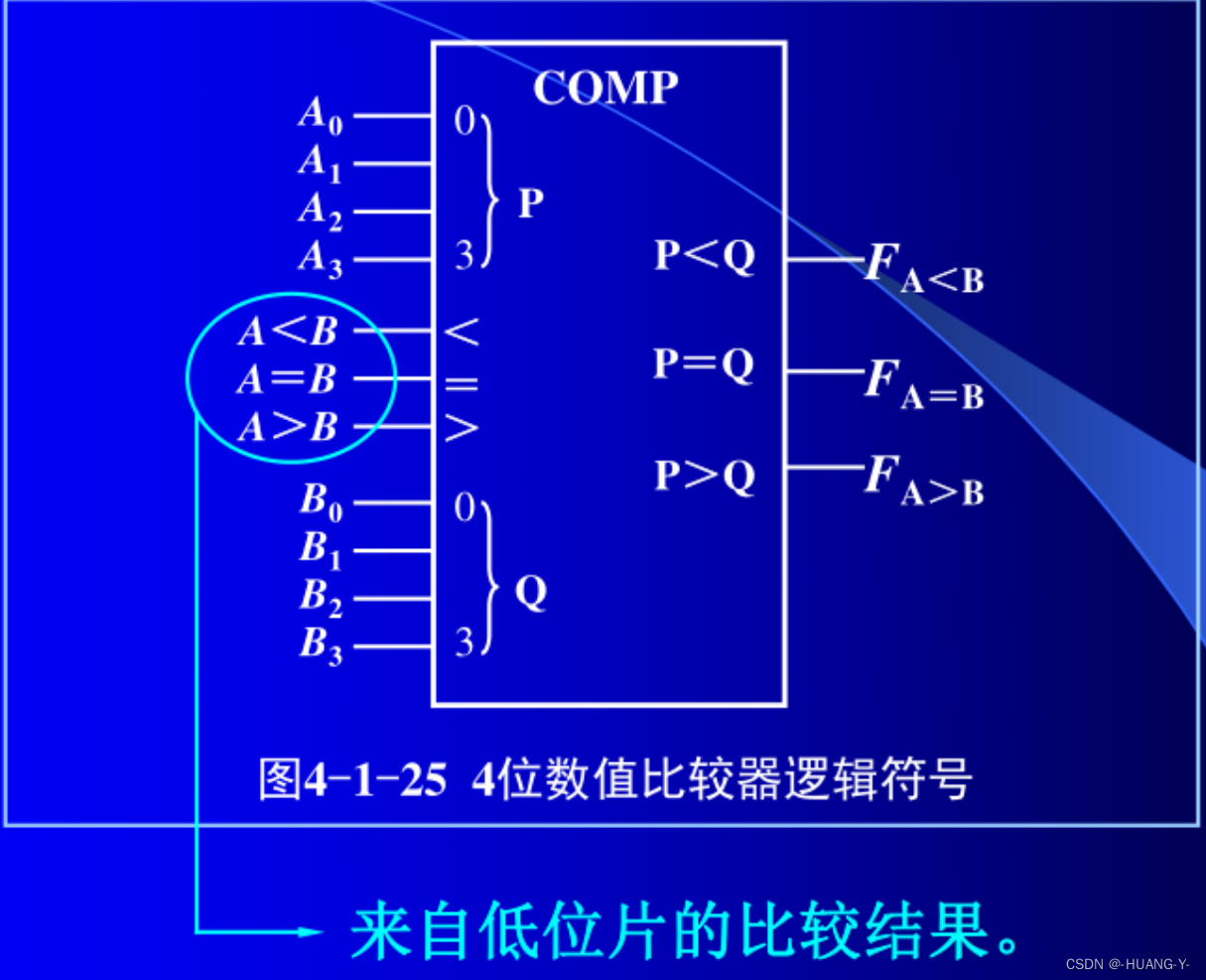

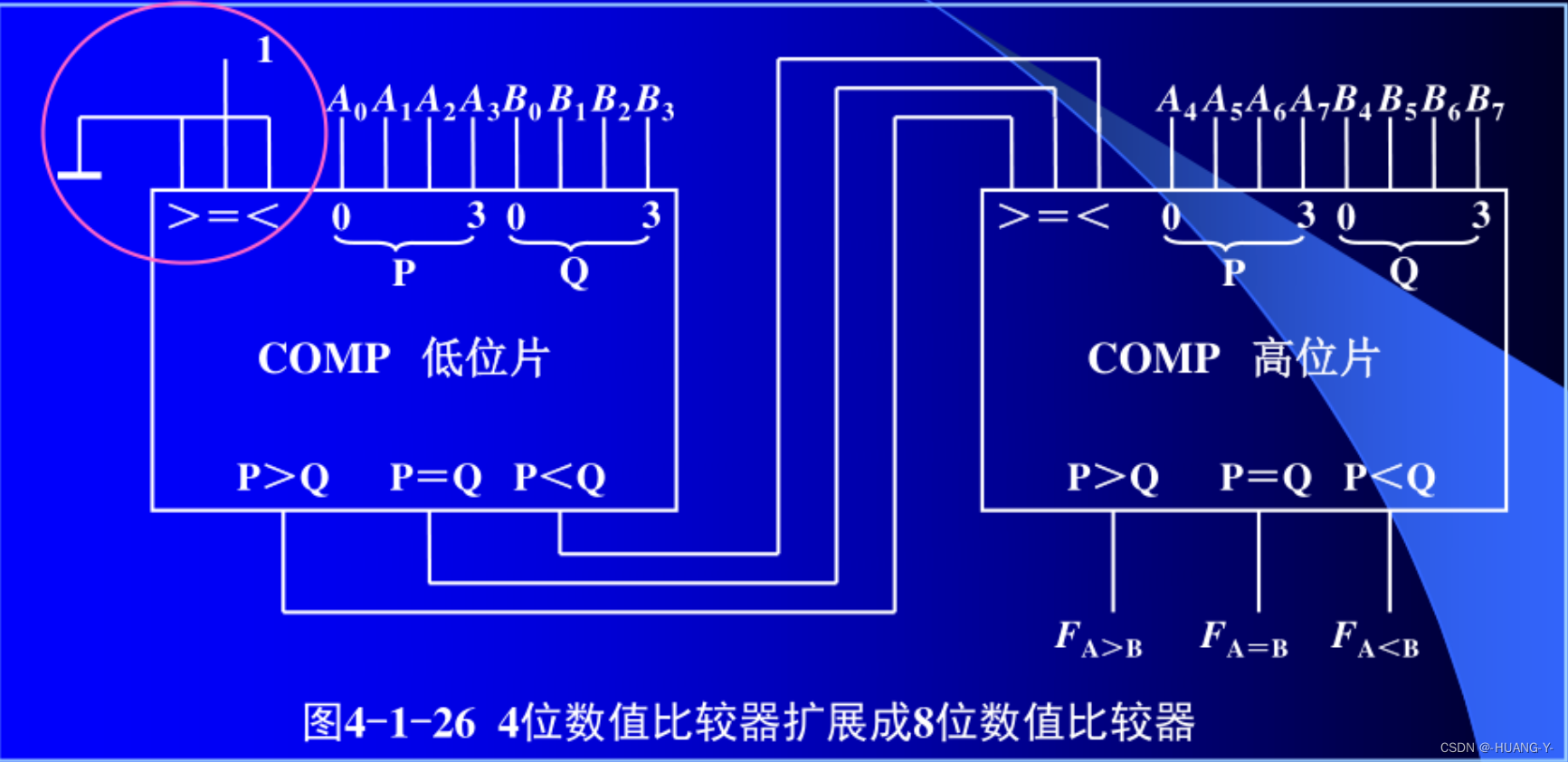

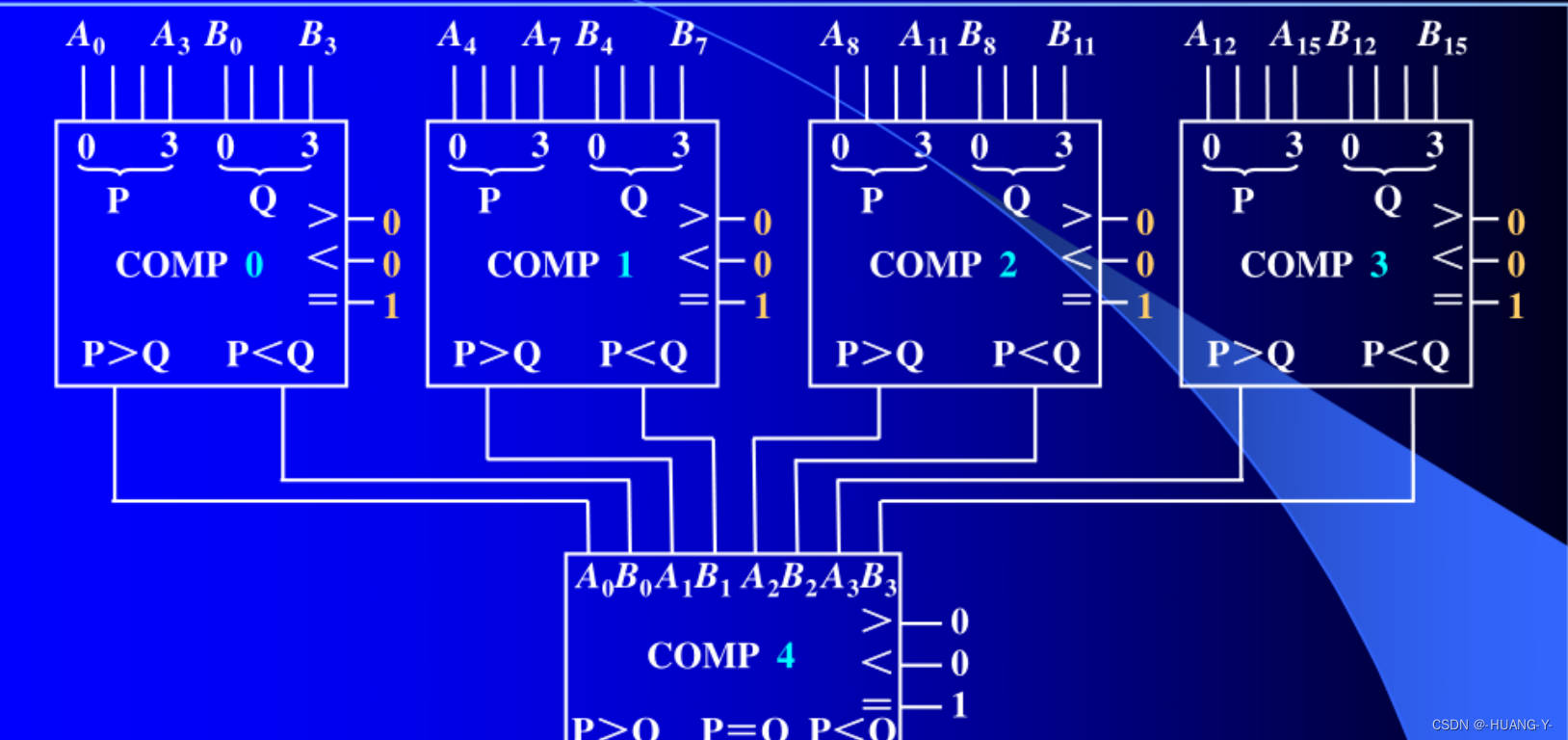

数值比较器

4位数值比较器:

注:

1、在单独使用或作为最低位片使用时,A>B,A<B接0,A=B接1。

2、从高位开始比,若高位有大小差异,后续不比较。

级联扩展:

并联扩展:

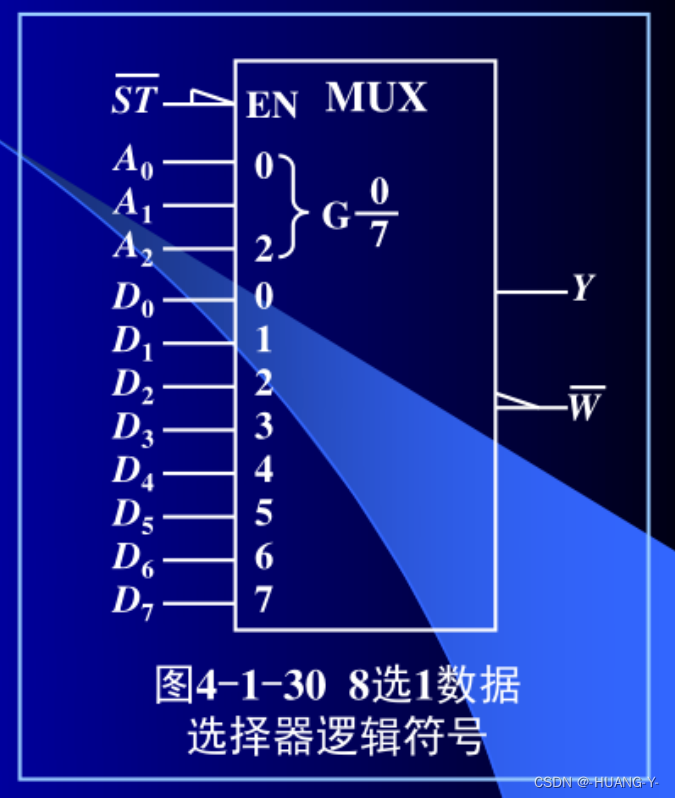

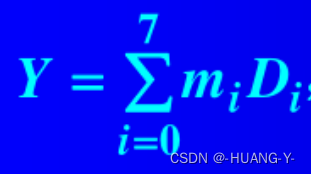

数据选择器

8选1数据选择器:

数据选择器满足:

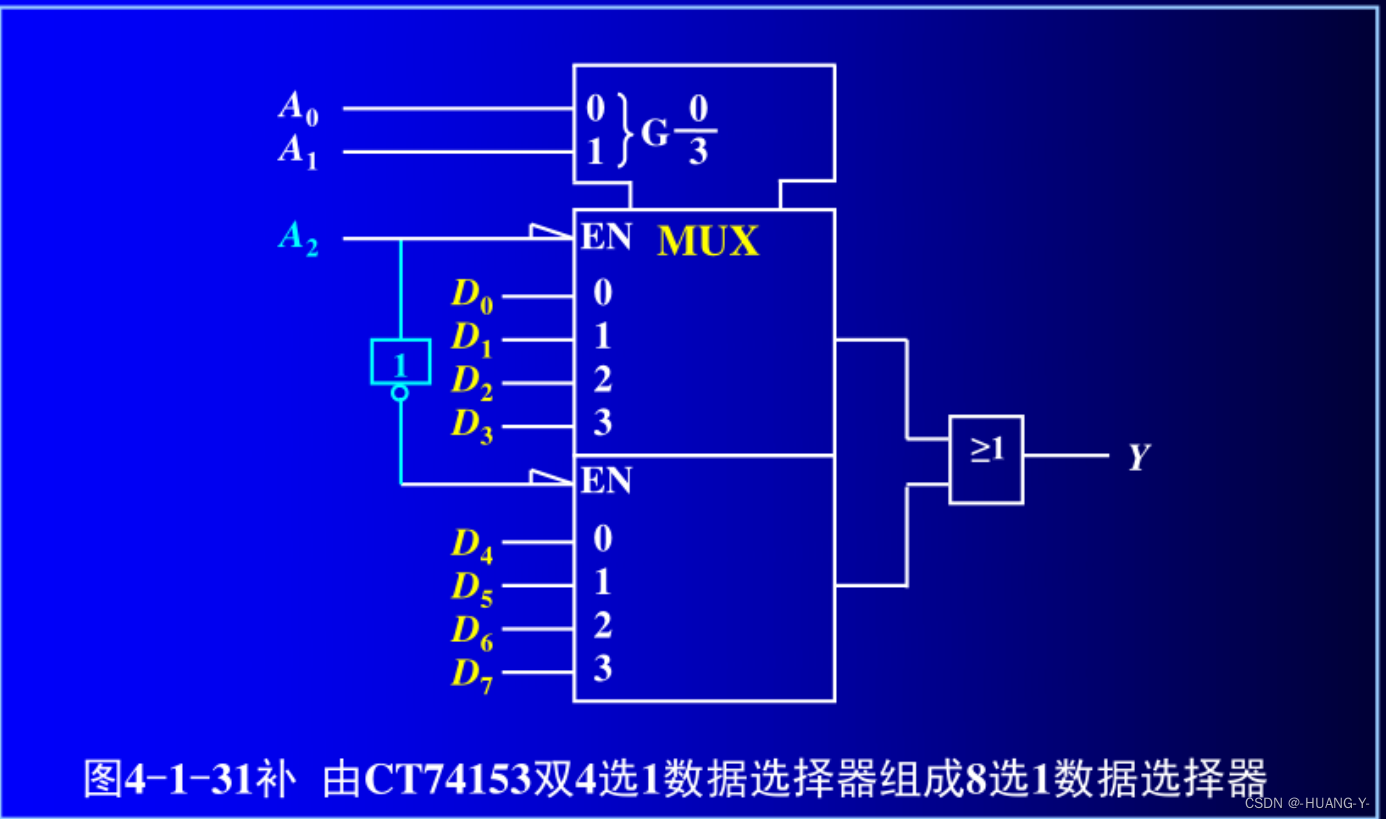

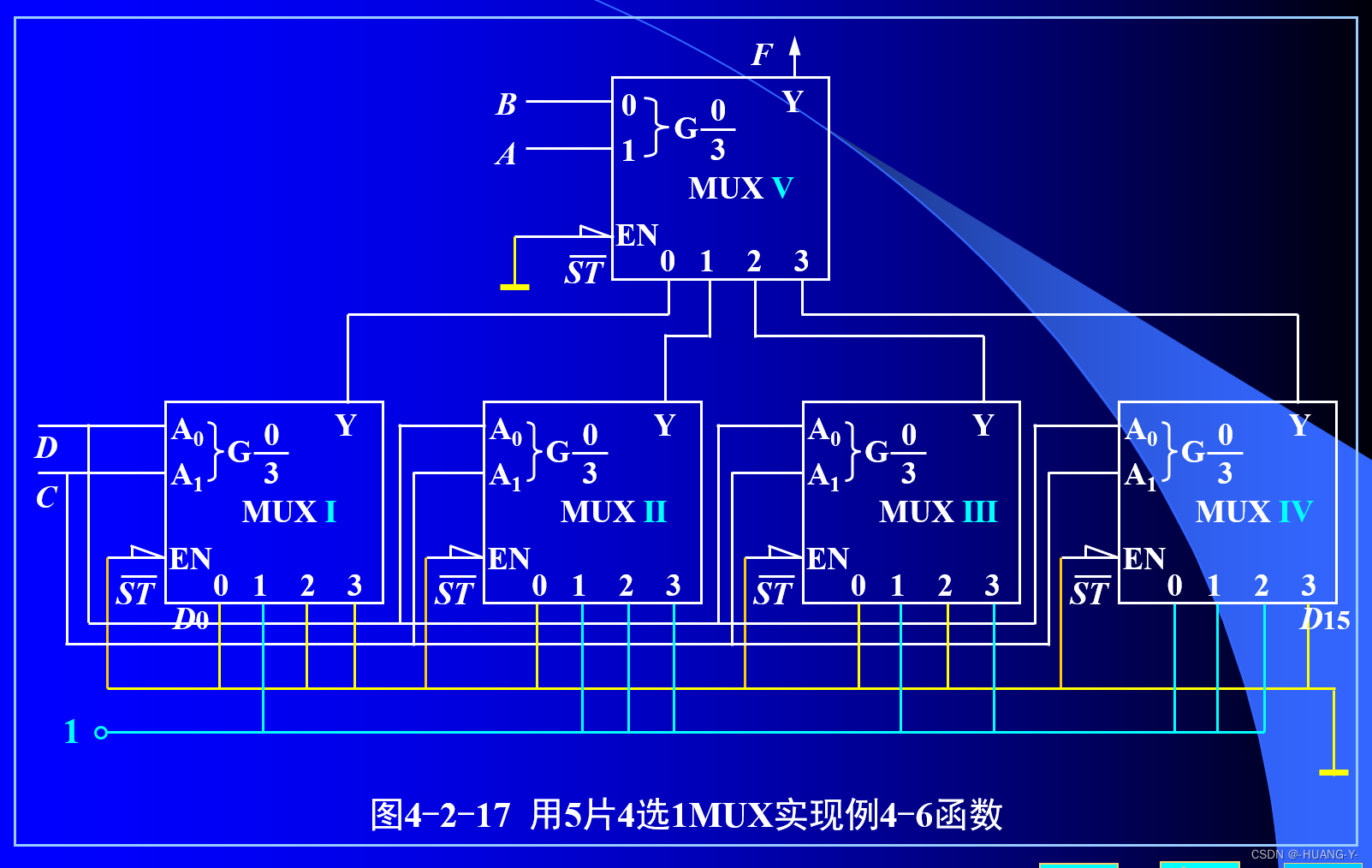

双4选1改为8选1:

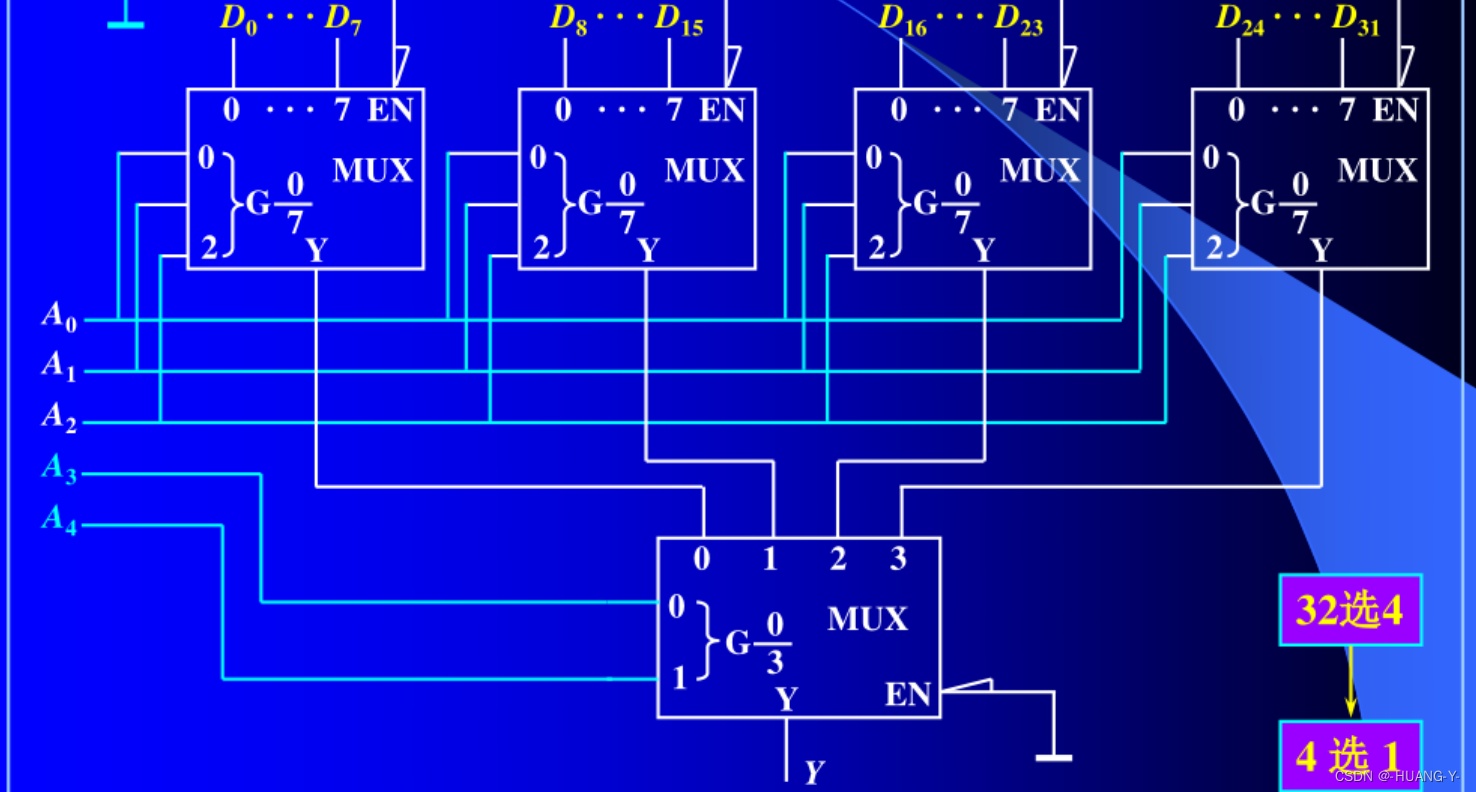

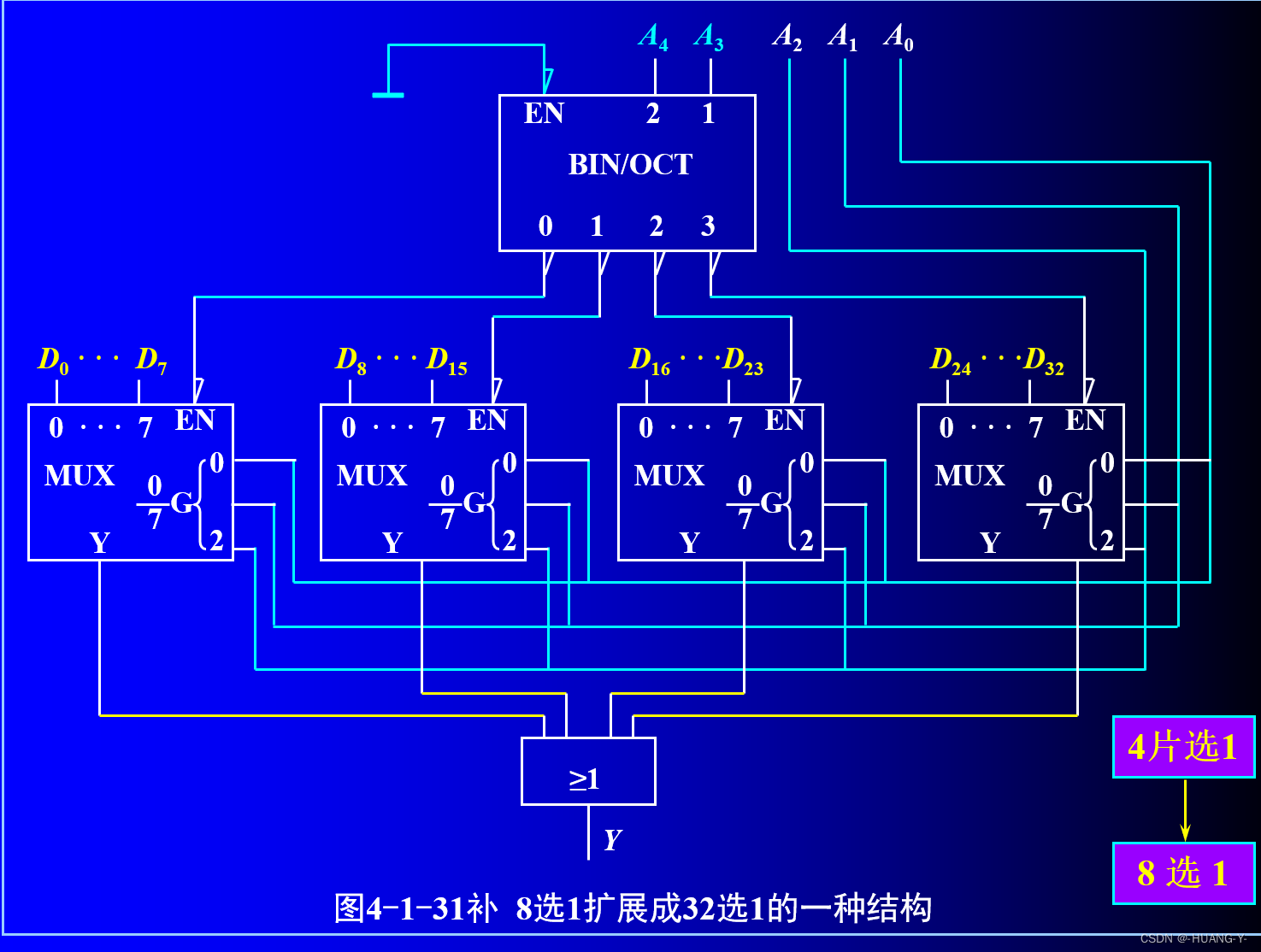

四片8选1改为32选1:

1、四片8选1都有效,由4选1控制传输哪个8选1:

2、用一片4选1控制四片8选1使能端:

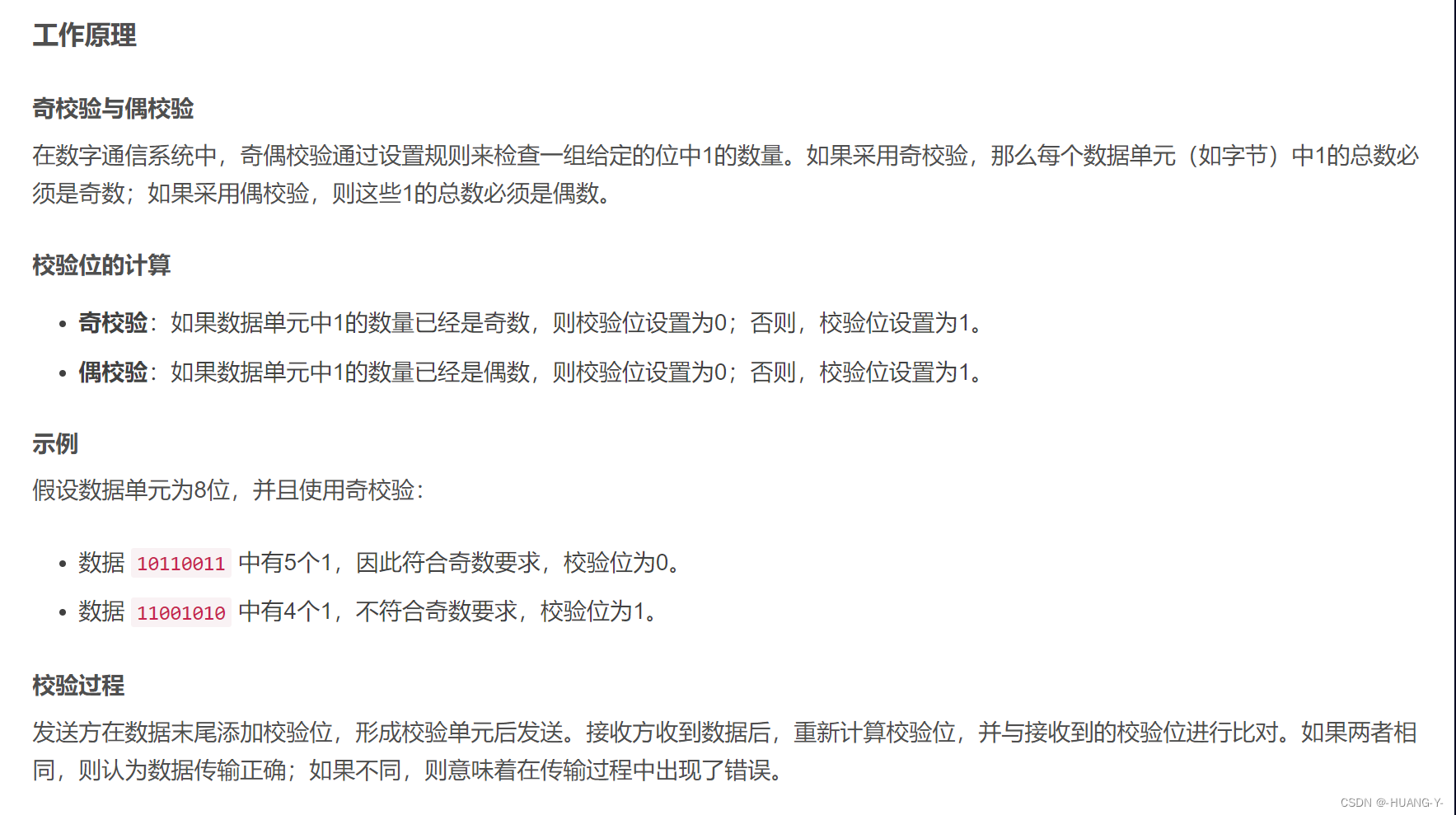

奇偶校验:

二、小规模集成器件组合逻辑设计

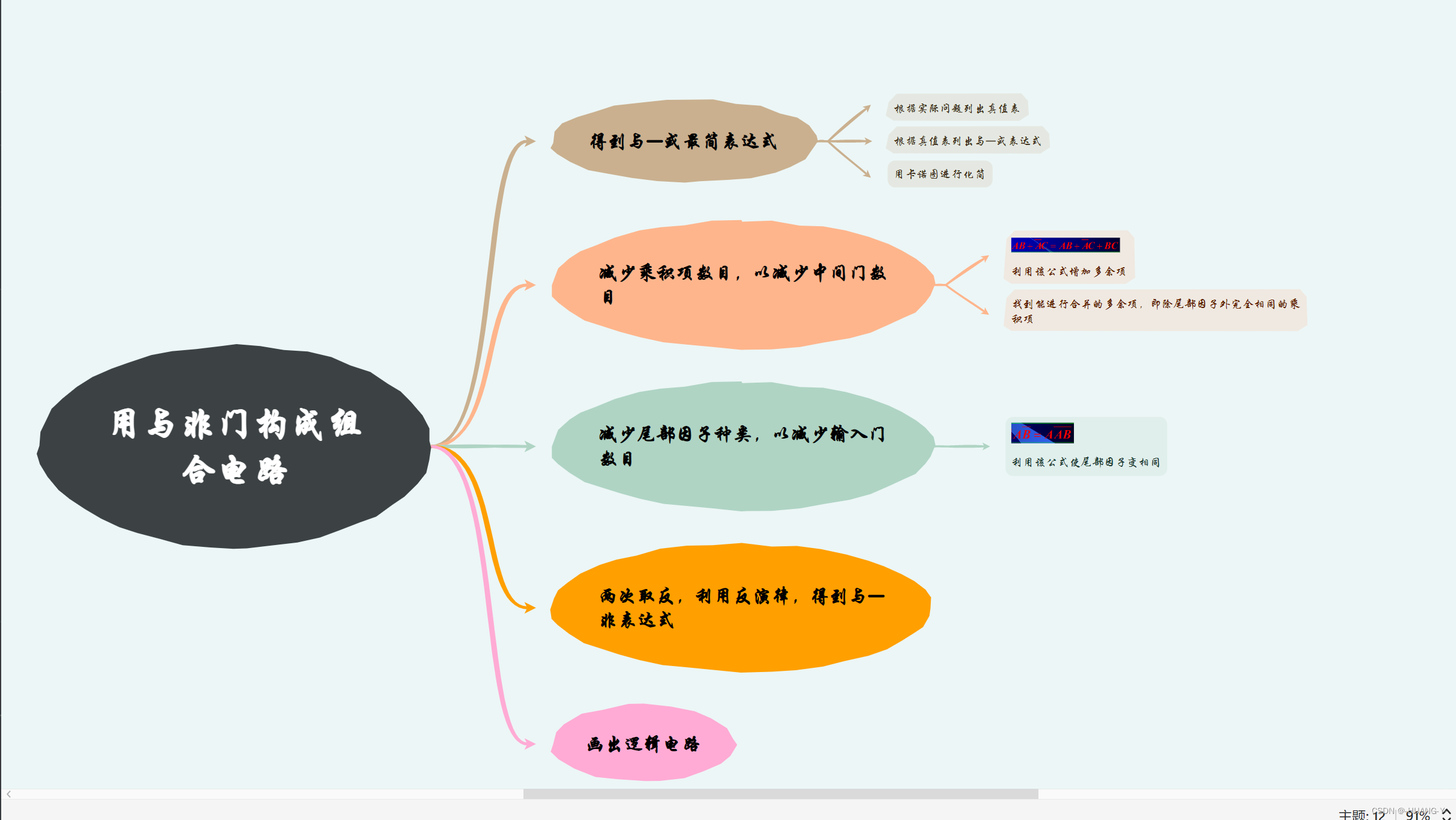

用与非门构成组合电路

http://t.csdnimg.cn/OBnR6 与非门构成其他逻辑门电路

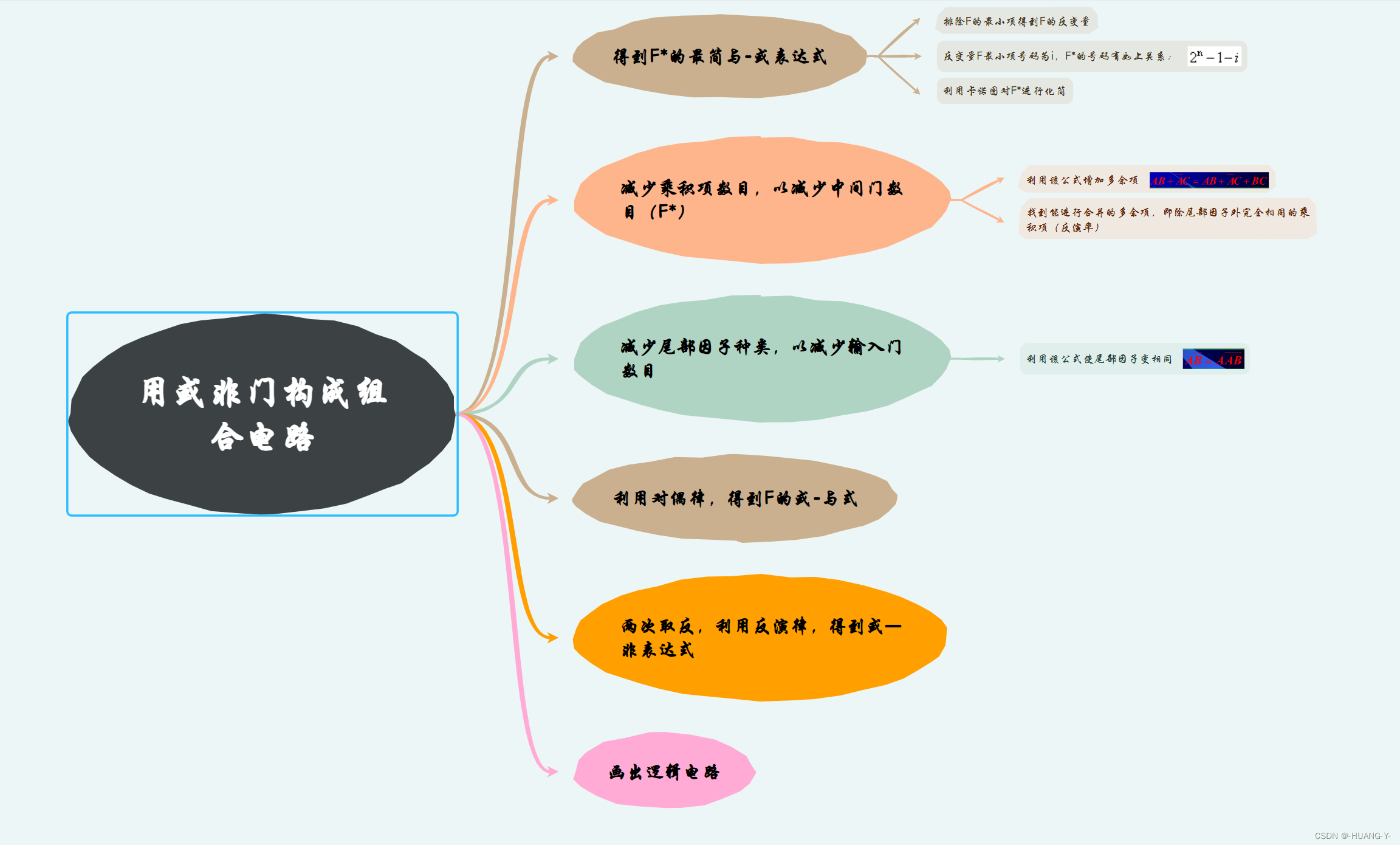

用或非门构成组合电路

三、中规模集成器件组合逻辑设计

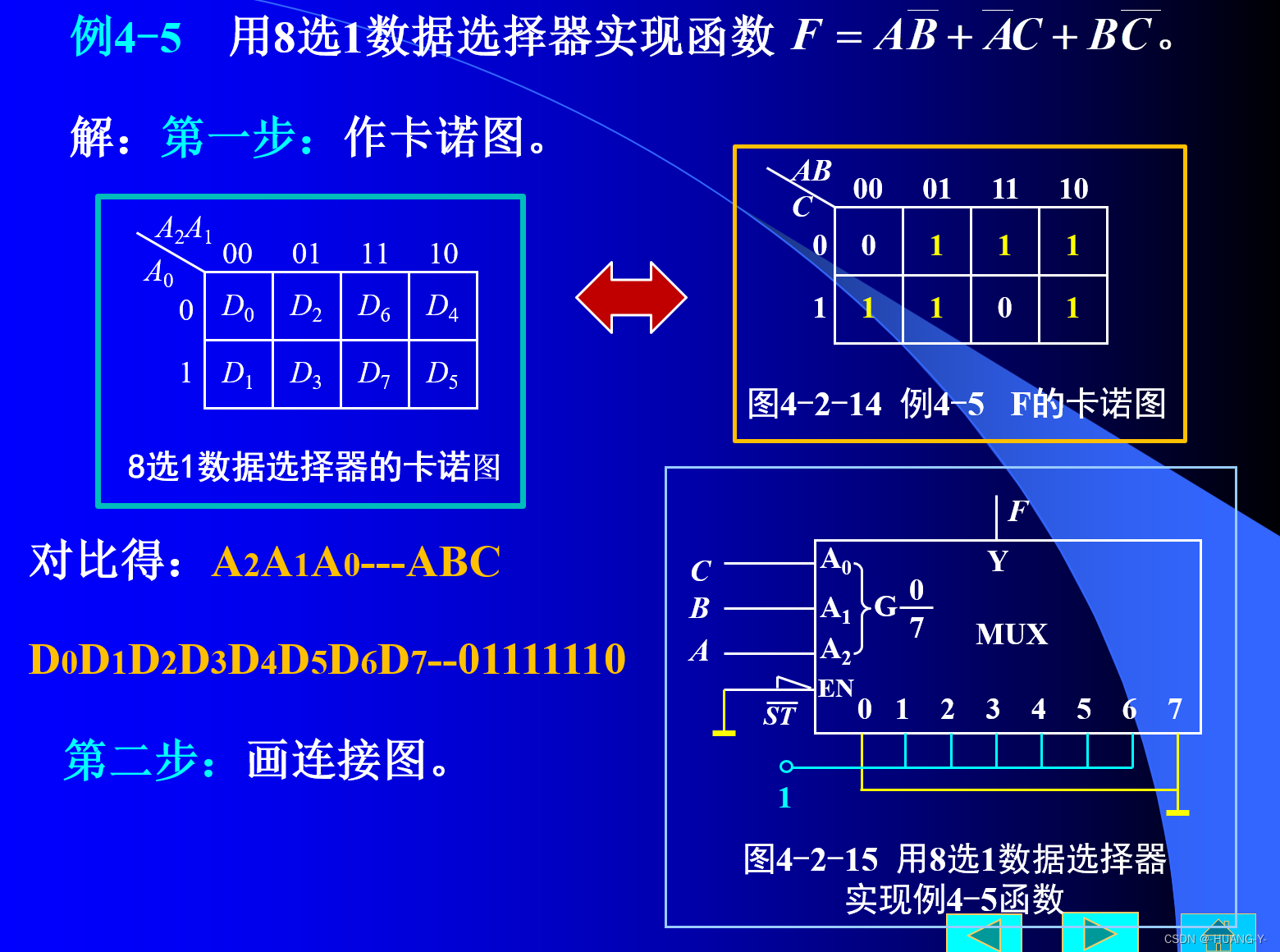

1、用具有n个地址输入端的数据选择器实现n变量的逻辑函数

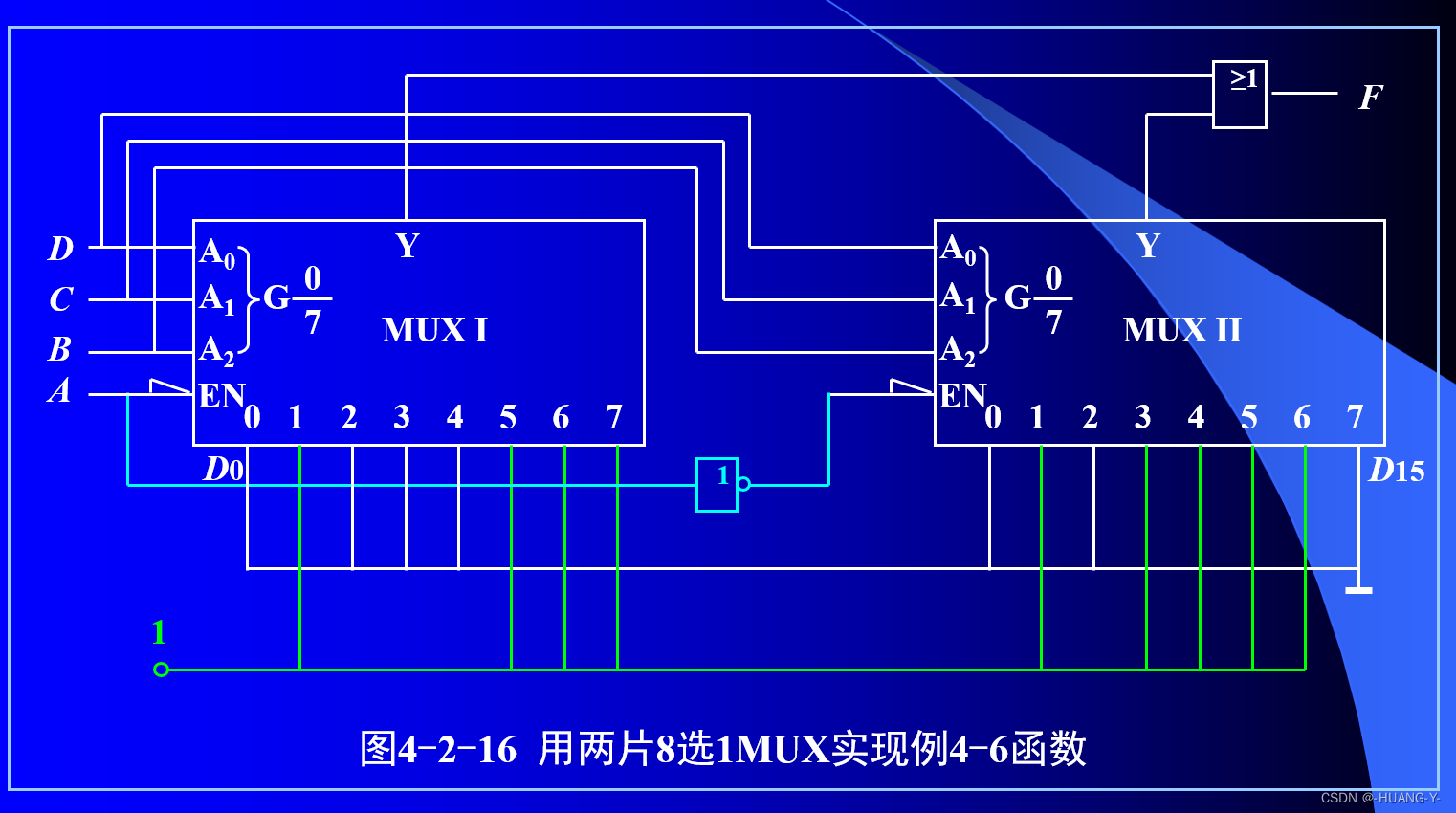

2、用具有n个地址输入端的数据选择器实现m变量的逻辑函数(m>n)

扩展法:

以n=3,m=4为例

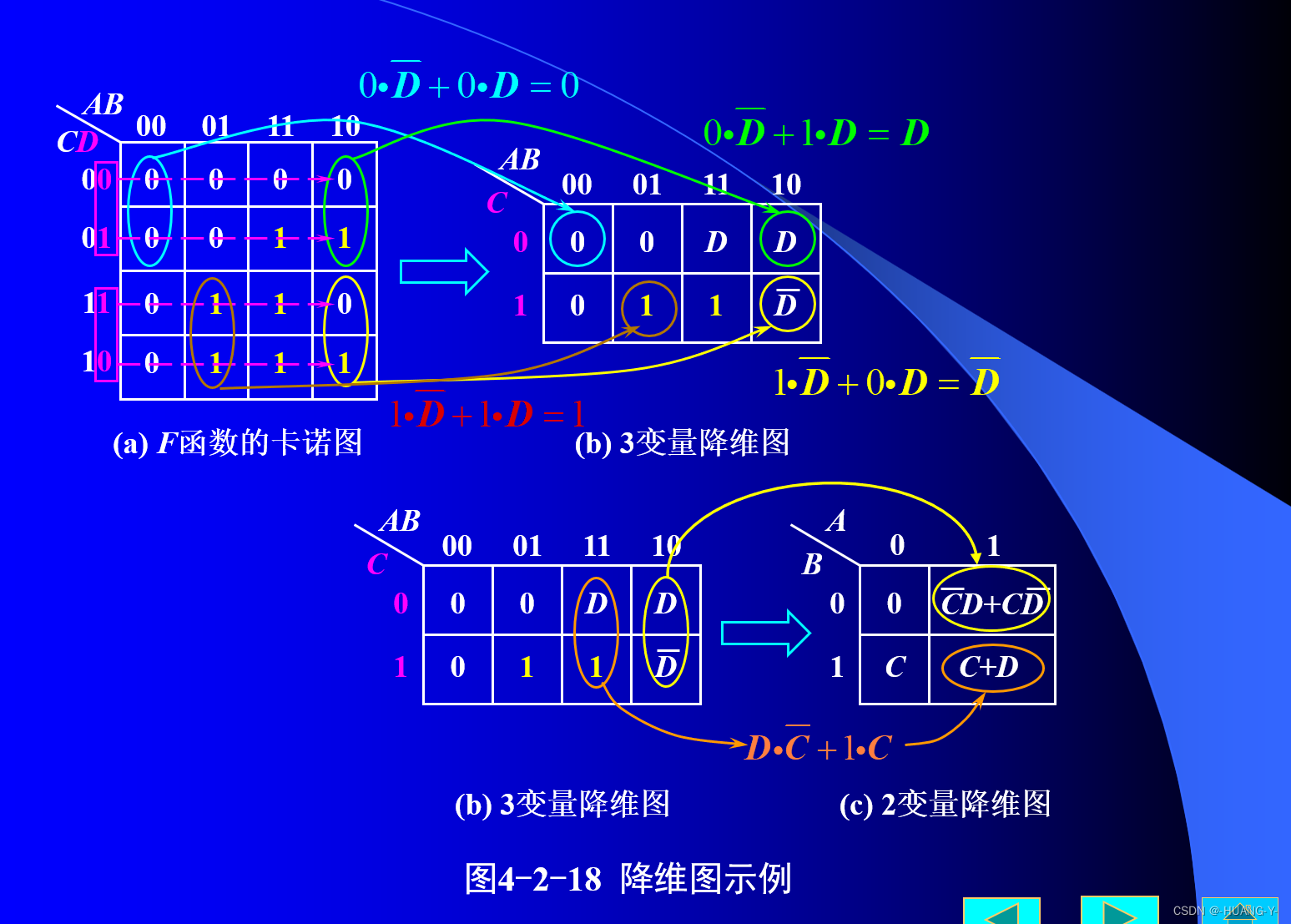

降维图法:

m降到n,再按第一种情况解决。

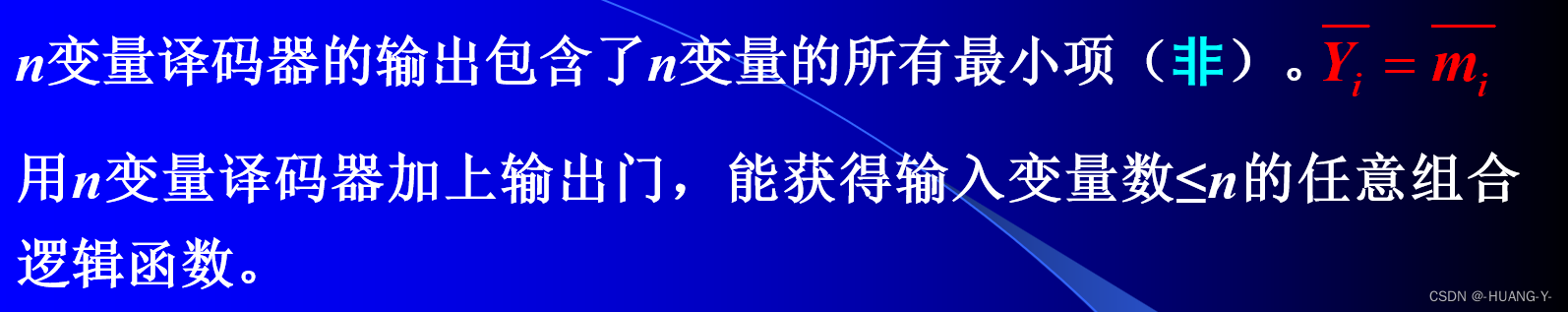

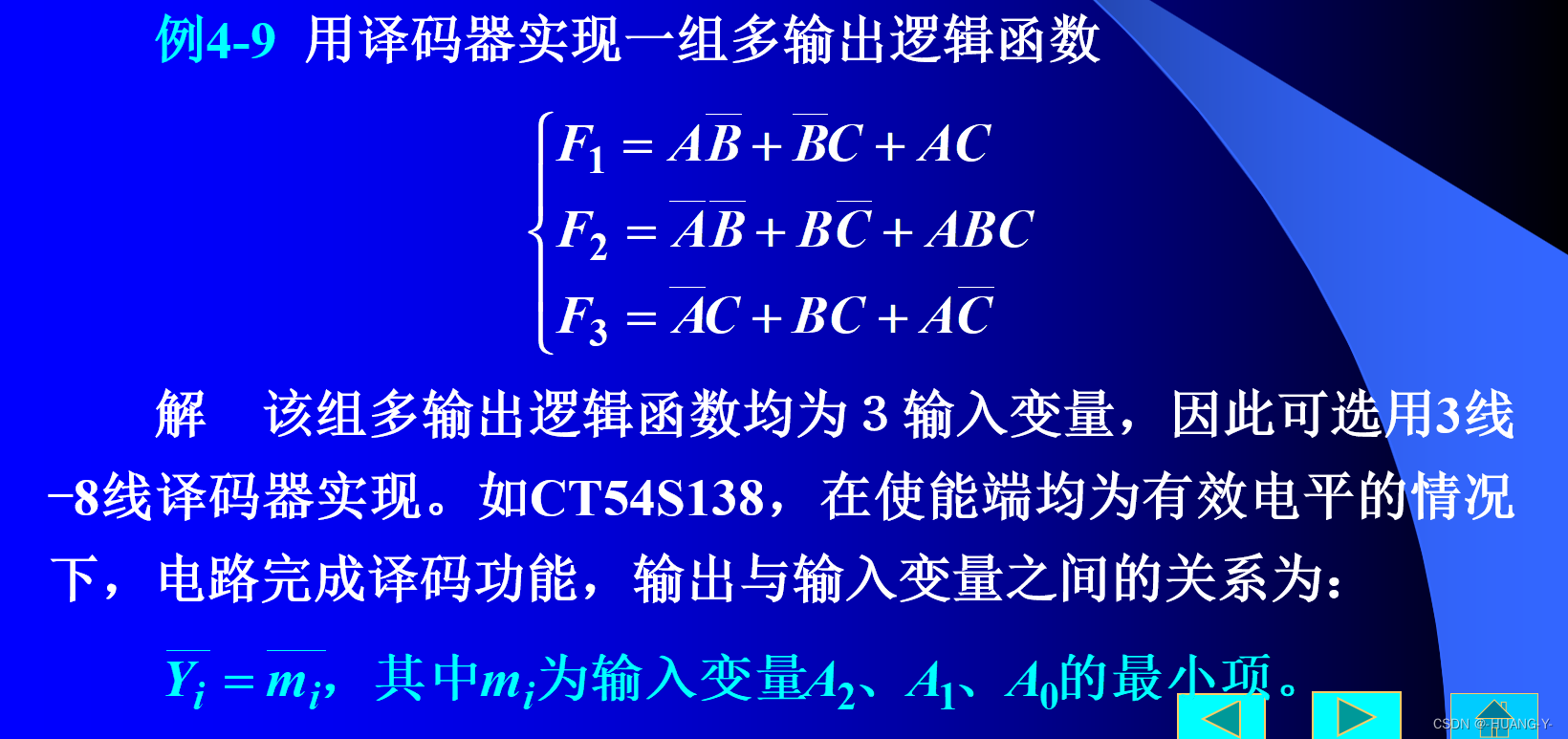

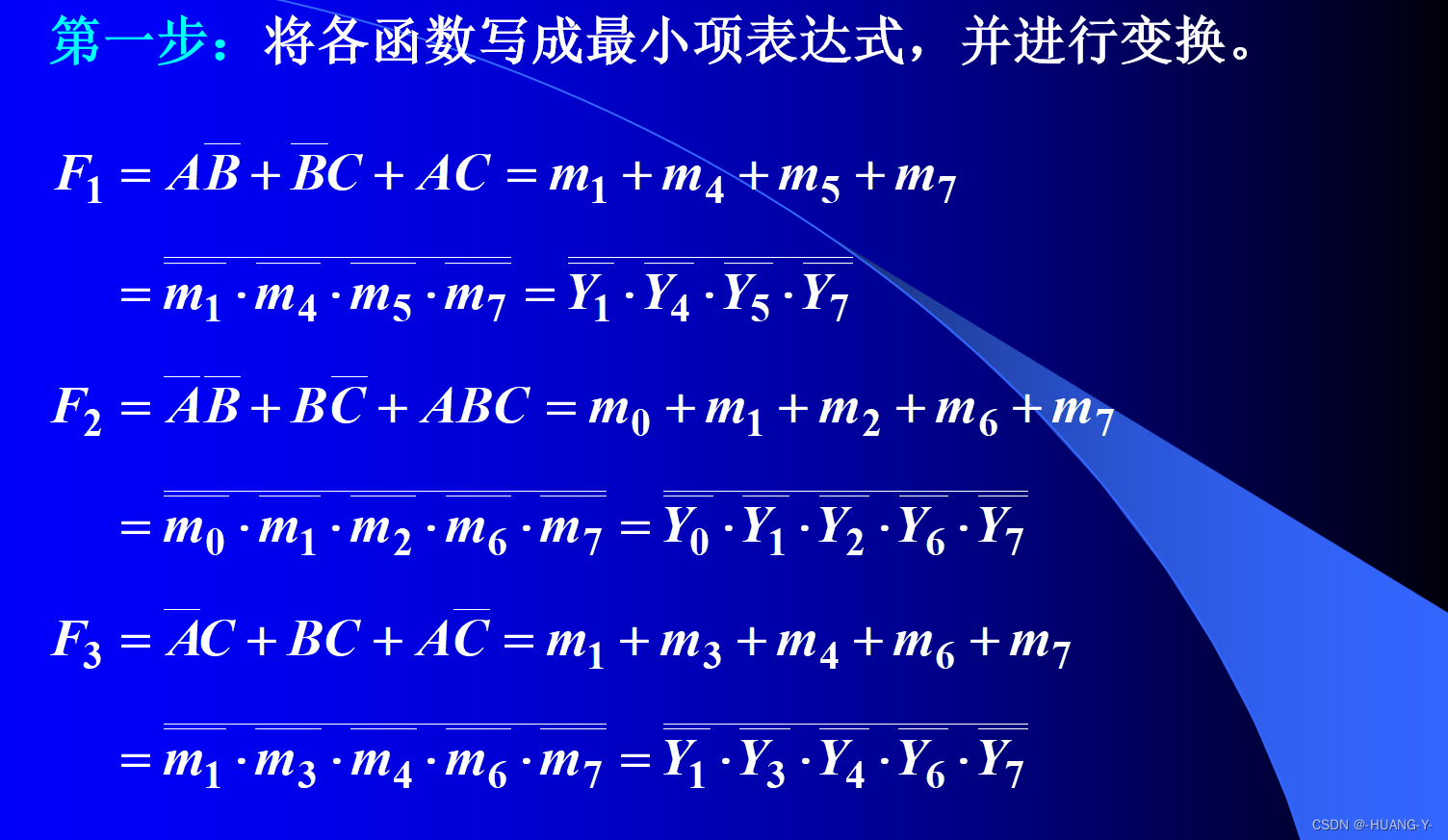

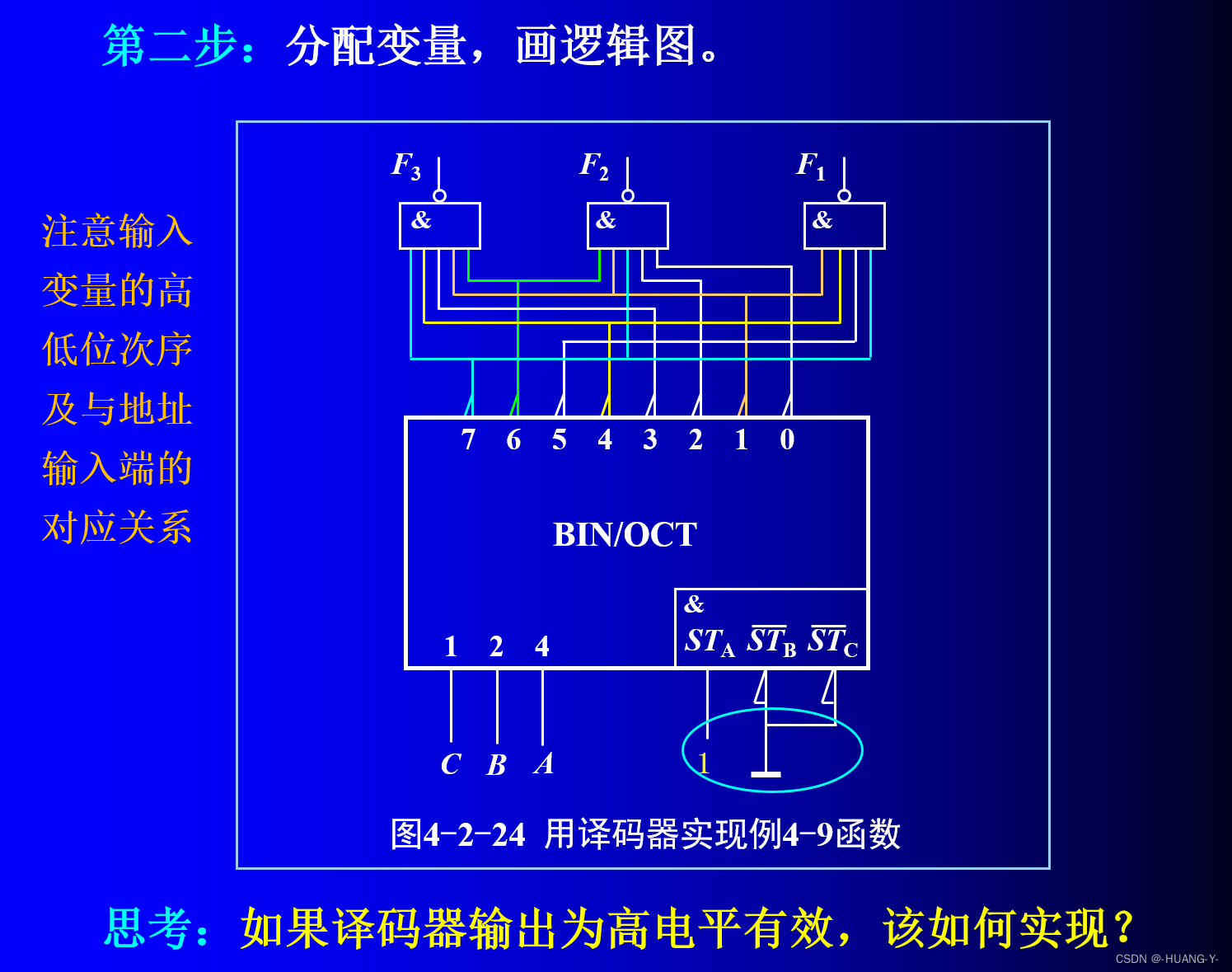

3、用译码器实现组合逻辑函数

如或是高电位输出有效,则到

如或是高电位输出有效,则到 即可。

即可。

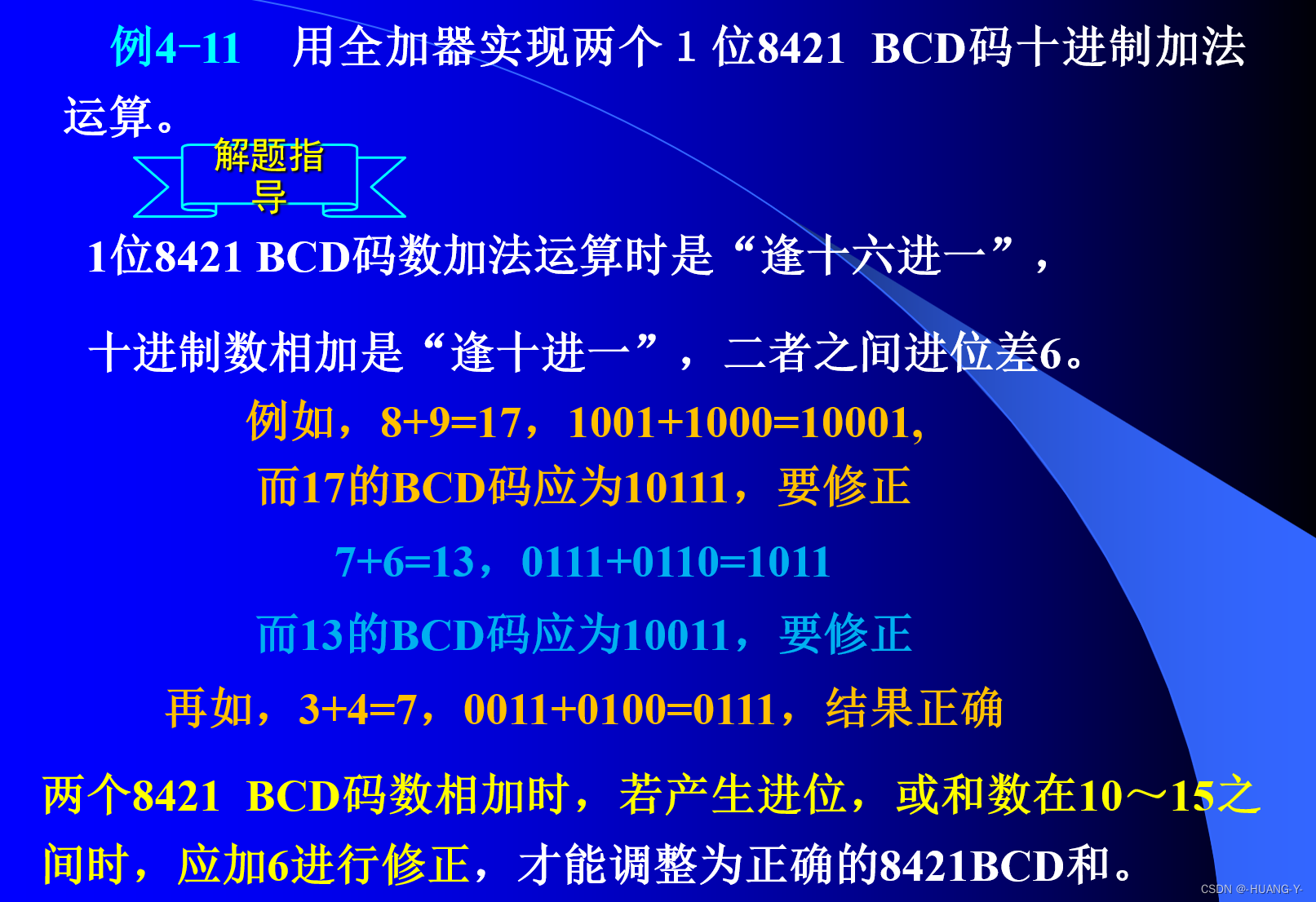

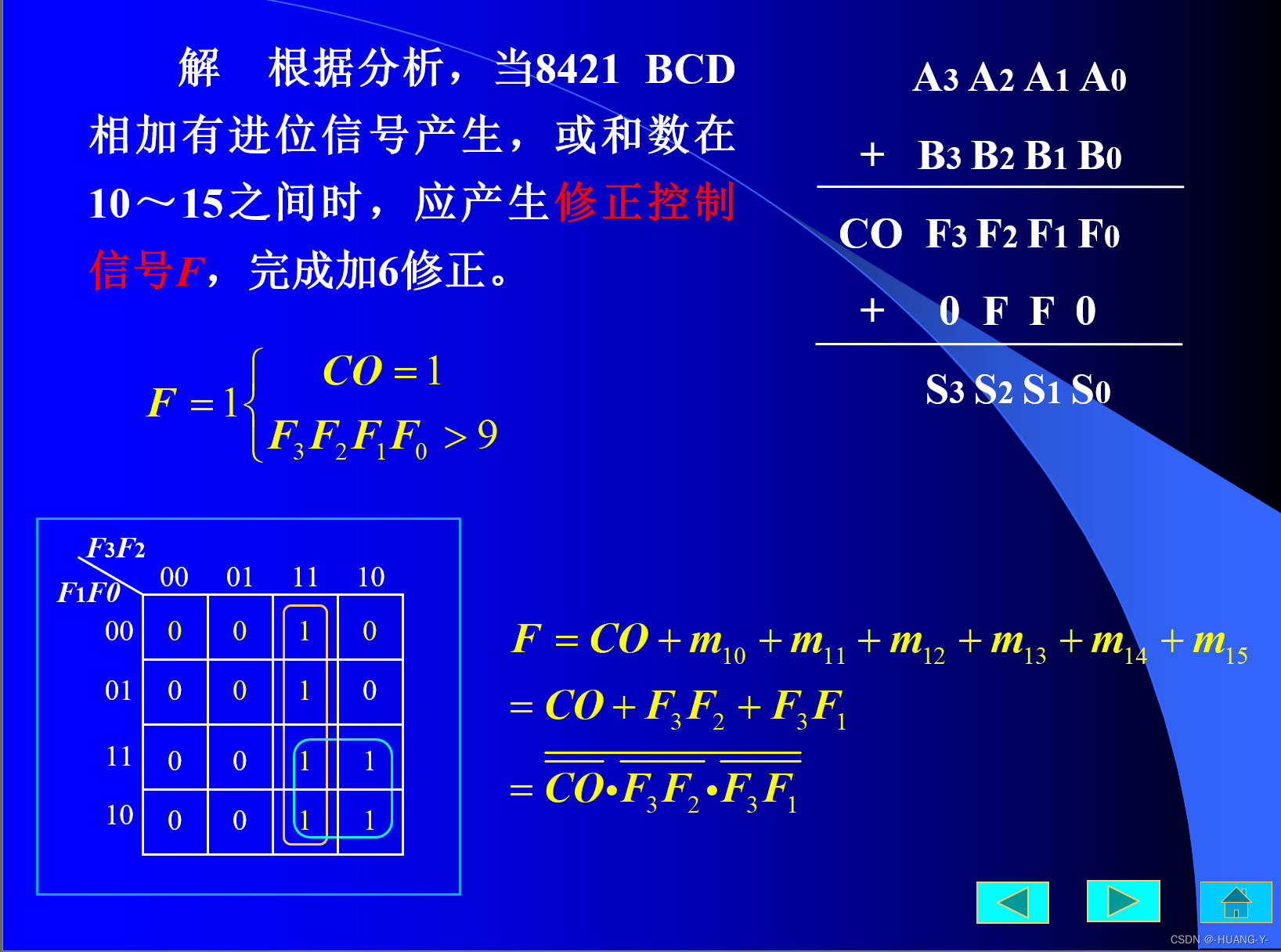

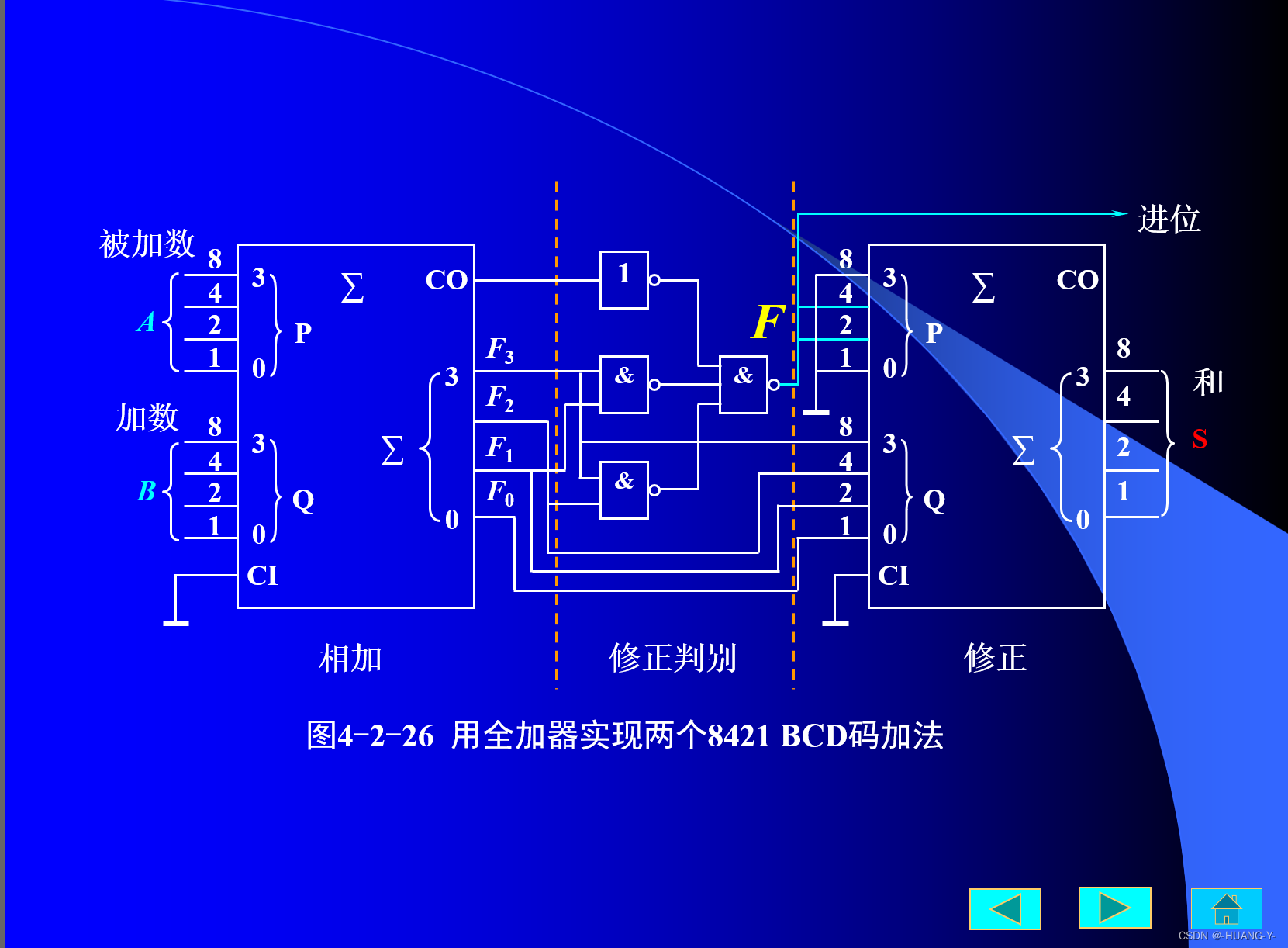

4、用全加器实现组合逻辑函数

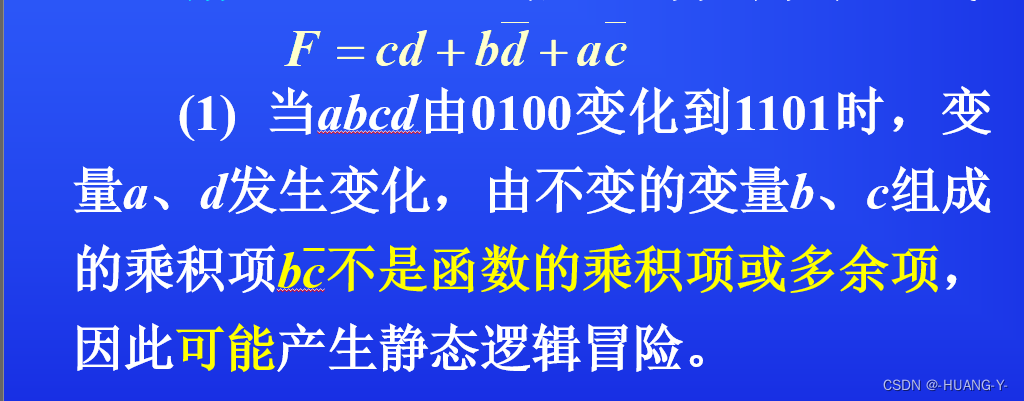

四、冒险现象

四、冒险现象

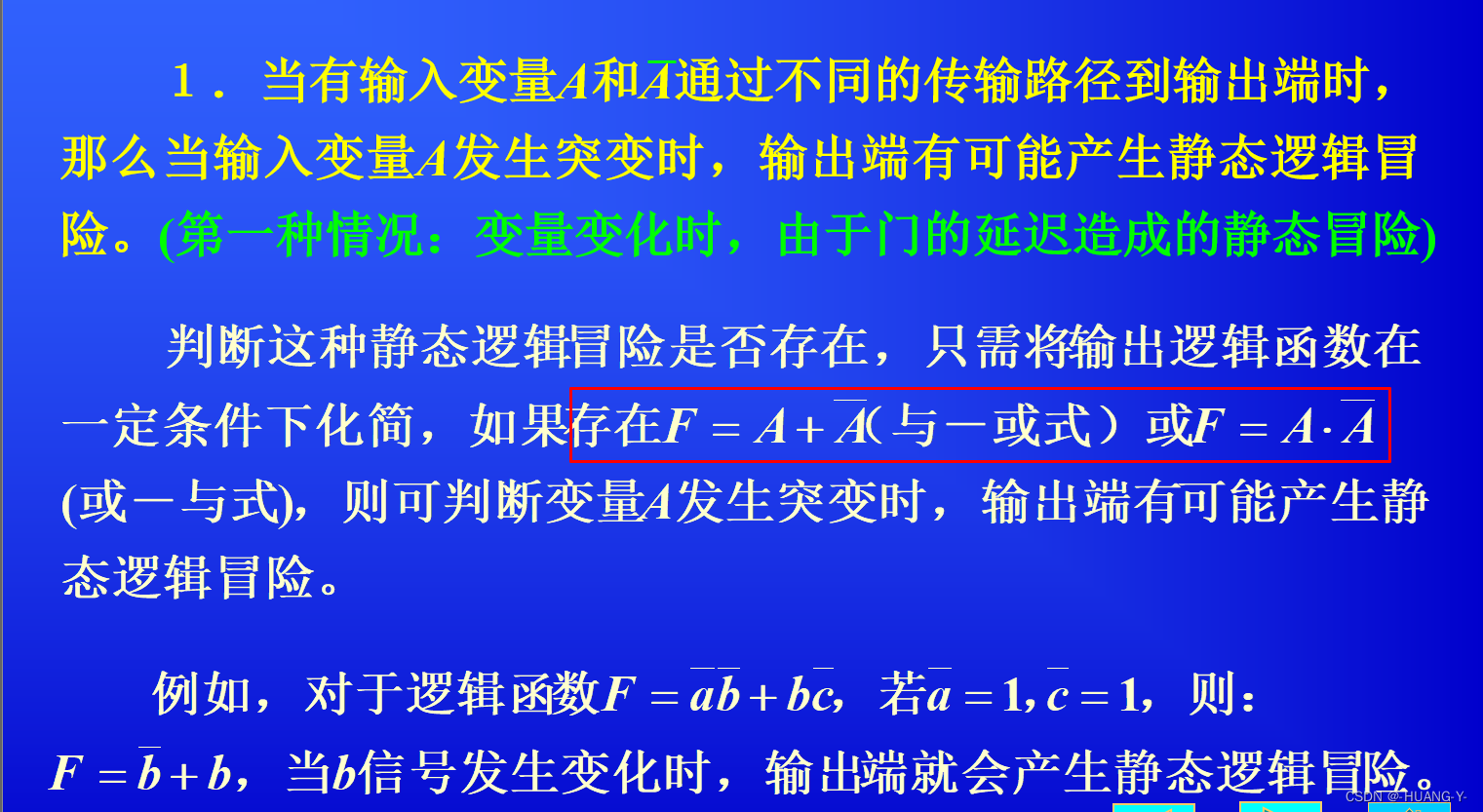

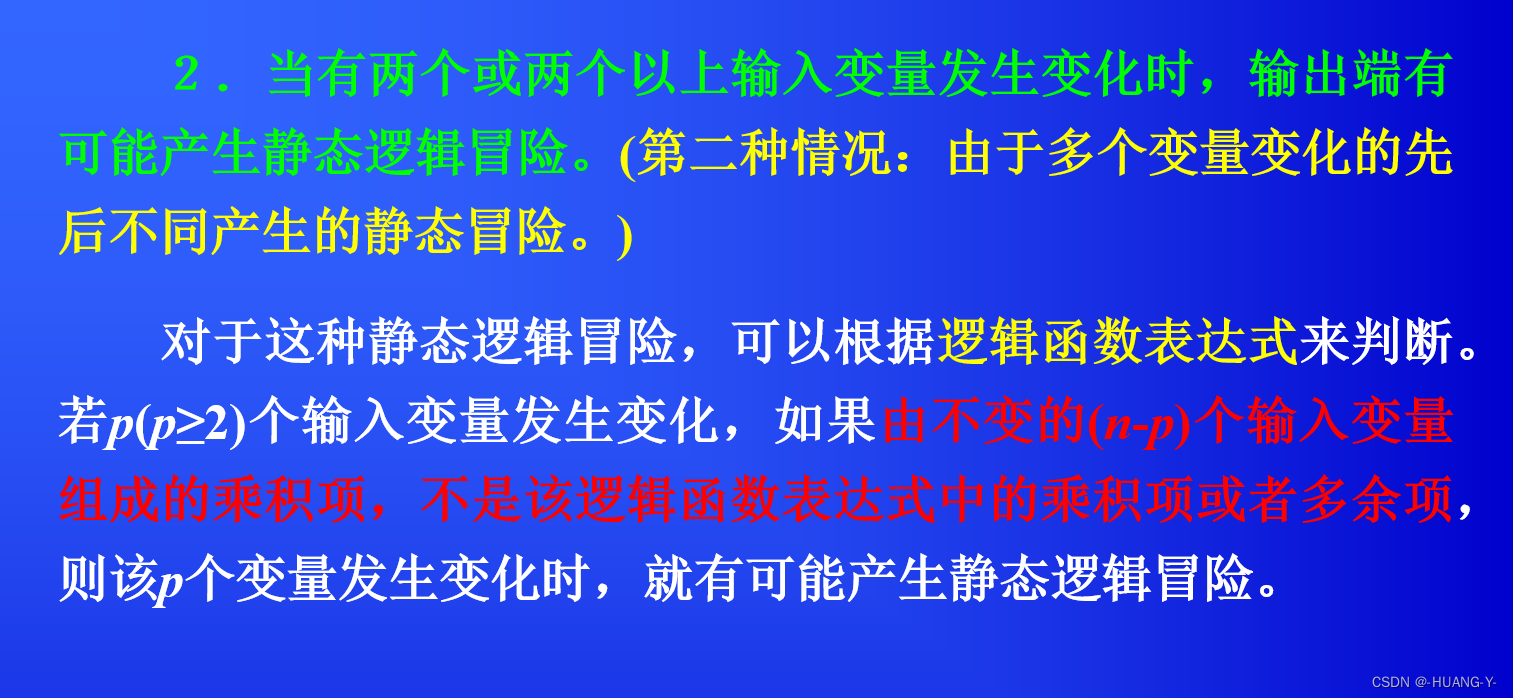

静态冒险

如:

注:若无第二种静态逻辑冒险,仍可能产生第一种情况,需代入验证。

避免逻辑冒险

1、增加多余项

2、取样脉冲信号

3、增加滤波电容

第5章 集成触发器

前言:本节触发器主要功能为存储。

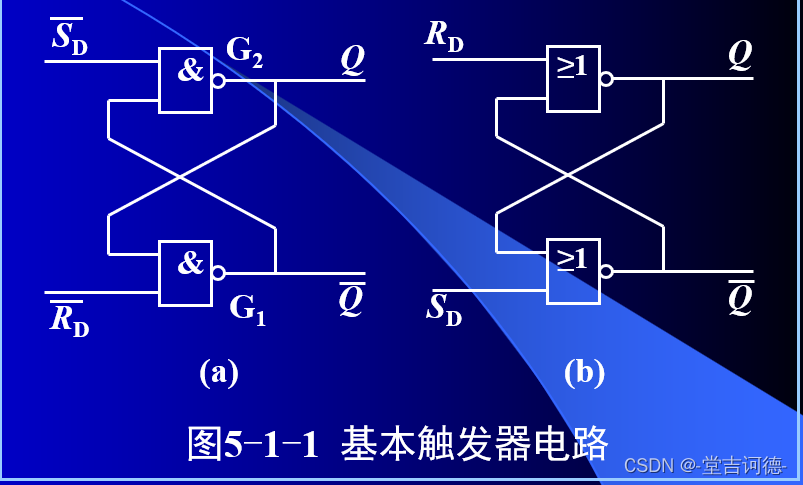

一、基本触发器

S-R锁存器

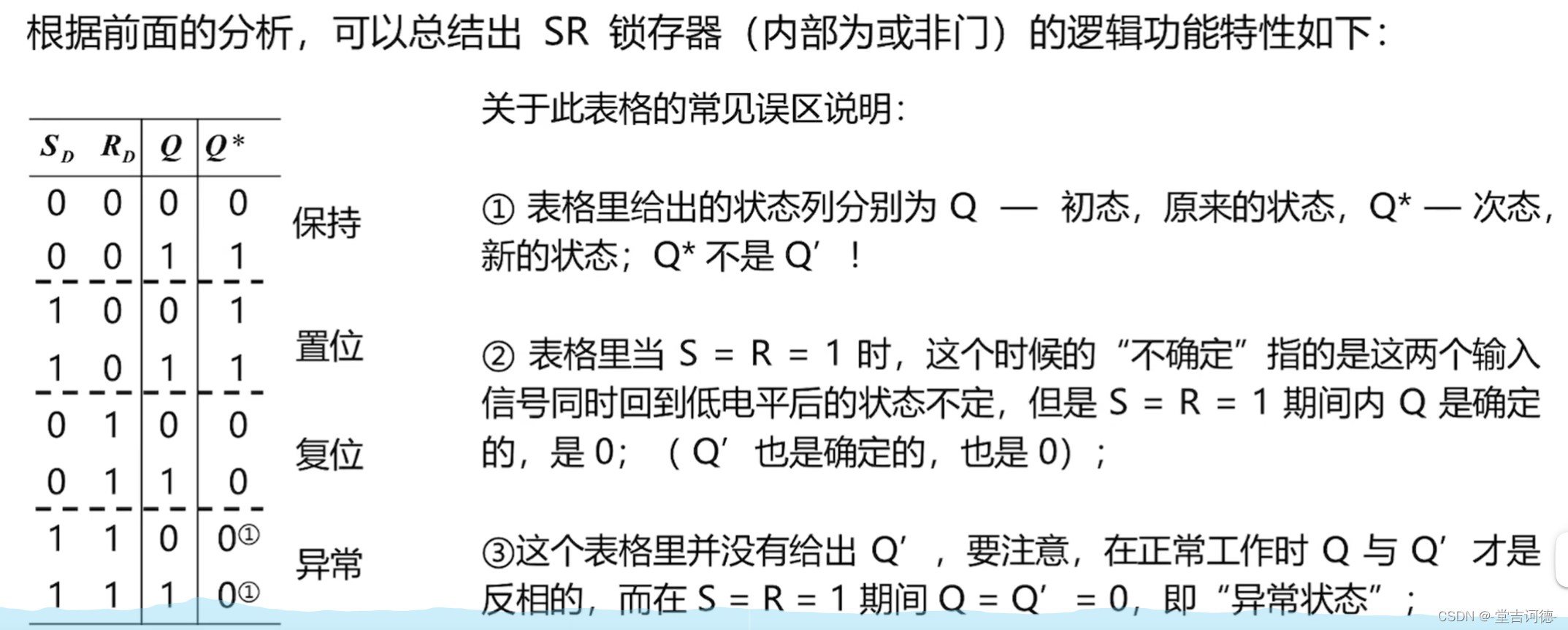

或非门:

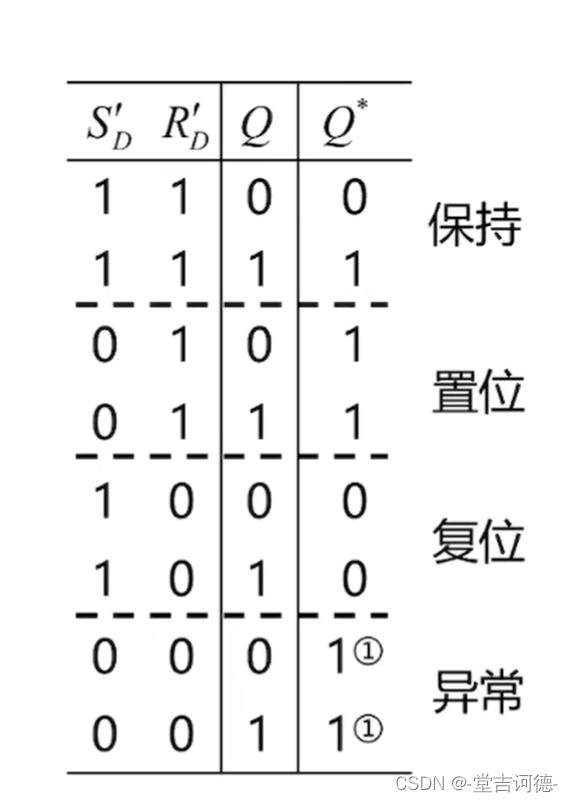

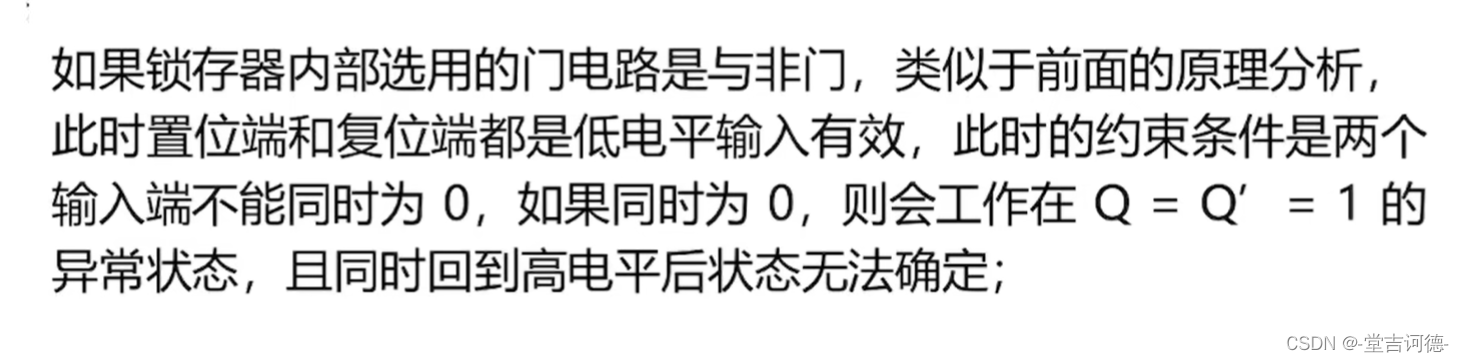

与非门:

总结:

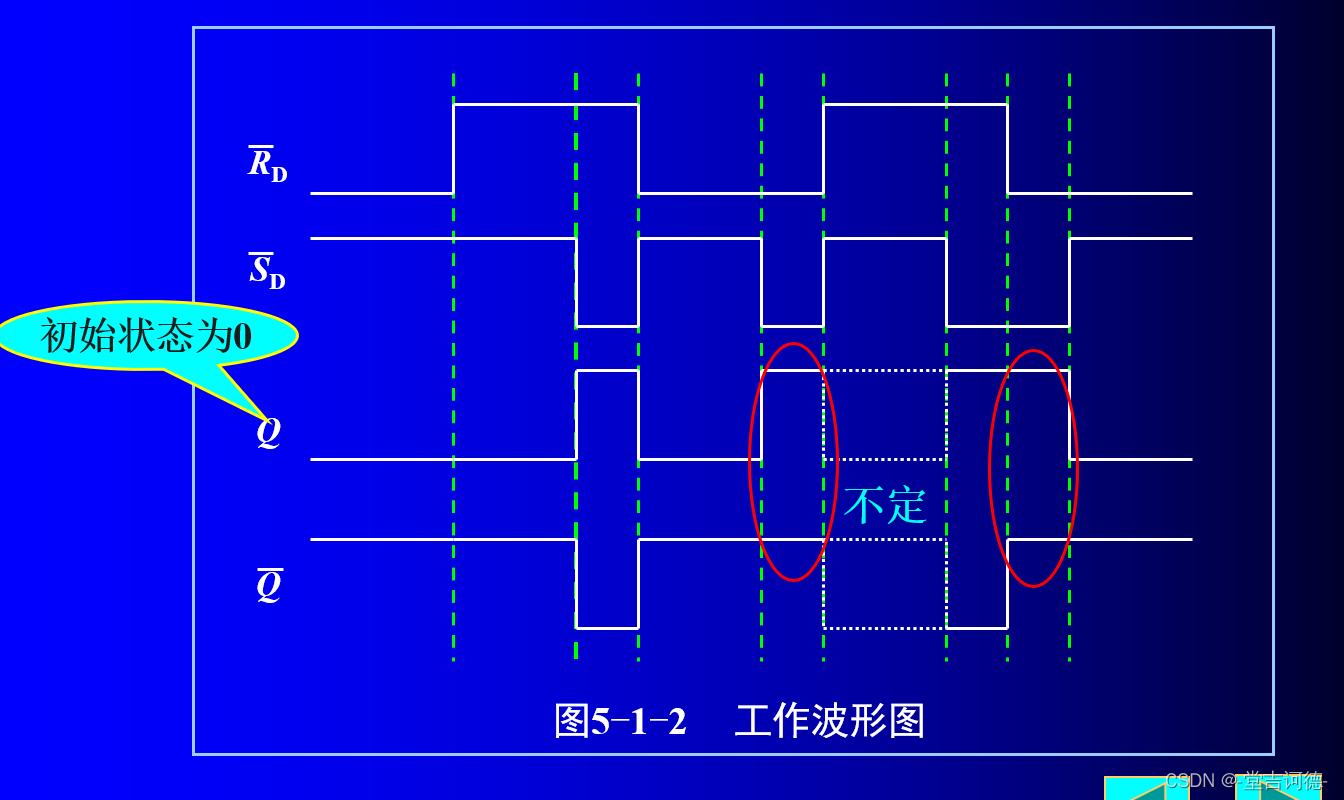

两个输入同时有效为异常状态,会使得两个输出同时为1或0;而当输入有效同时撤回时,即由异常状态变为保持状态,此时输出不定。

功能描述(与非门S-R锁存器为例):

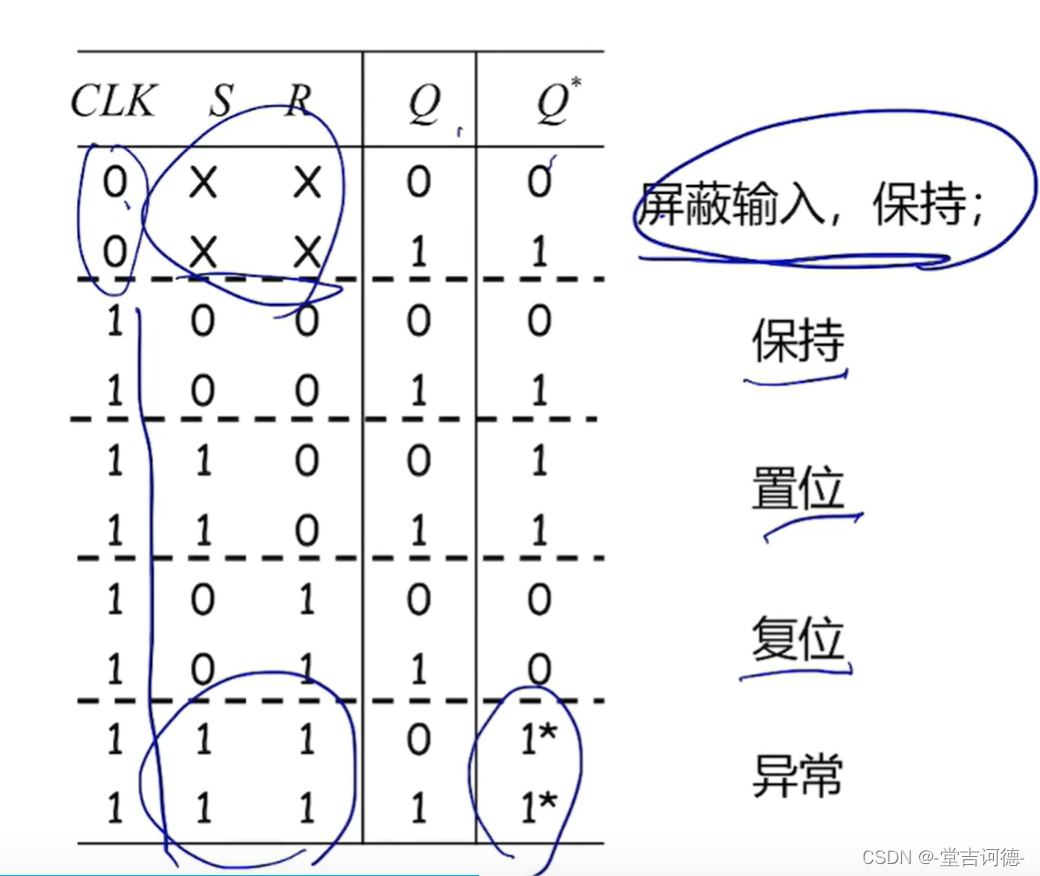

真值表:

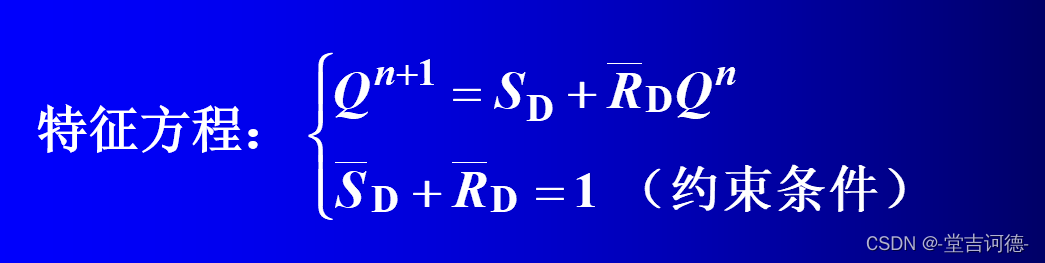

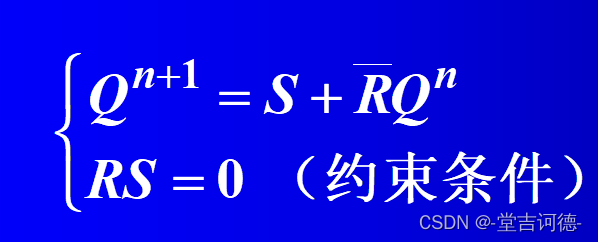

特征方程(可由卡诺图推出):

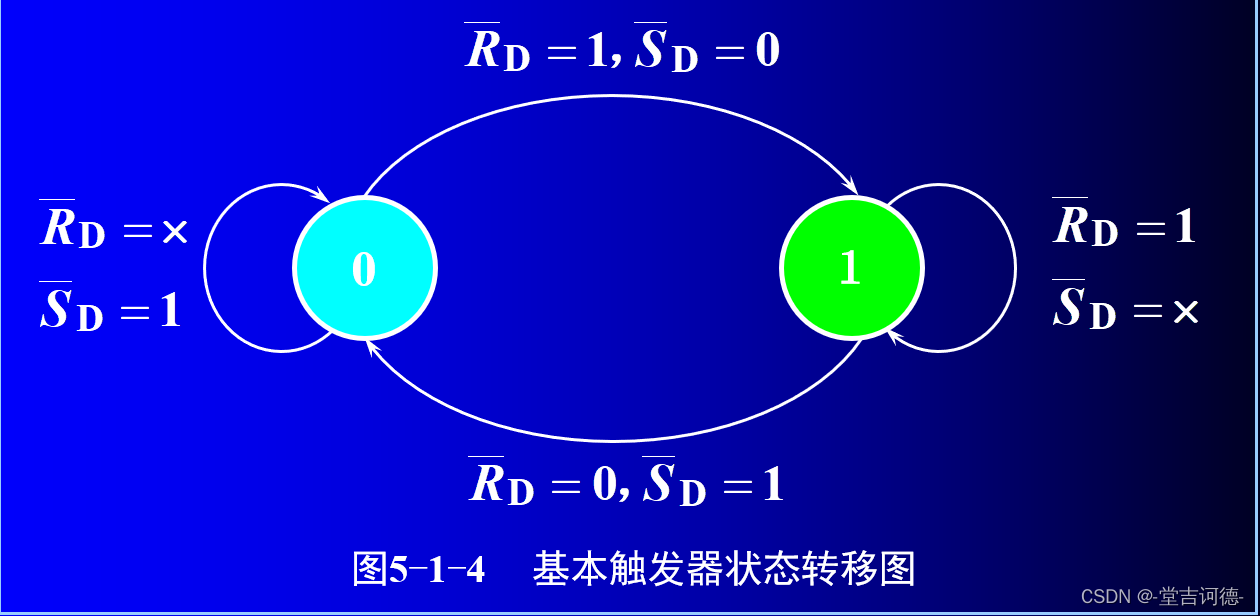

状态转移图:

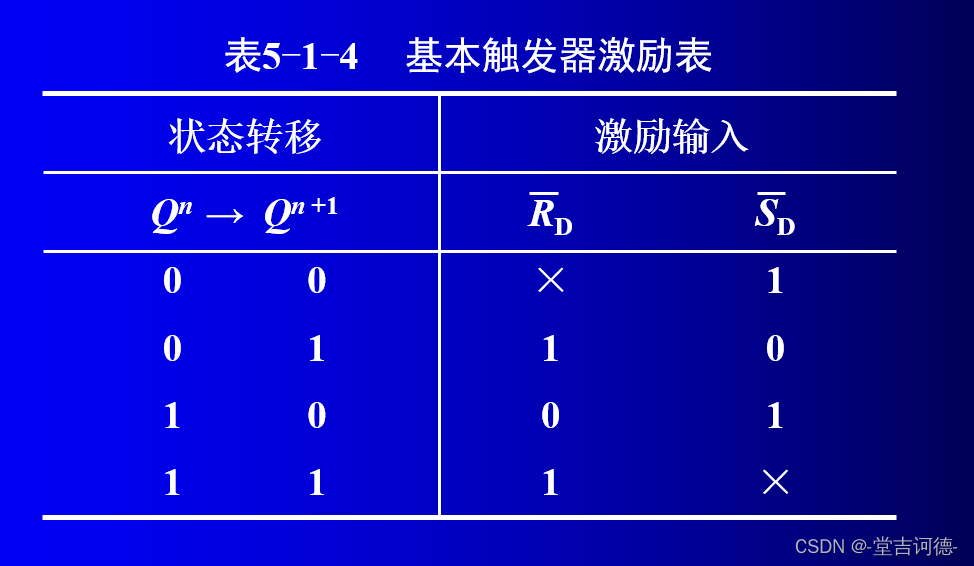

激励表:

波形图:

缺点 :

输出由输入信号直接控制,抗干扰性差。

二、钟控触发器

以下均为电位触发方式:

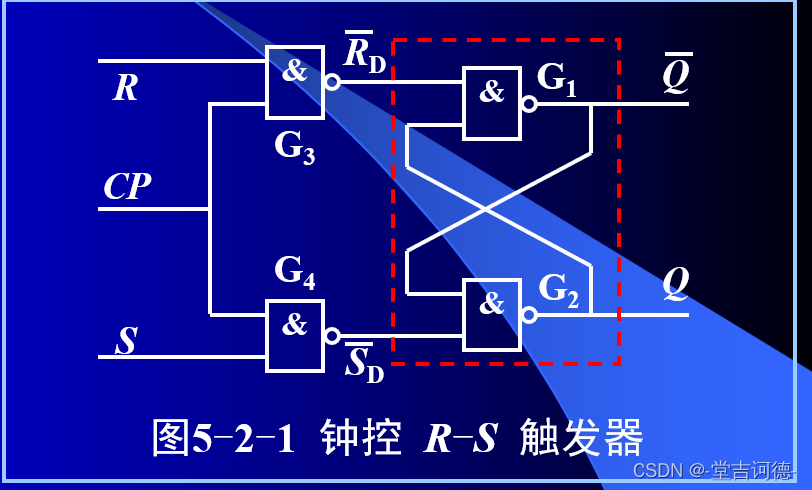

1、钟控R-S触发器

注意:

异常状况当CLK=S=R=1的时候,输出为1;当此种情况下,撤去CLK=1或撤去S=R=1,输出不确定。

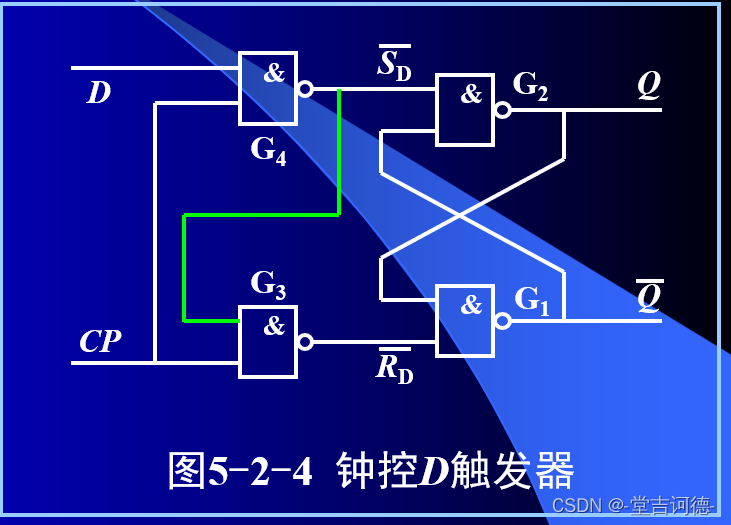

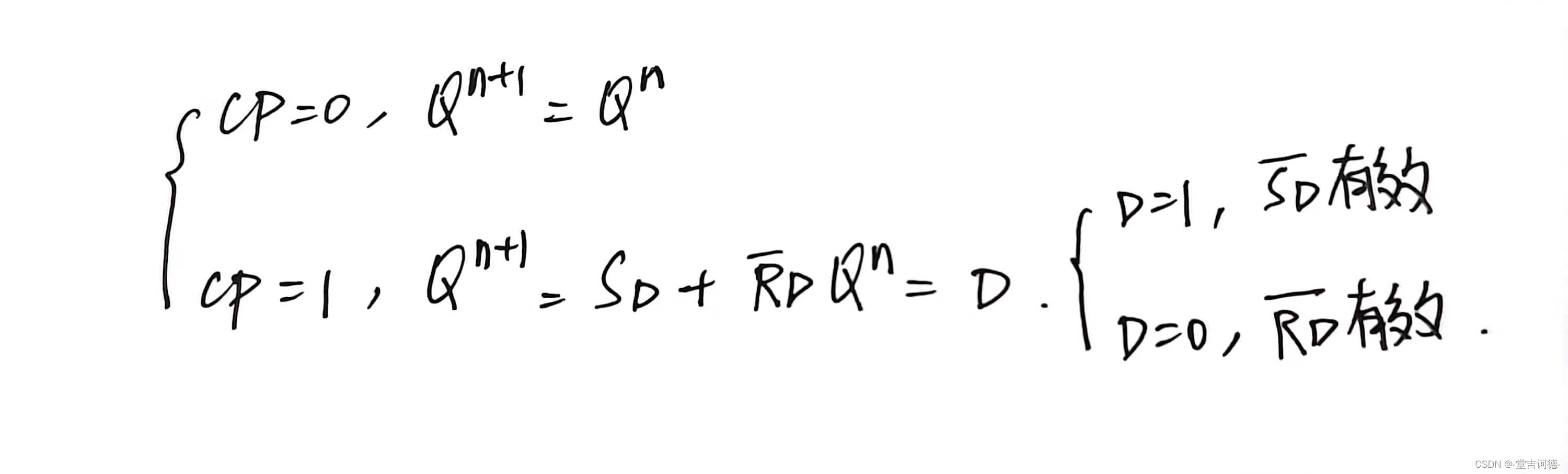

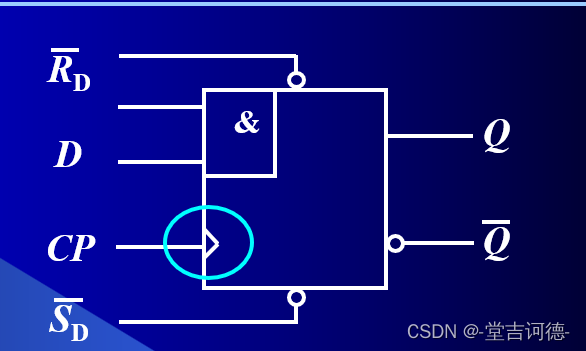

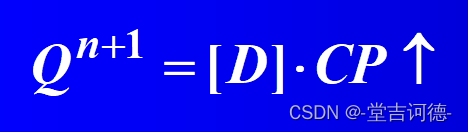

2、钟控D触发器

注意:

钟控D触发器避免了出现异常情况,但仍有缺点:如若想在CP有效的情况下保持电平,需要保持D输入端不变。

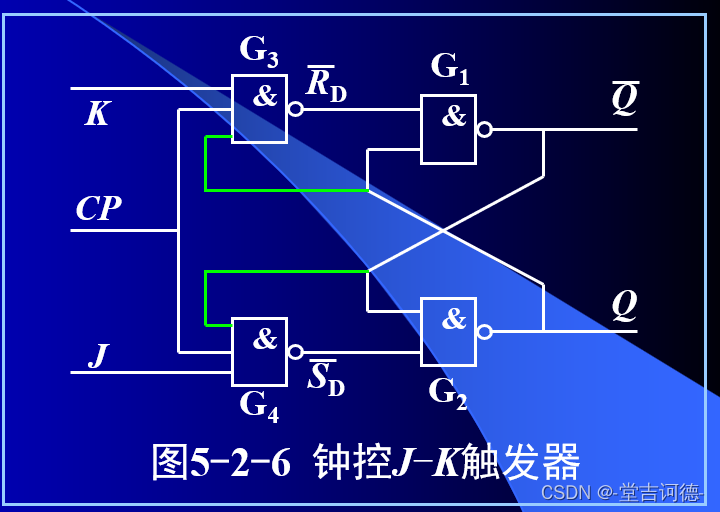

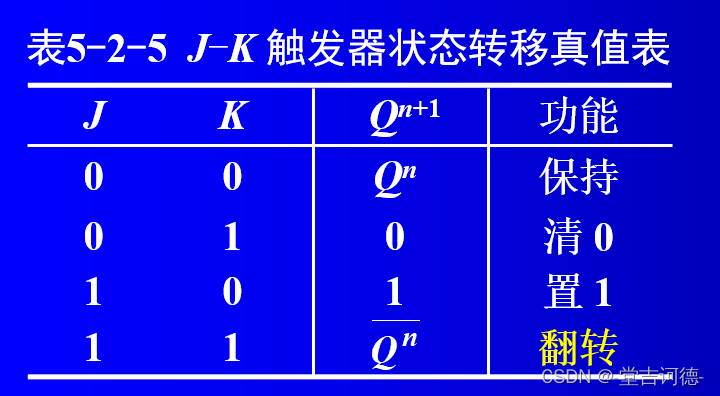

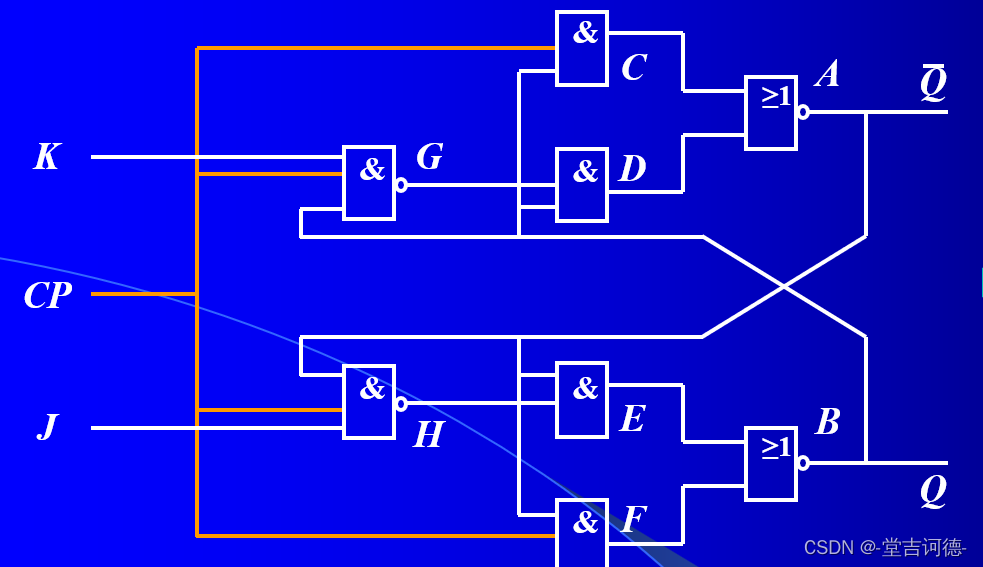

3、钟控J-K触发器

![]()

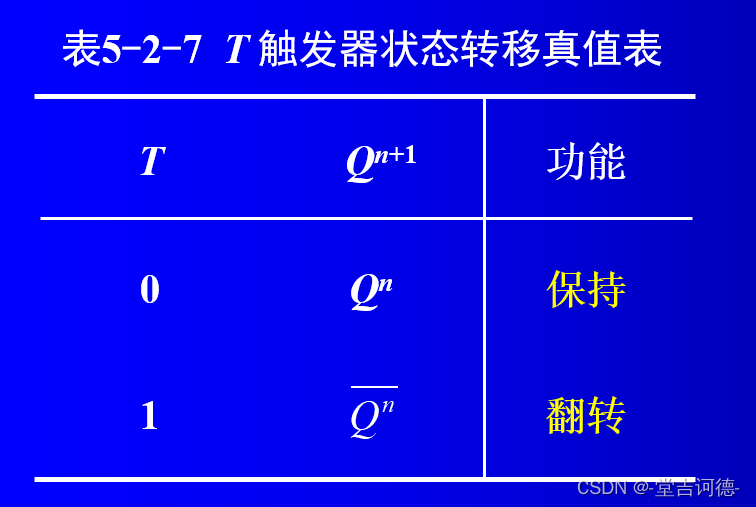

4、钟控T触发器

![]()

三、主从触发器

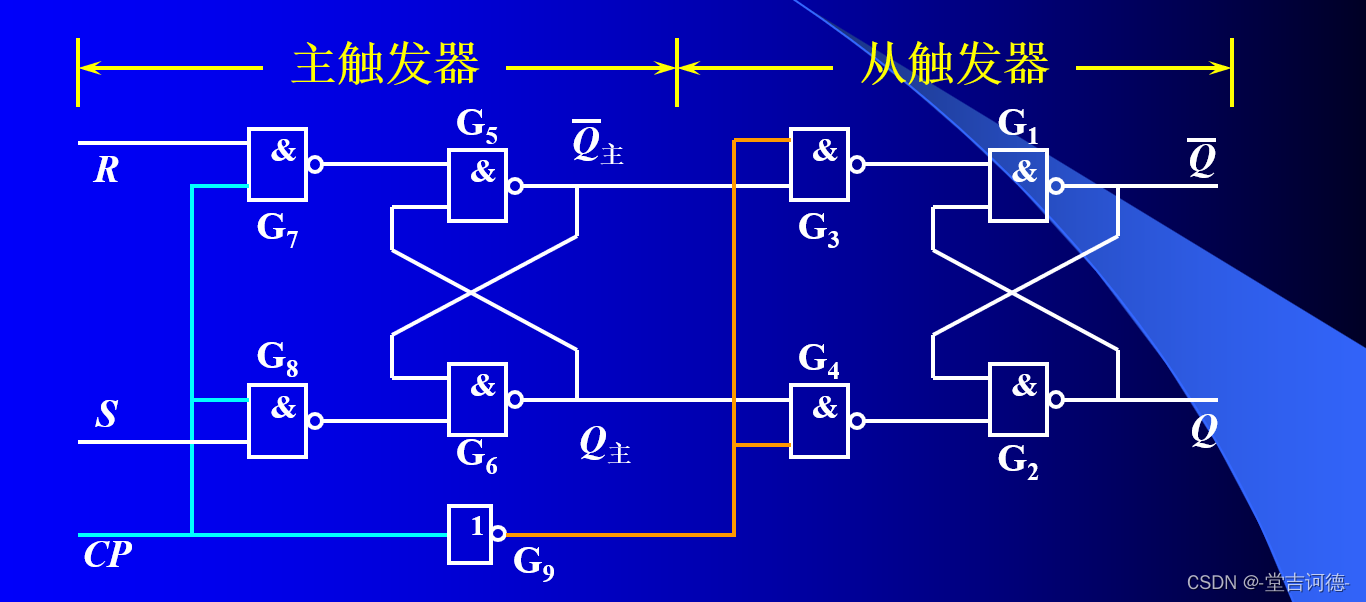

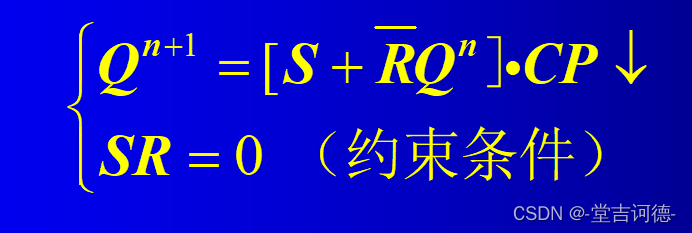

1、主从R-S锁存器

只在下降沿发生状态转移,其余时刻保持。

S=R=1时,CP由1变为0后,输出不定。

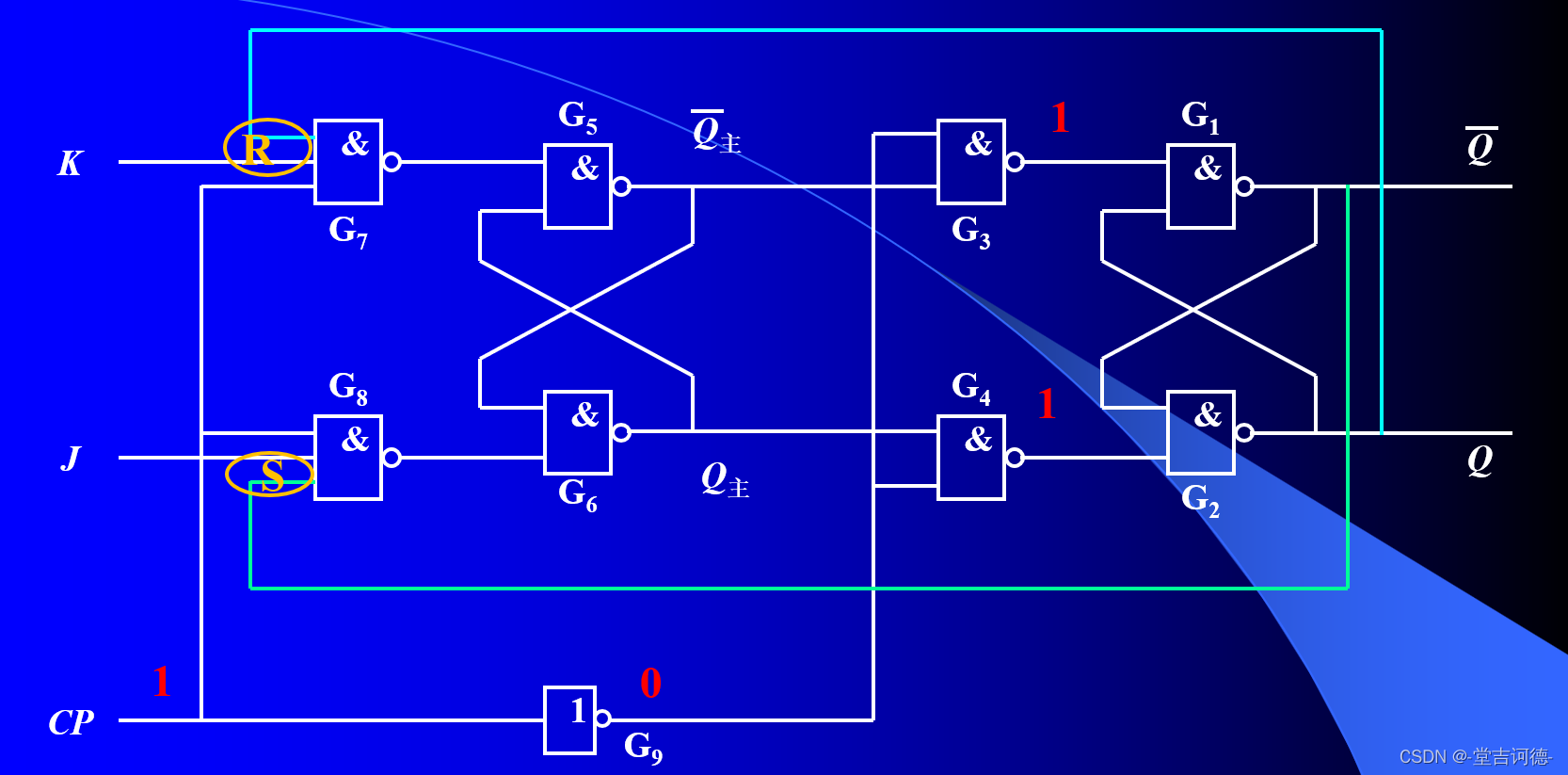

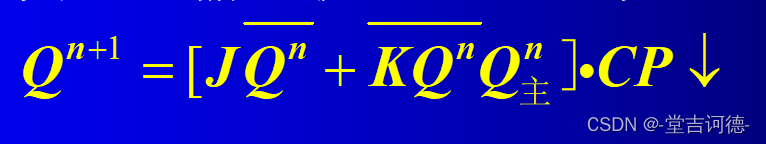

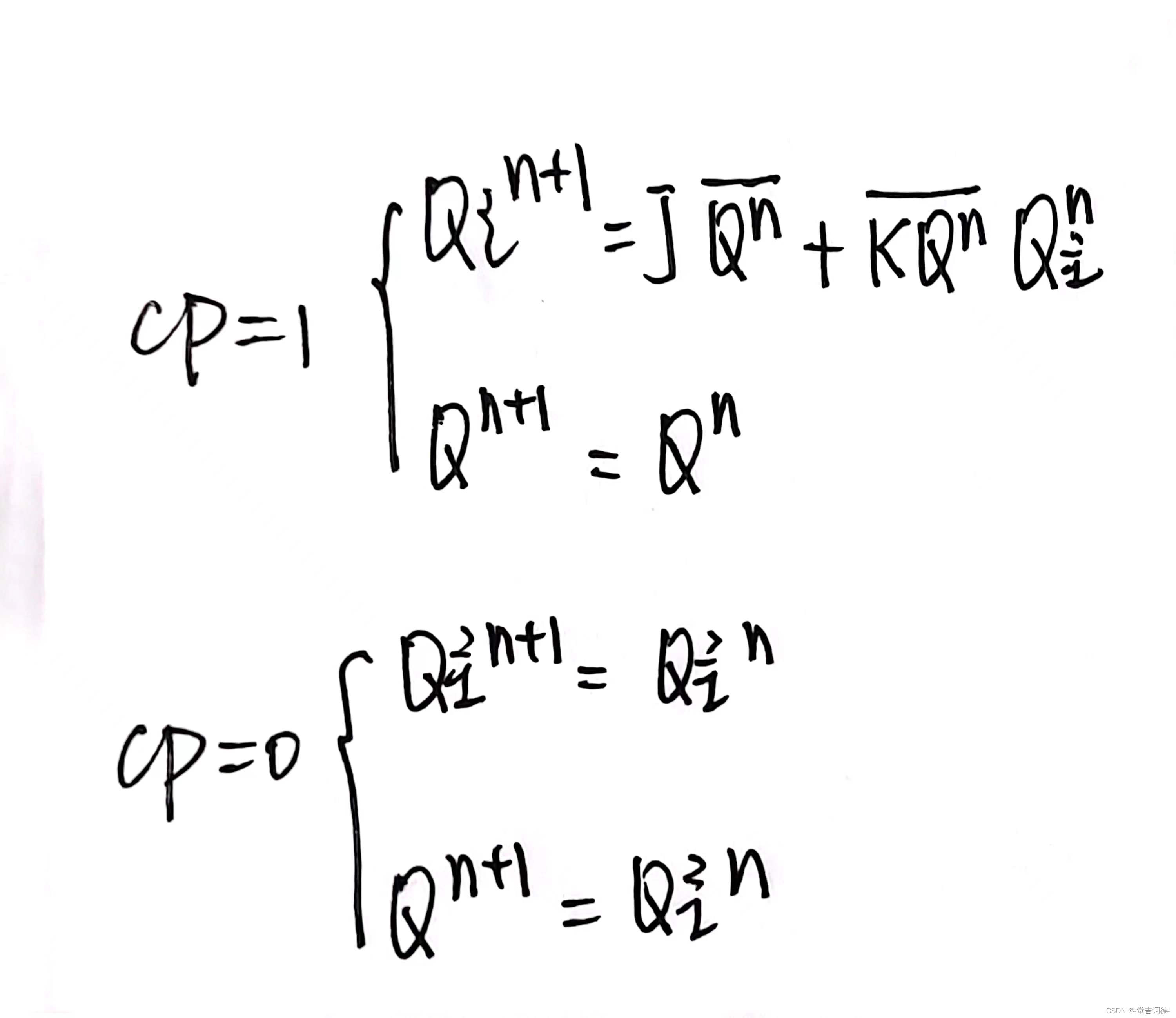

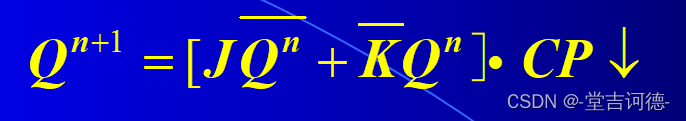

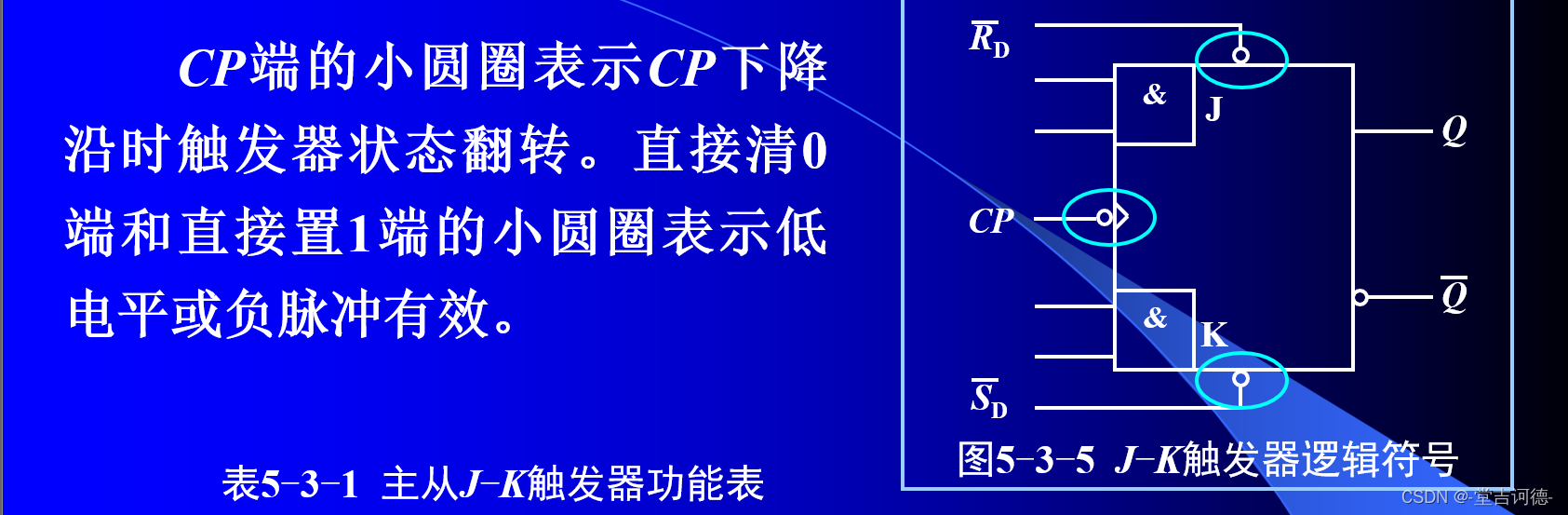

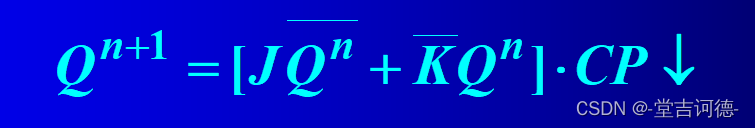

2、主从J-K触发器

宽脉冲情况:

Q只在下降沿发生变化。

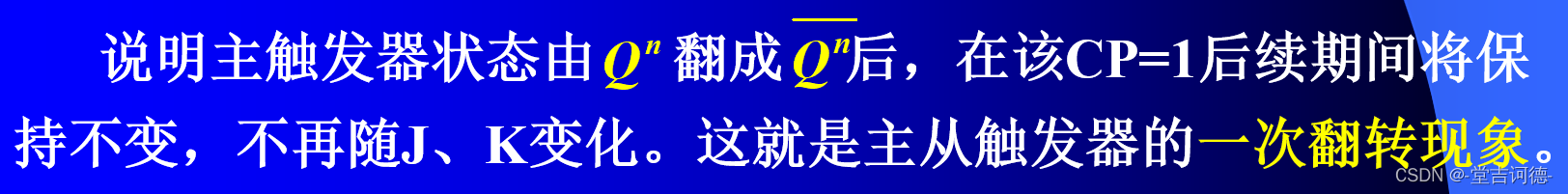

一次翻转现象:

(之后Q主不随CP和J、K变化)

窄脉冲情况:

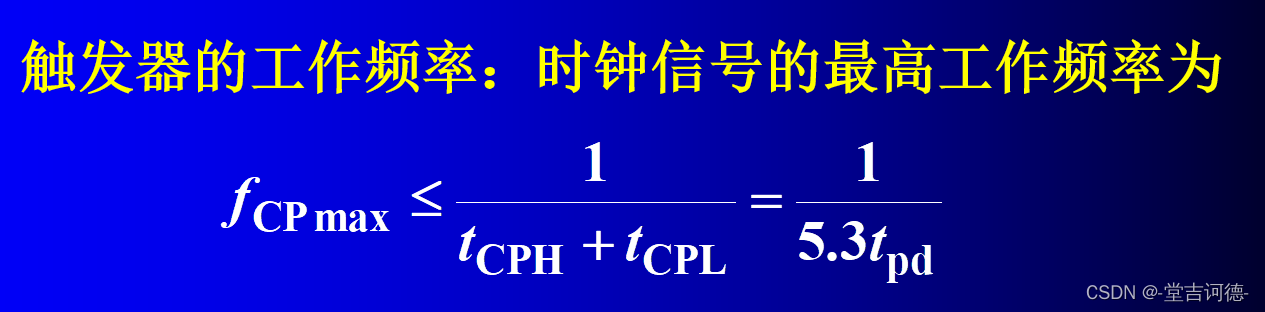

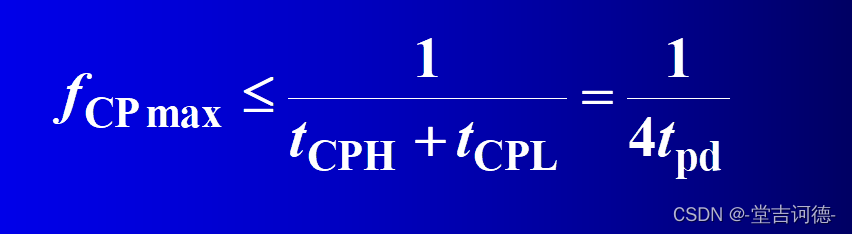

工作频率:

四、边沿触发器

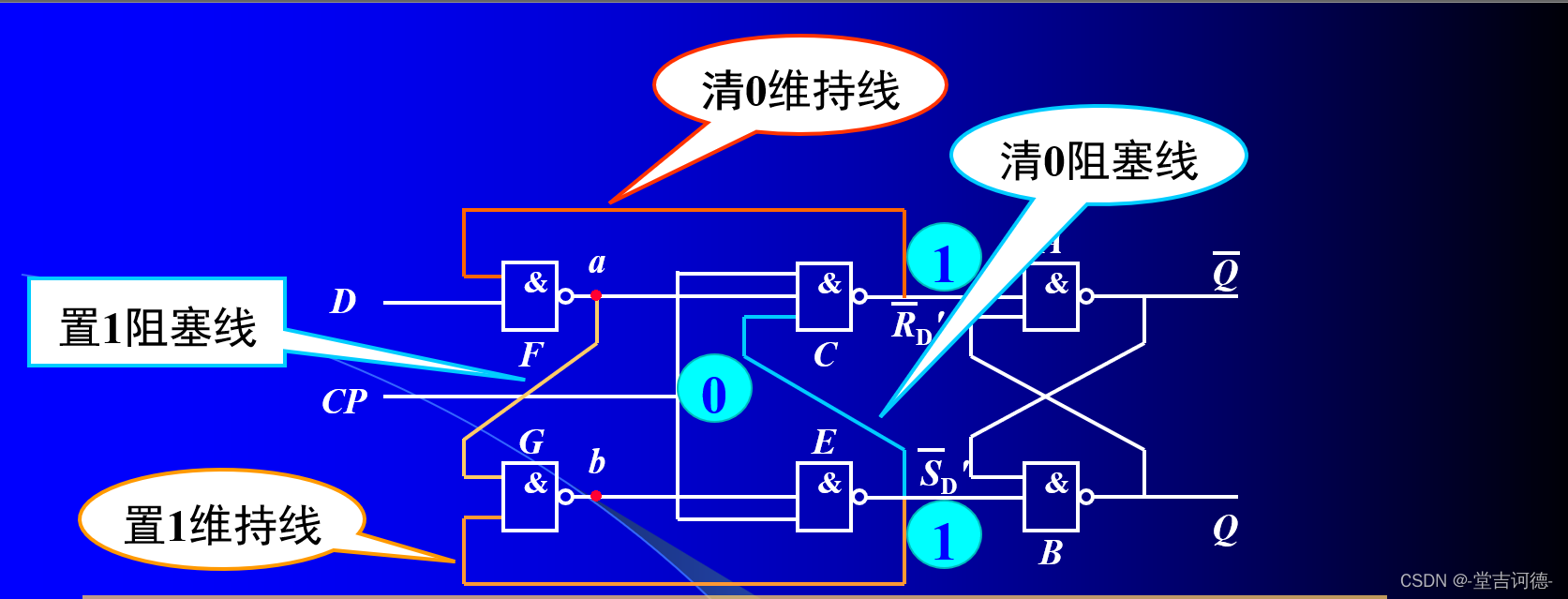

1、维持阻塞的D触发器

2、下降沿触发的边沿触发器

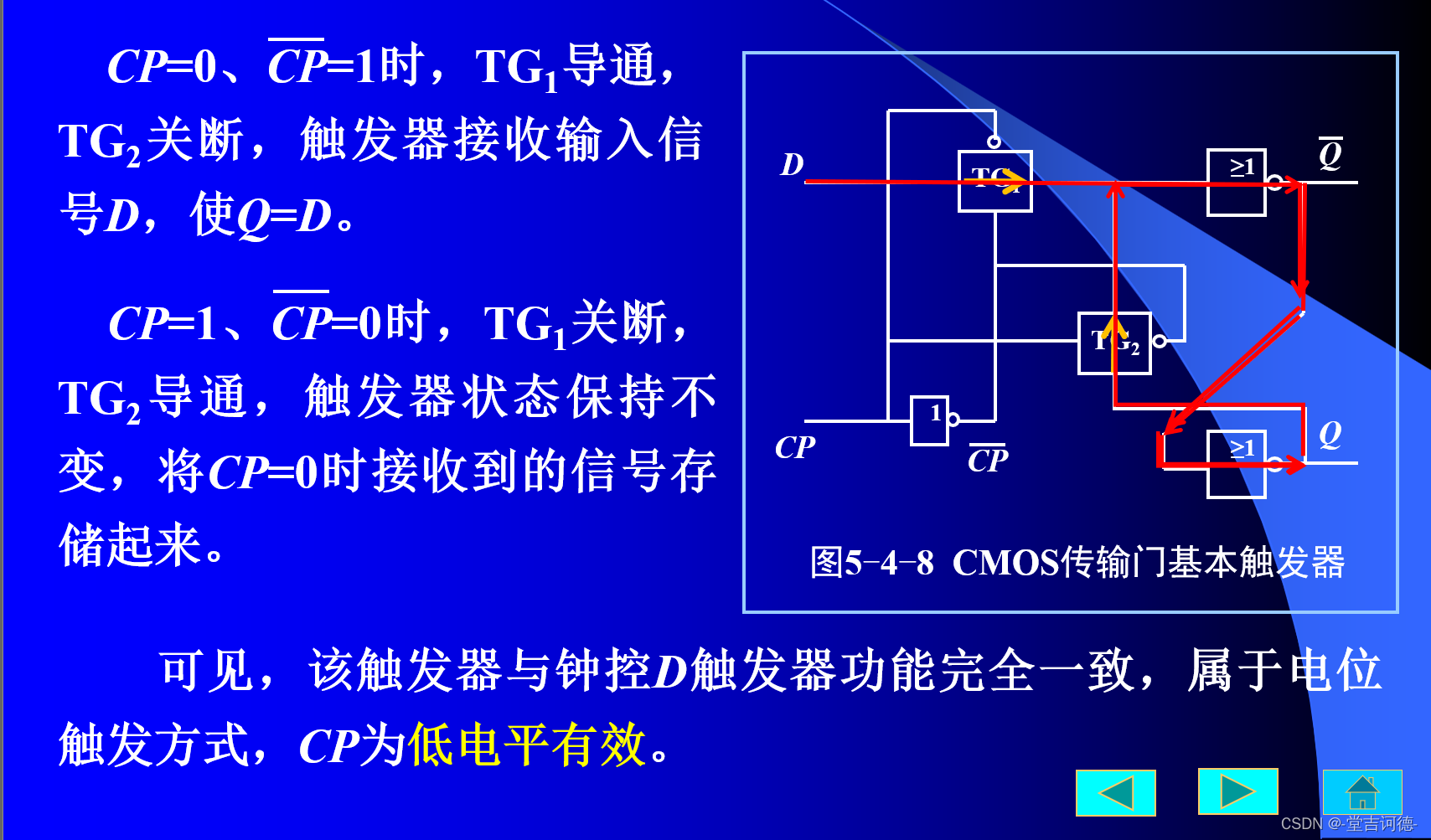

3、CMOS构成的基本触发器

第5章 时序逻辑电路

寄存器

1、寄存器对触发方式无要求,但必须要求触发器有置1置0的功能。

2、利用时钟信号的延迟特性实现触发器不同位的转换。

移位寄存器

1、左移位寄存器

2、右移位寄存器

3、双向移位寄存器

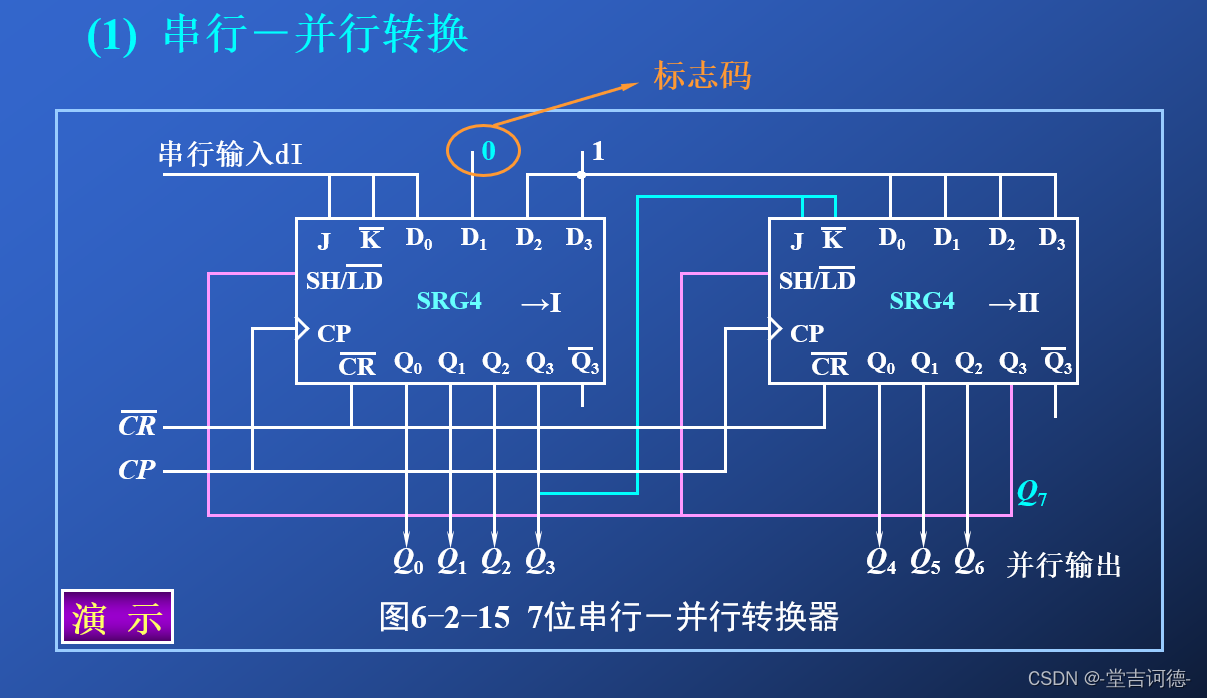

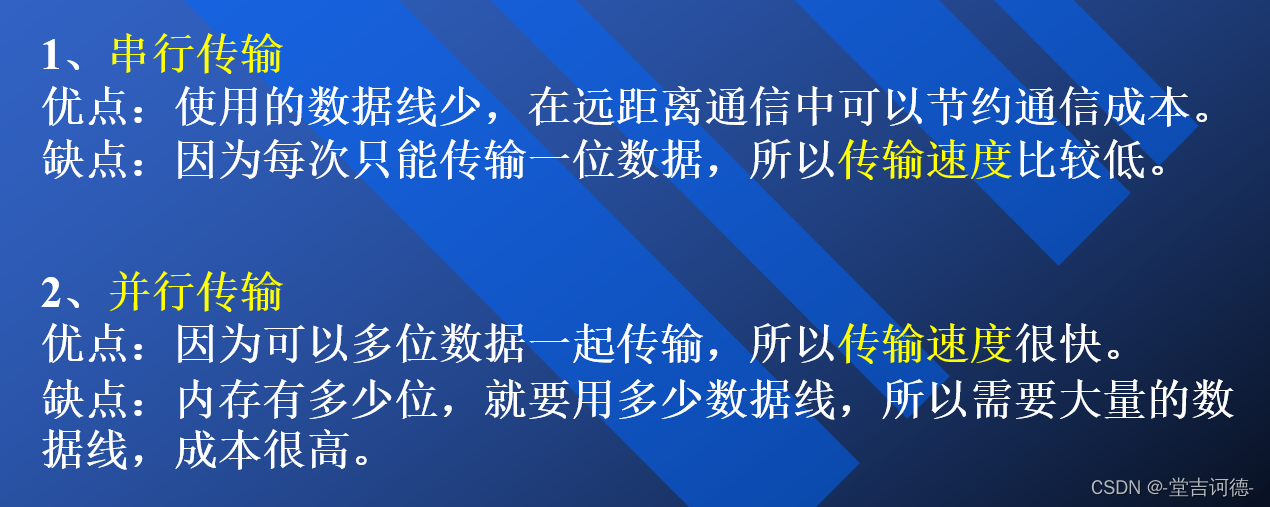

4、串行输入并行输出(N个时钟信号)

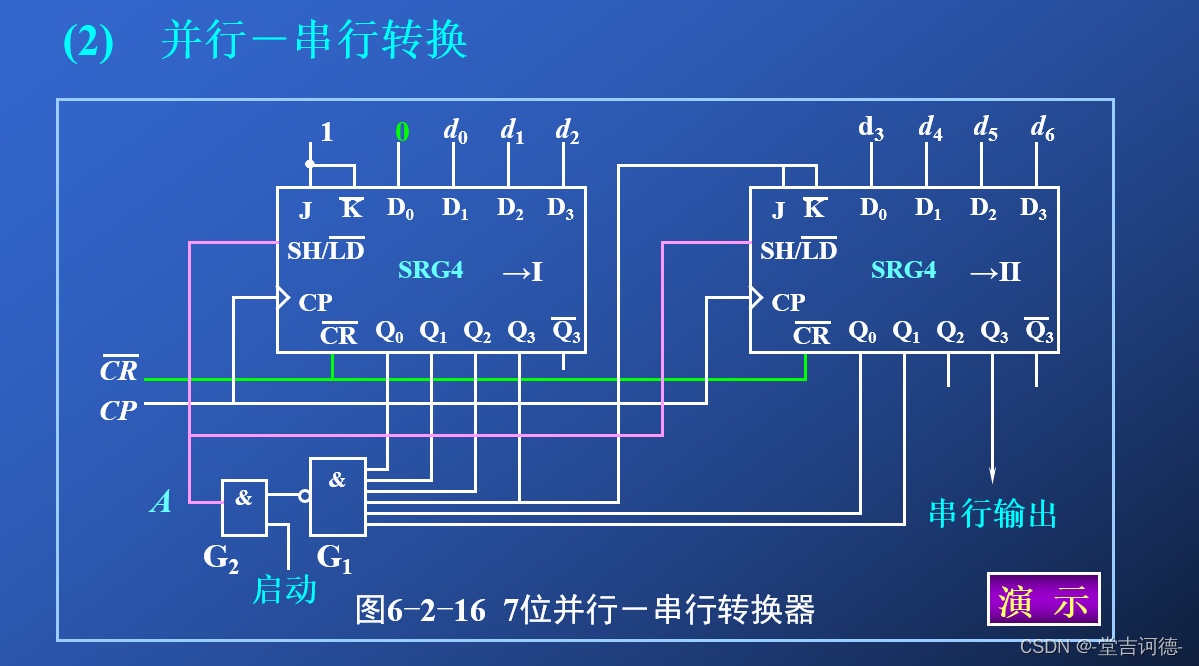

5、并行输入串行输出

(2N-1个时钟信号,一开始要清零,并行取样脉冲M=1取样,M=0移存)

![]()

应用:

(1) 实现数码串-并行转换

(2) 移位寄存器用于脉冲节拍延迟

(3) 移位寄存器还可构成计数分频电路、序列信号发生器等

(4) 移位寄存器实现乘法或除法运算

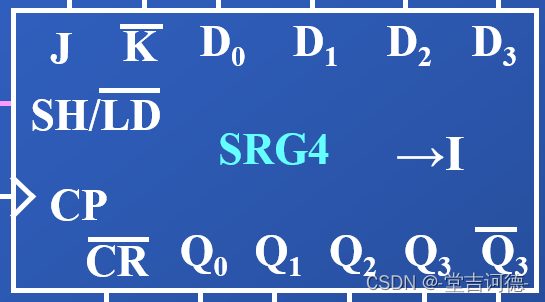

集成移位寄存器

计数器

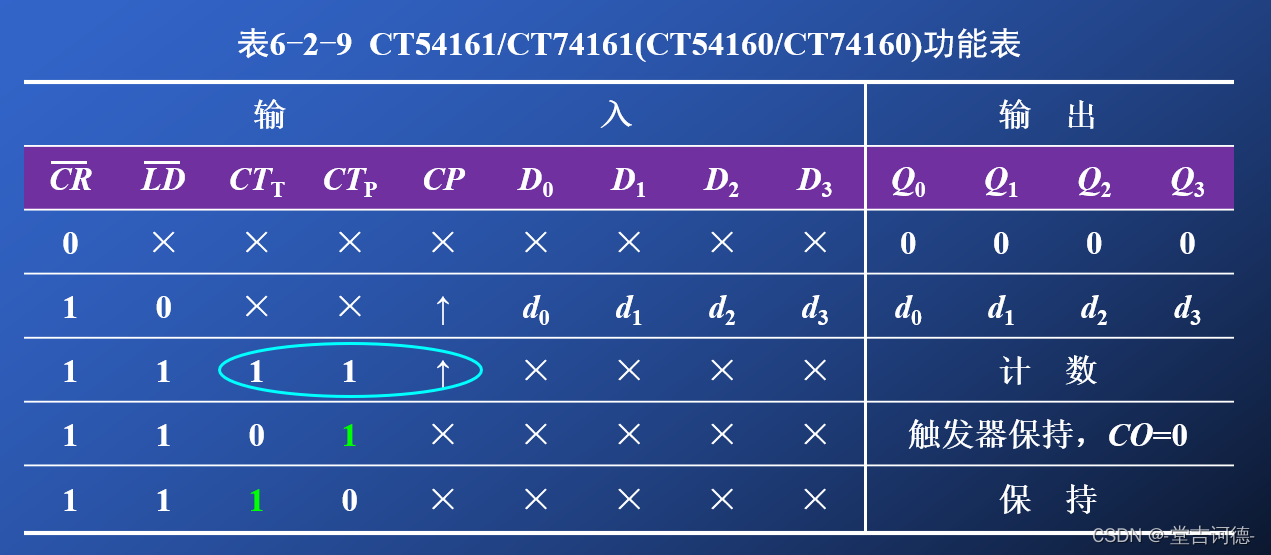

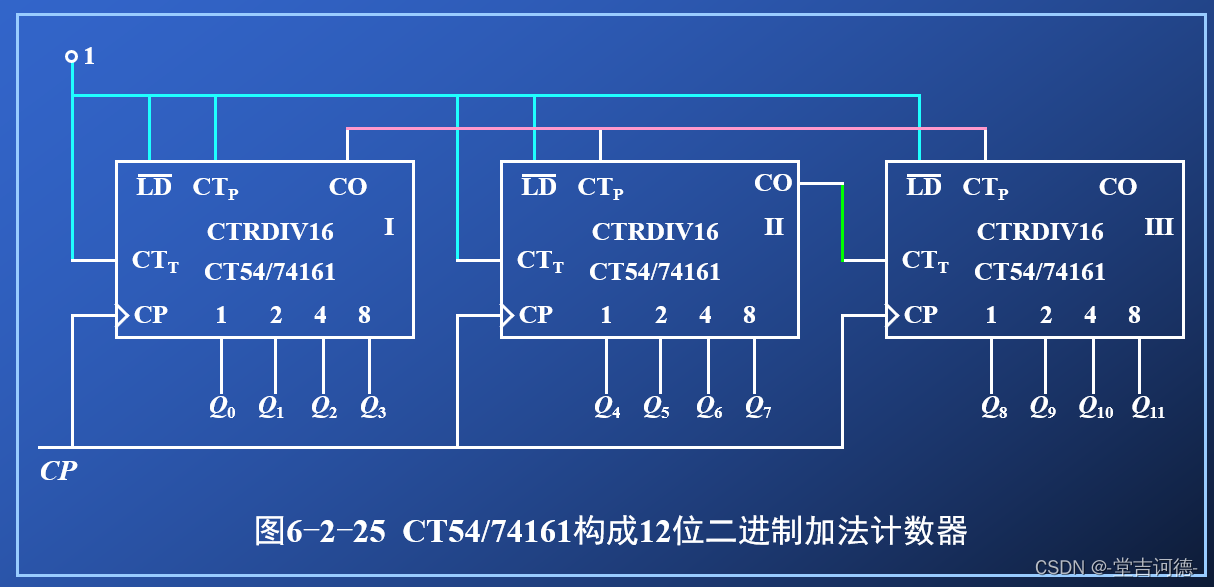

集成同步计数器

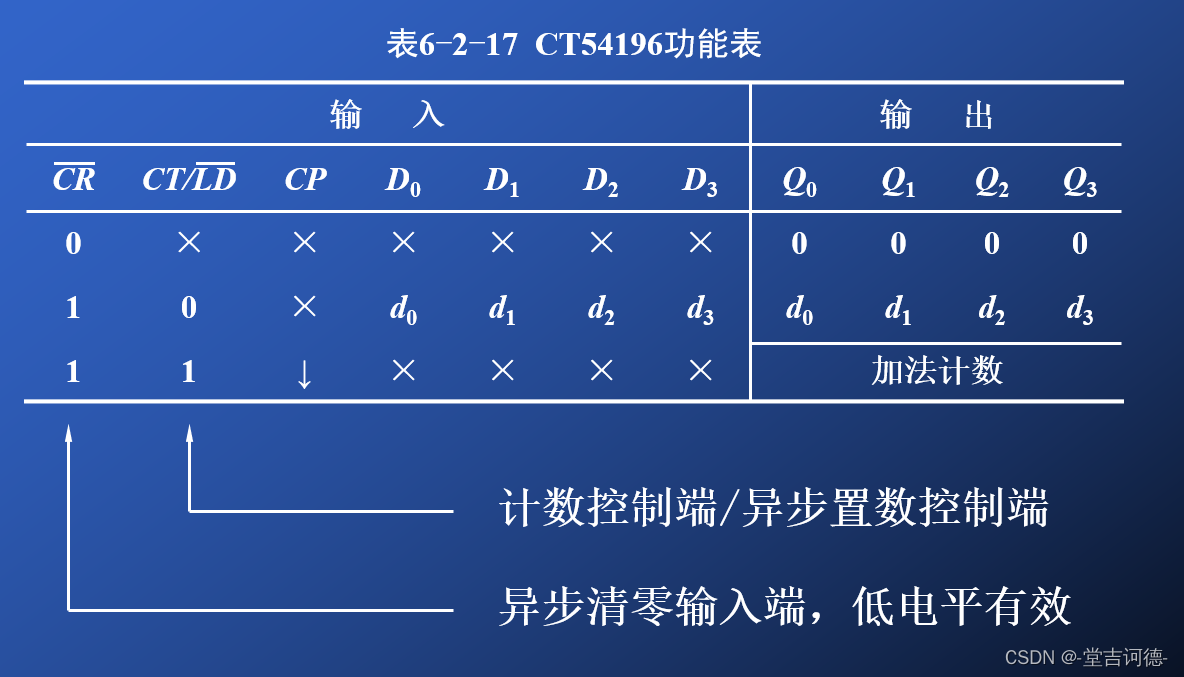

集成异步计数器

时序逻辑电路设计

采用小规模集成器件设计同步计数器

1、建立状态图

2、状态分配

3、求状态转移方程(卡诺图化简)

4、检验自启动特性(确定转移方向)

5、选择触发器类型并画逻辑电路图

采用小规模集成器件设计异步计数器

1、建立原始状态图

2、建立状态转移表

3、选择各级触发器时钟信号(重要)

4、作状态转移表(求出各级触发器在各自被触发时刻的状态转移情况,将不被触发时刻的转移状态作为任意态处理)

5、求解各级触发器的状态转移方程和输出方程(卡诺图)

6、检验自启动特性

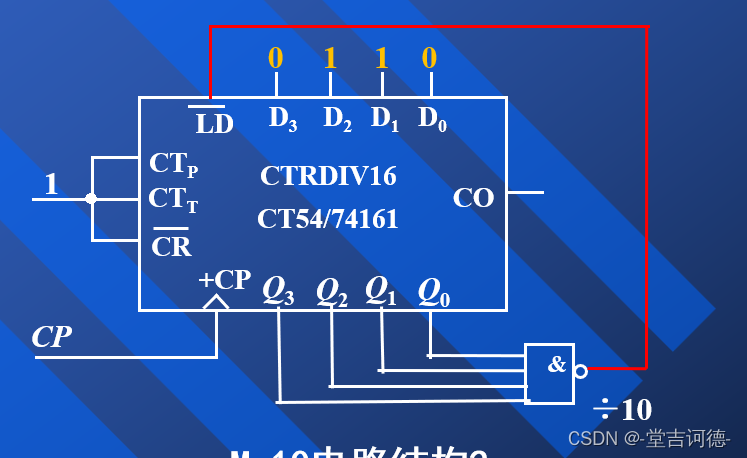

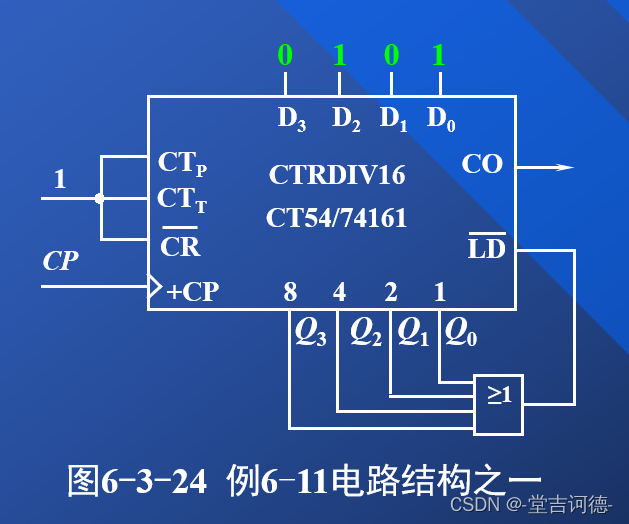

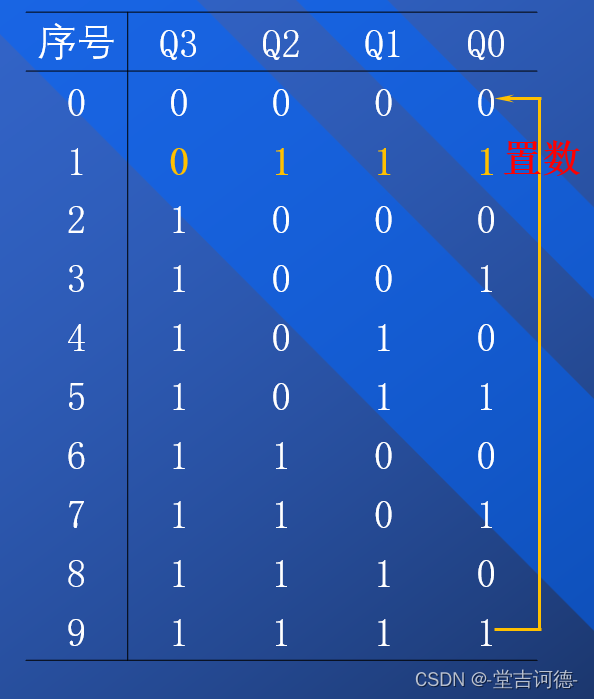

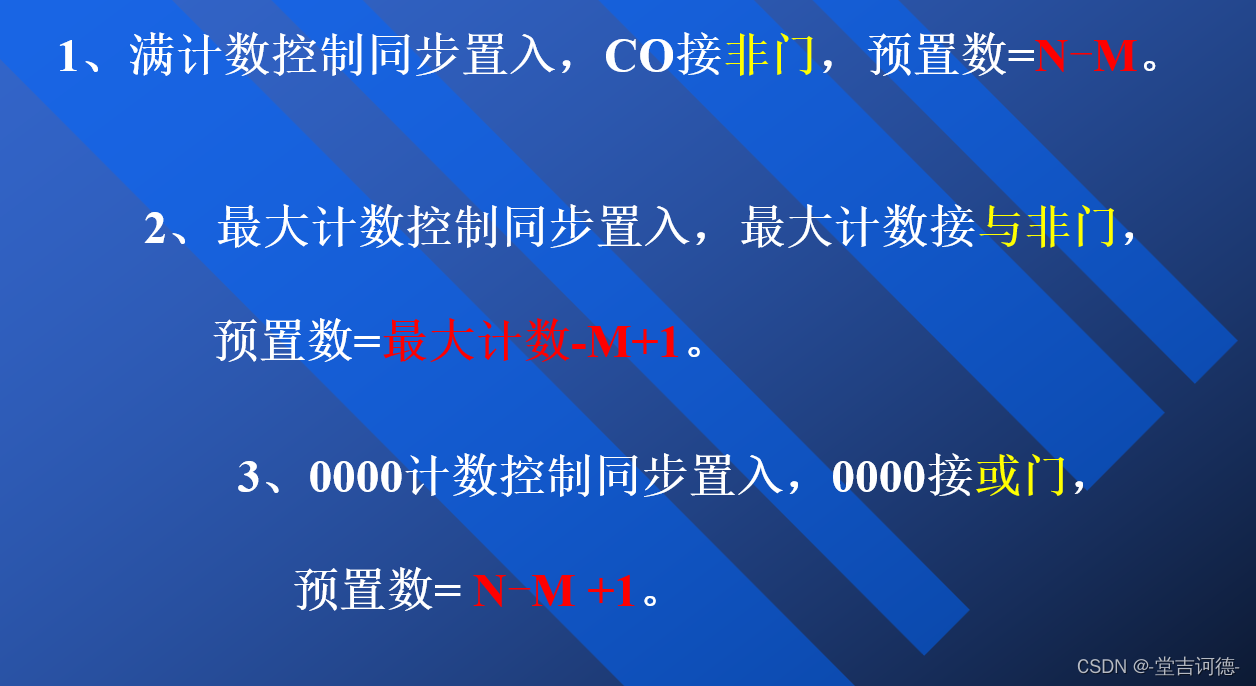

采用中规模集成器件实现任意模值计数(分频)器

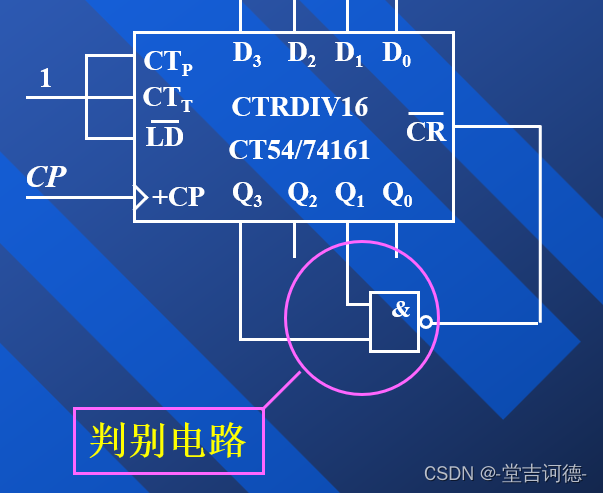

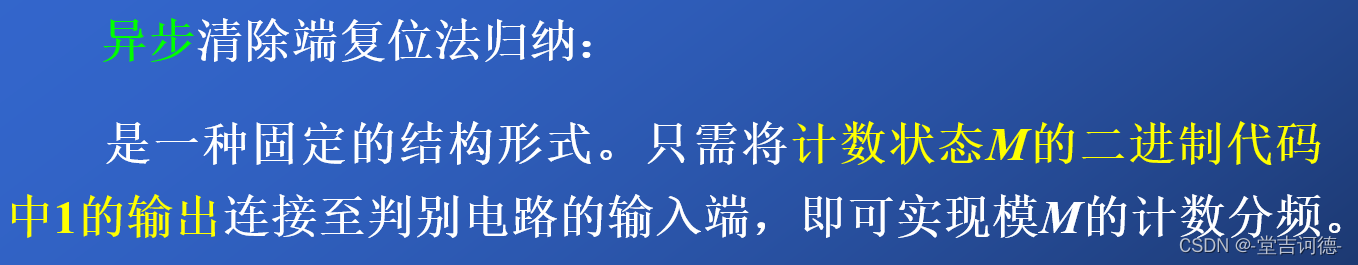

利用异步清除端复位法

利用同步置入控制端的置位法

1、以最大计数作为同步置入控制

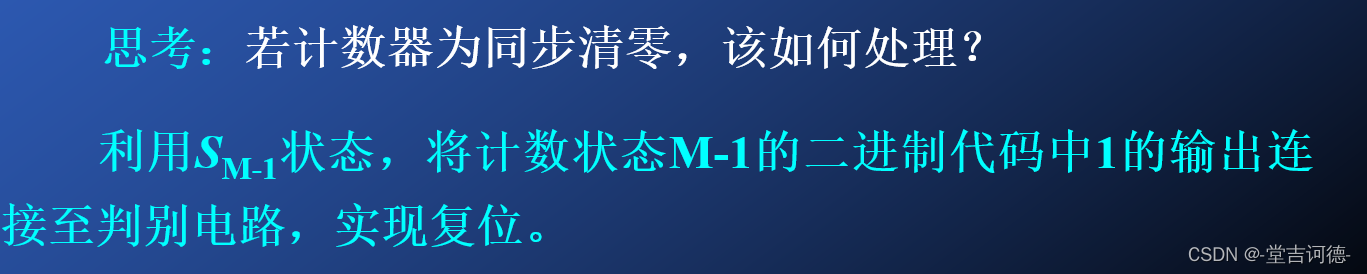

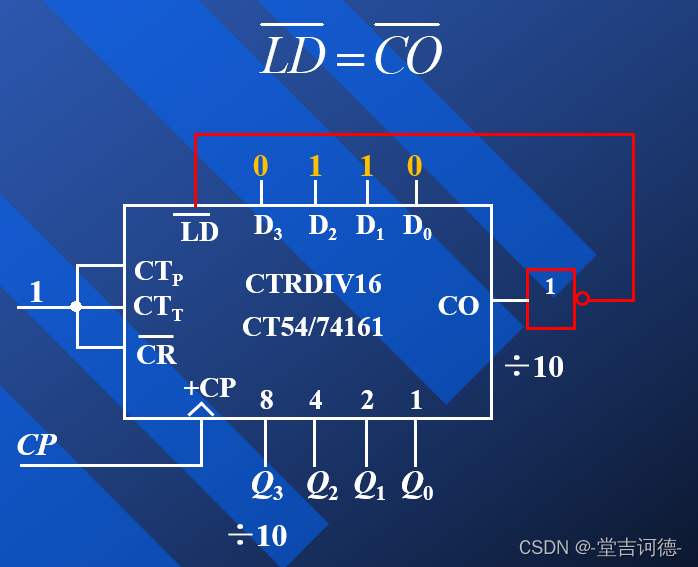

1)以满计数控制同步置入端— CO控制

模值M,预置数D3~D0=N–M,N为最大计数模值

2)以最大计数控制同步置入端—与非门控制

2、以0000状态作为同步置入控制

预置数=N-M+1

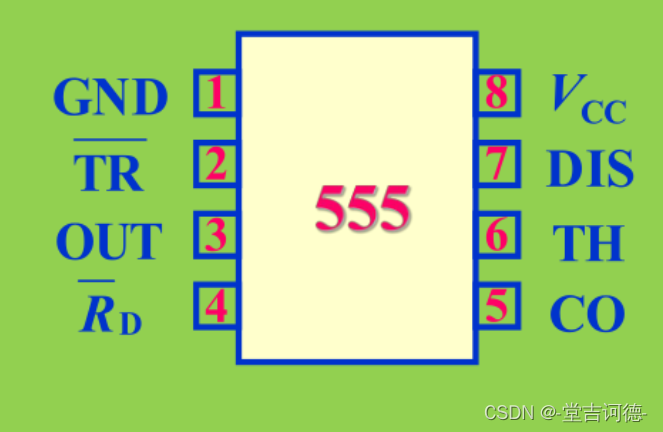

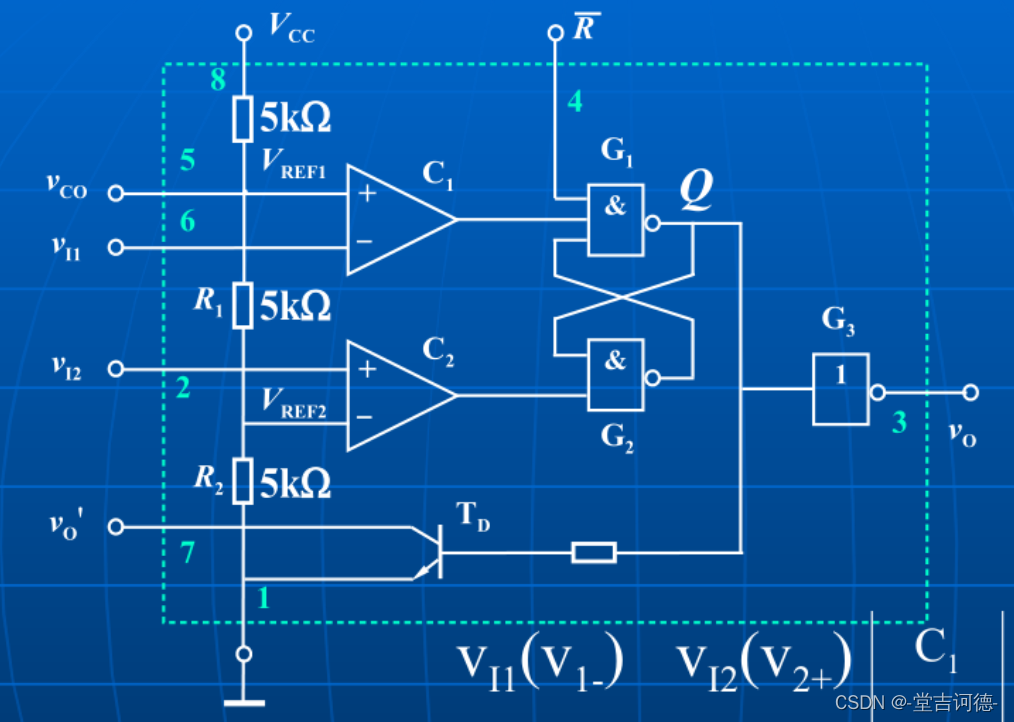

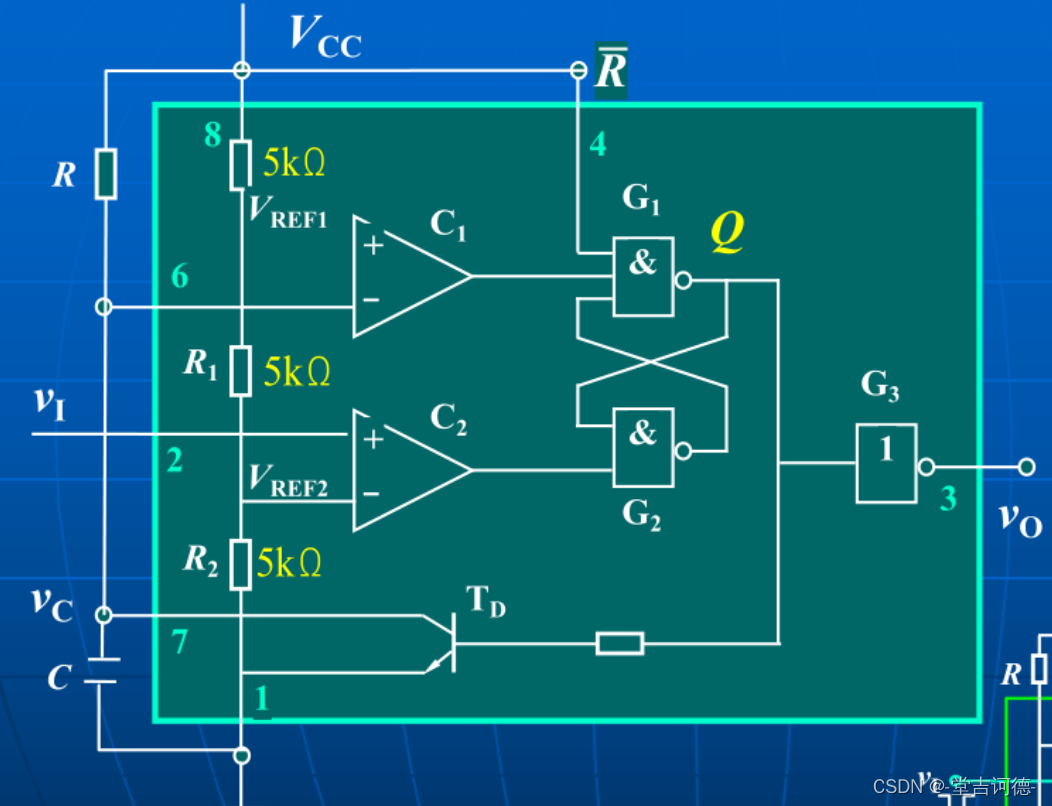

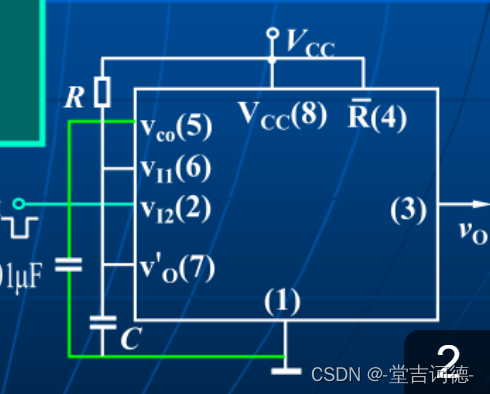

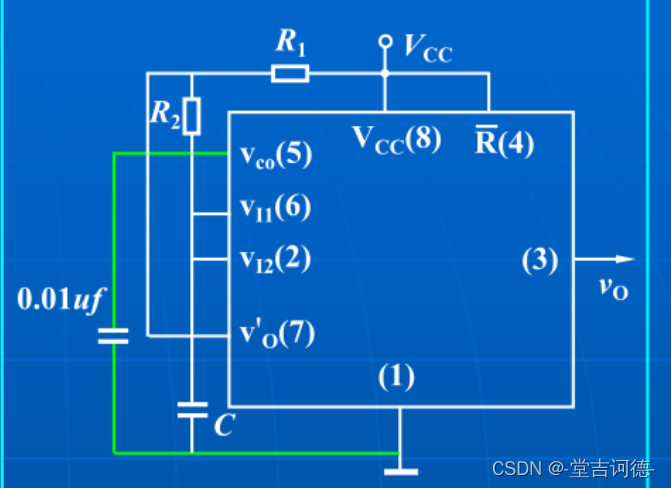

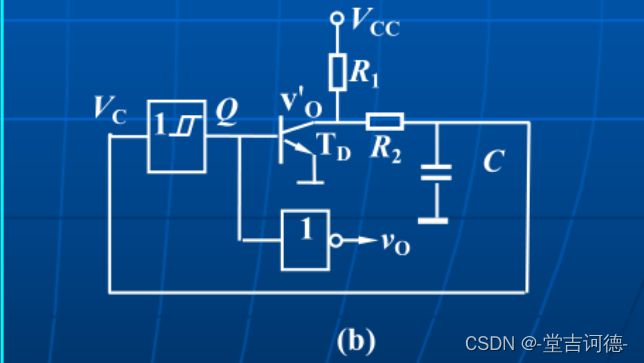

第10章 555定时器

内部结构

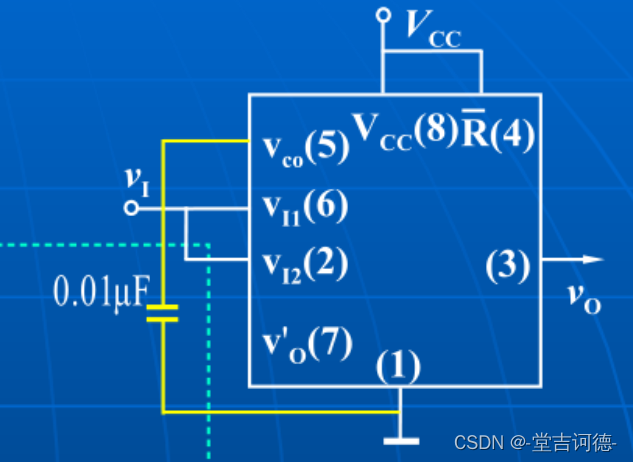

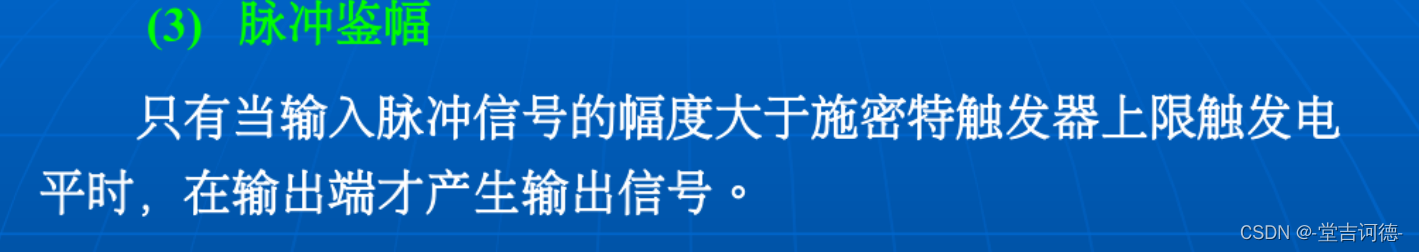

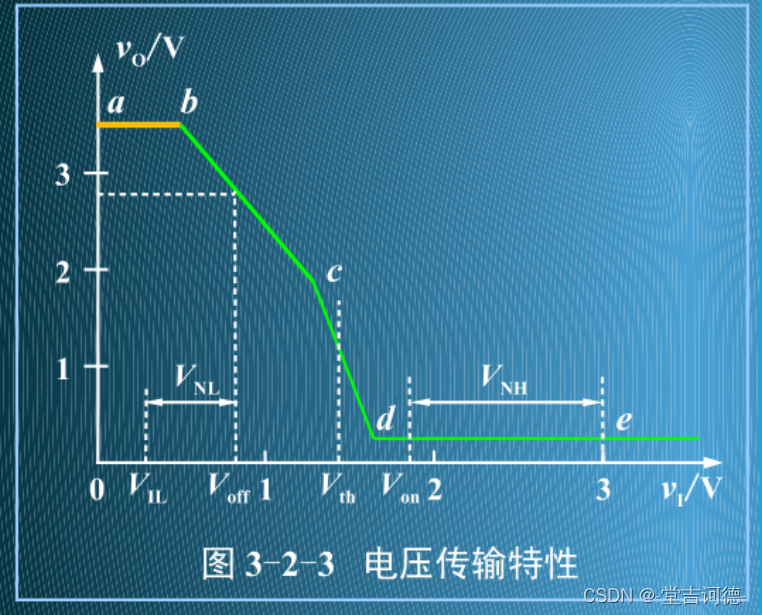

施密特触发器

前者为施密特传输门,后者为施密特反向门。

施密特反向器

用途:

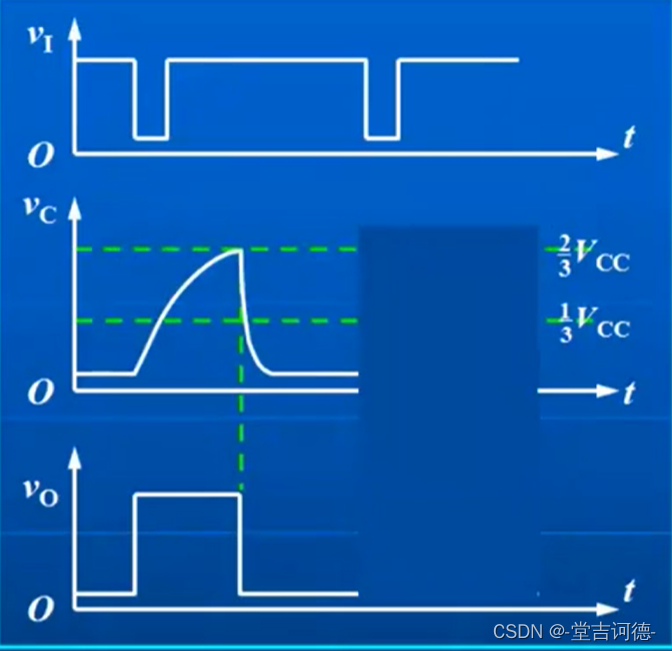

单稳态触发器

输出脉冲宽度tw=1.1RC;

用途:

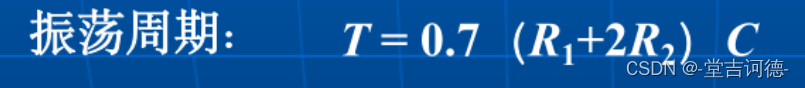

多谐振荡器

充电脉冲宽度:

![]()

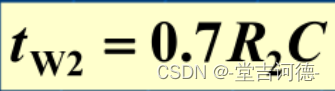

放电脉冲宽度:

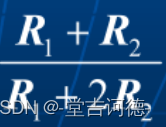

占空比:

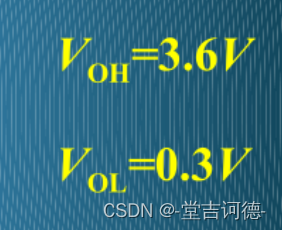

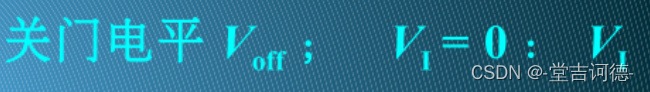

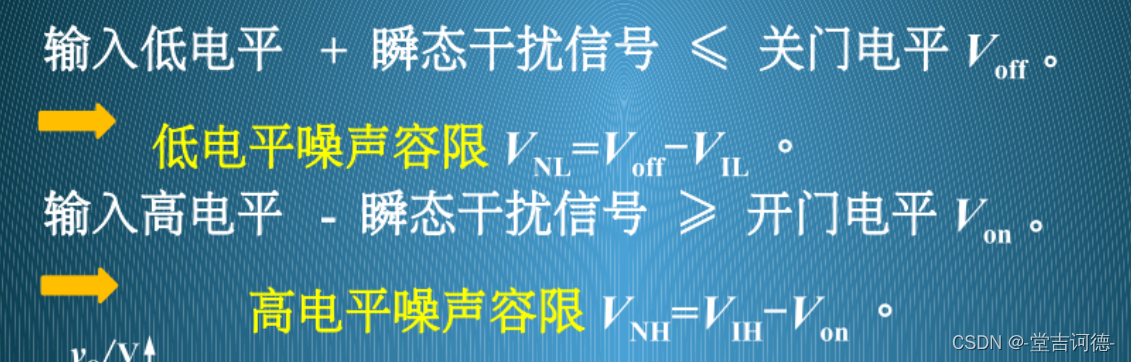

第3章 集成逻辑门

![]()

处于关态:

![]()

处于开态:

![]()

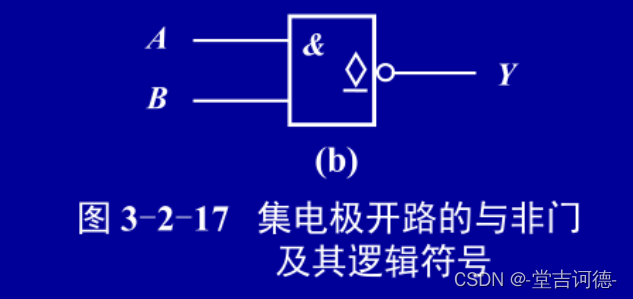

OC门(能实现线与):

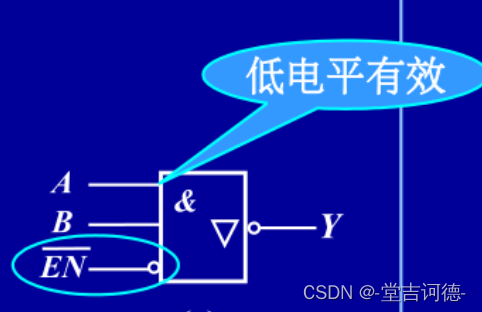

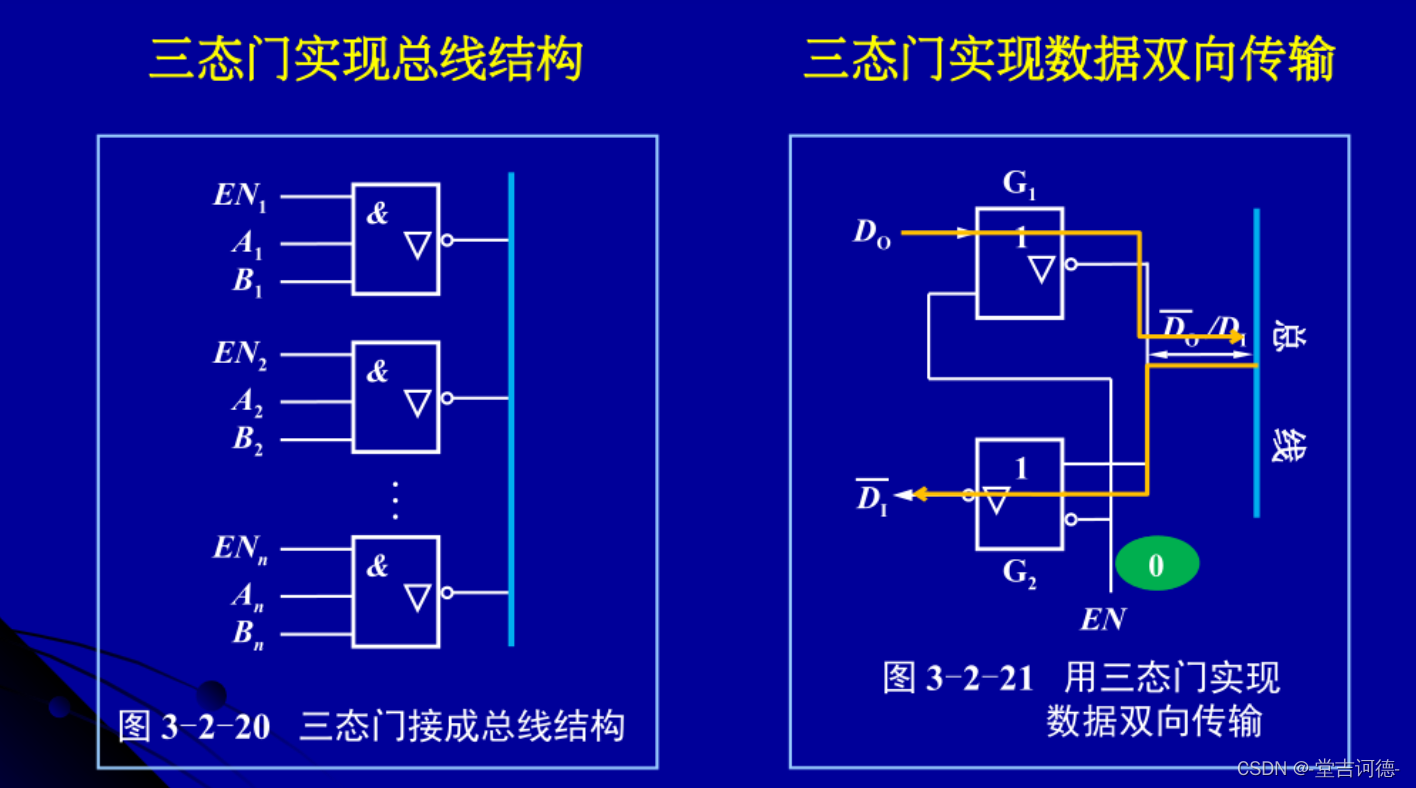

三态门(高阻态):

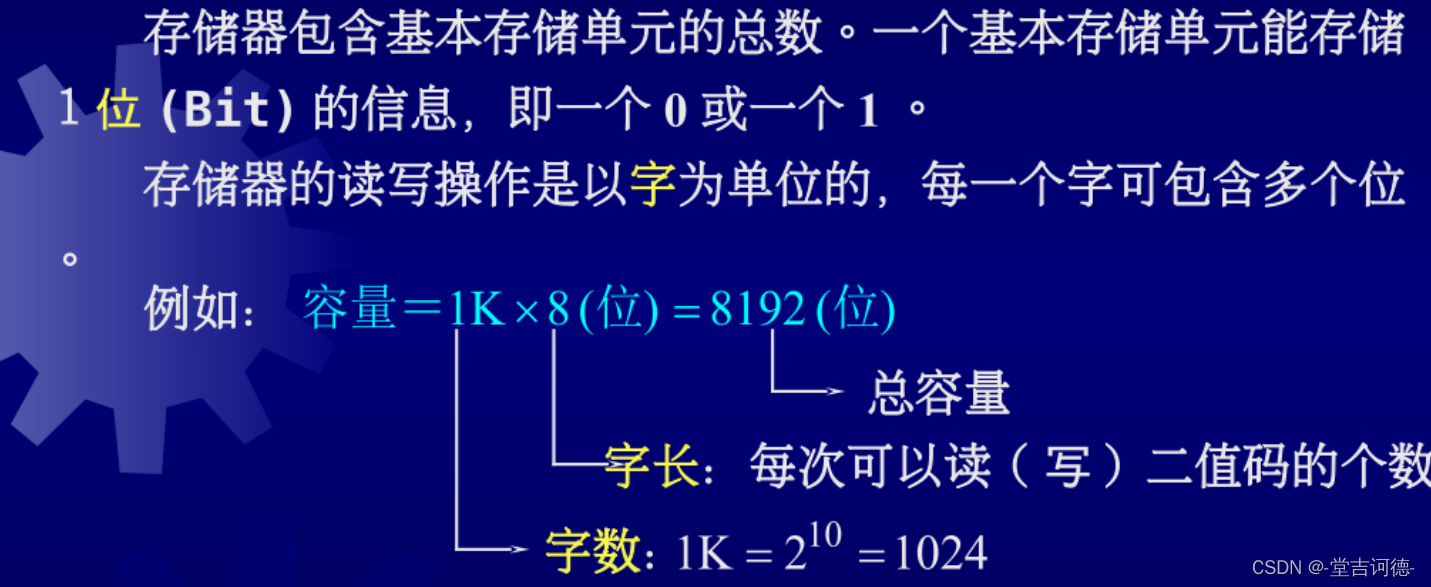

第7章 存储器

一、RAM

存储单元

静态存储单元

动态存储单元

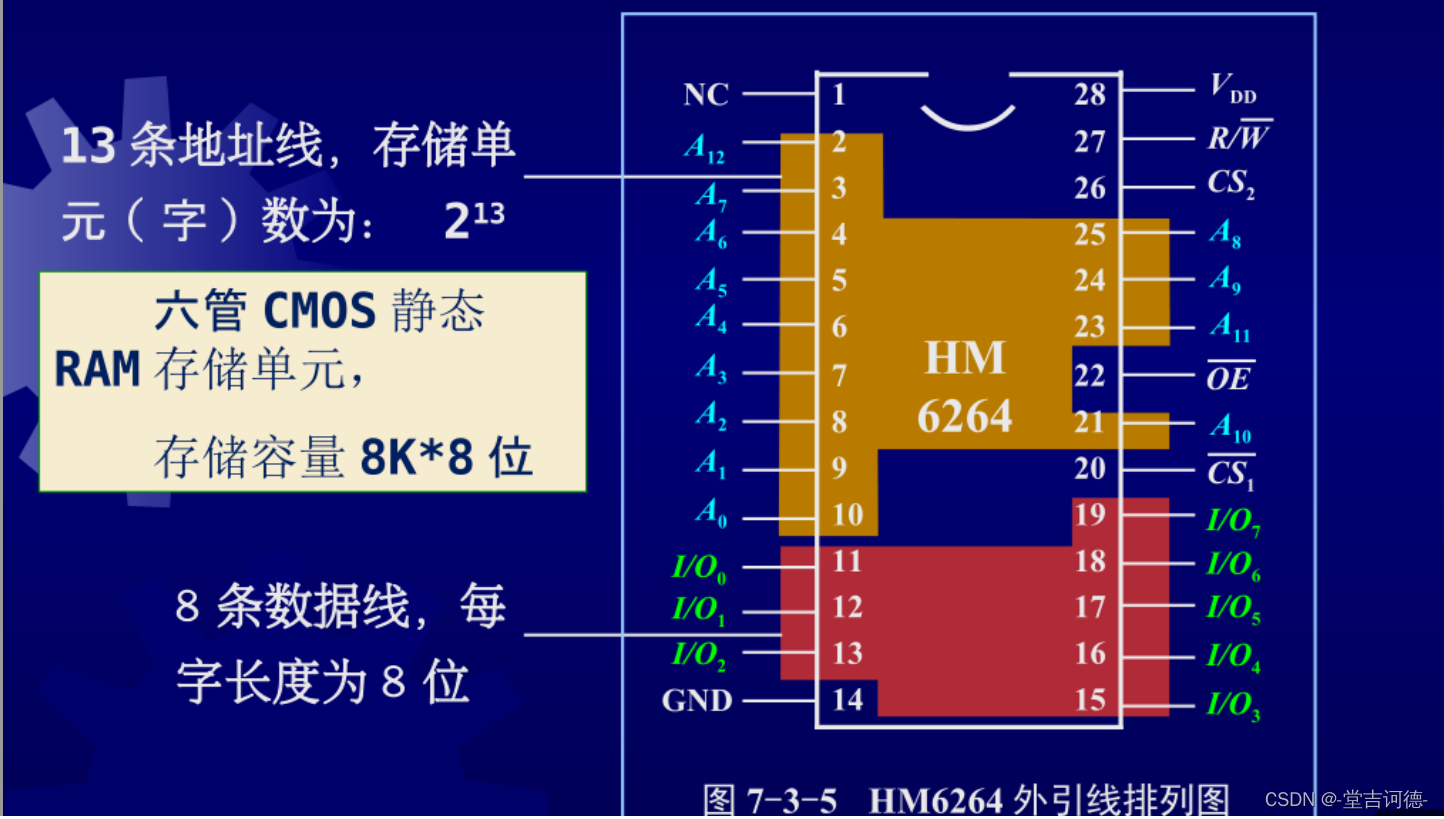

集成芯片

存储扩展

存储扩展

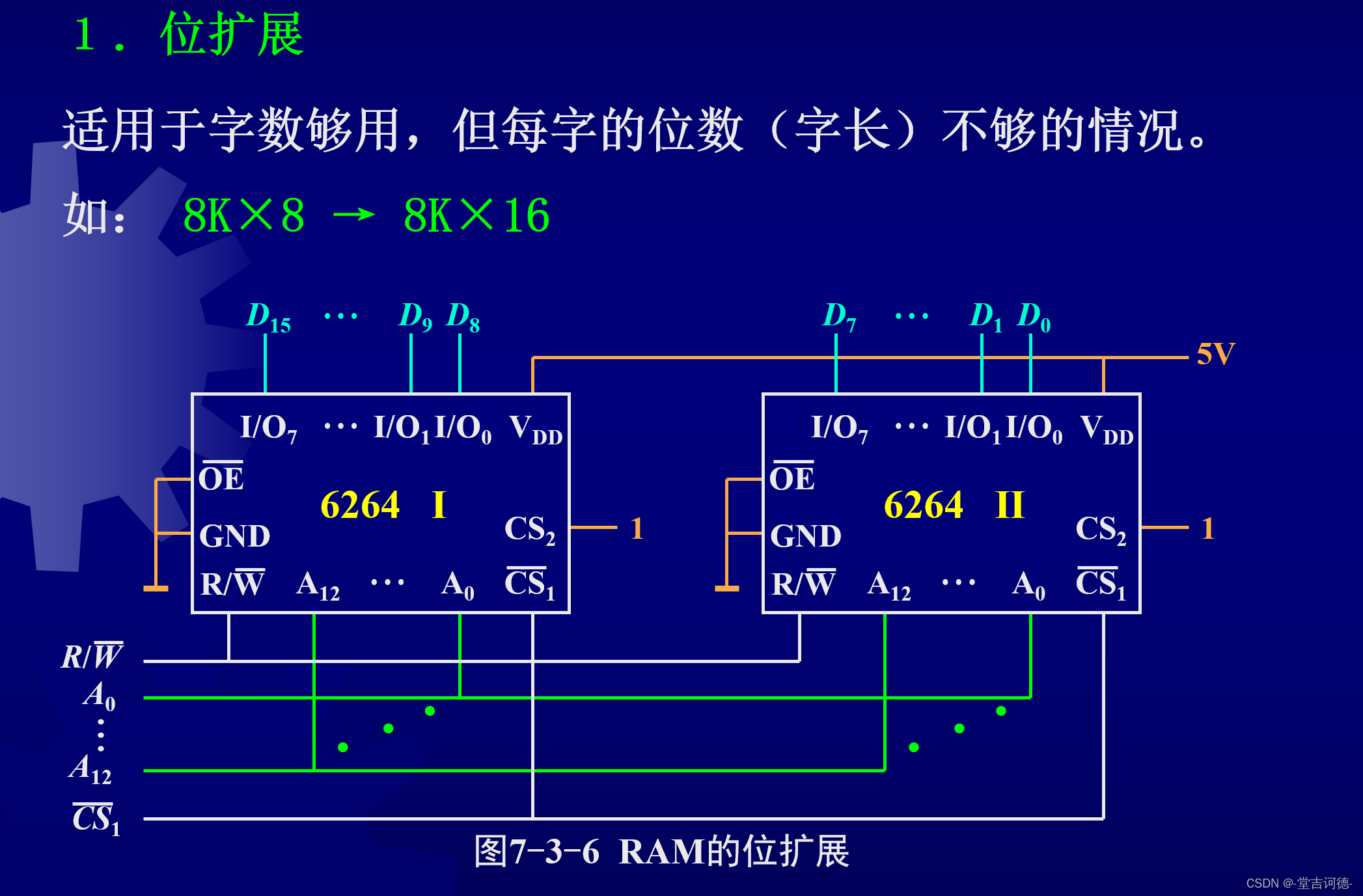

位扩展

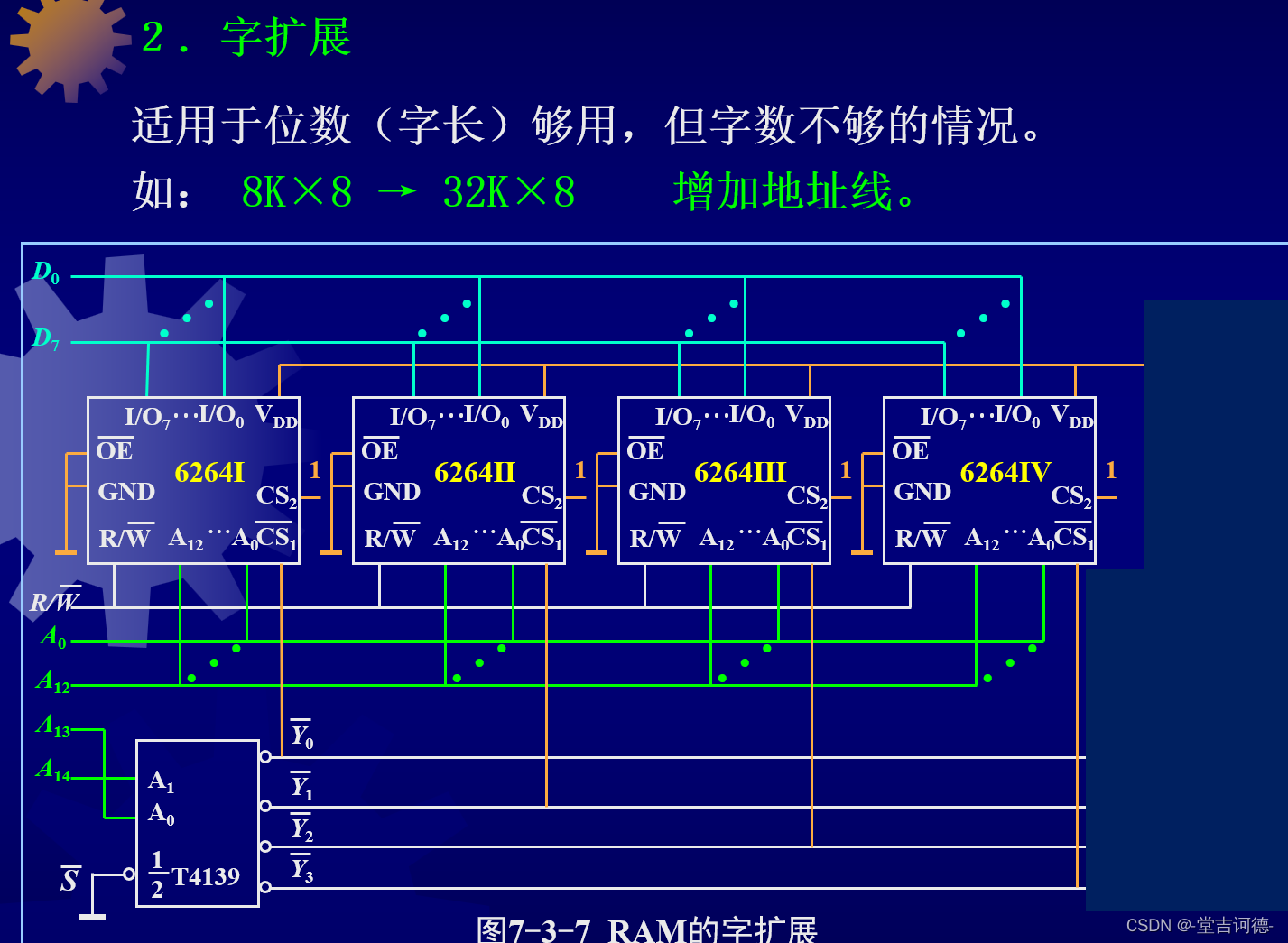

字扩展

二、ROM

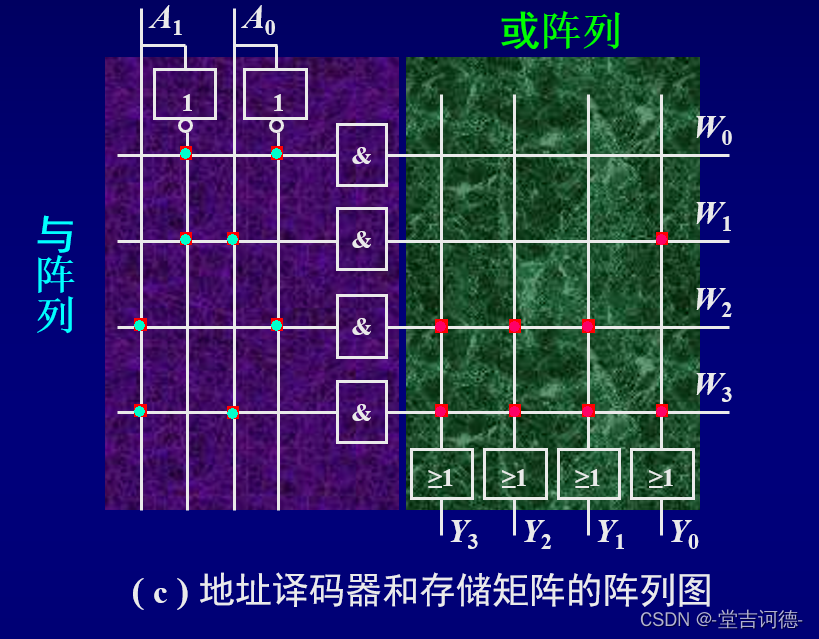

固定ROM(二极管、MOS)

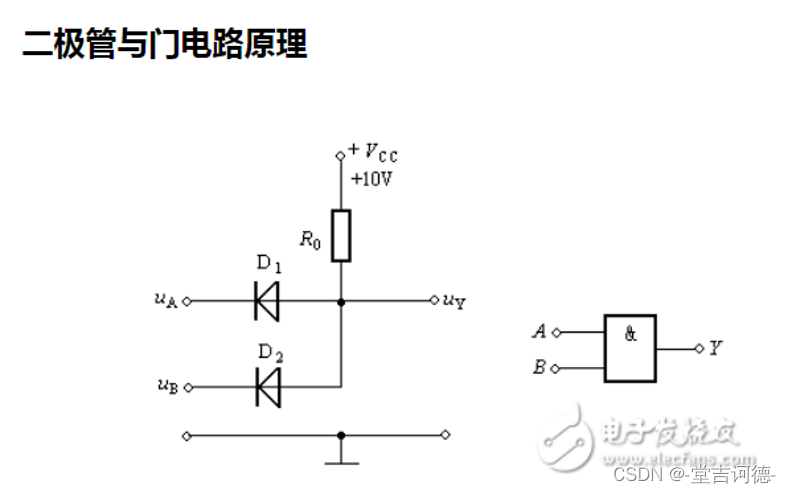

二极管与门

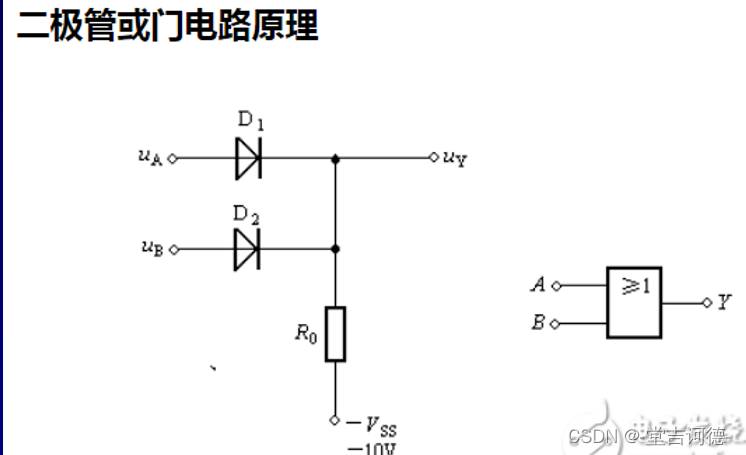

二极管或门

可编程ROM(PROM)

熔丝,一次性编程

可擦除可编程ROM(EPROM)

1、叠层栅注入MOS管(紫外线)

2、电可擦可编程ROM(EEPROM)

3、快闪存储器(Flash Memory)

用ROM实现组合逻辑函数

最小项相或的表达式

本文详细介绍了逻辑函数的简化、组合逻辑电路中的全加器、编码器与译码器、数值比较器、数据选择器以及不同类型的触发器,包括钟控、主从和边沿触发,还探讨了时序逻辑电路如寄存器、移位寄存器和计数器的设计方法。最后,涉及555定时器的内部结构和其在电路中的应用。

本文详细介绍了逻辑函数的简化、组合逻辑电路中的全加器、编码器与译码器、数值比较器、数据选择器以及不同类型的触发器,包括钟控、主从和边沿触发,还探讨了时序逻辑电路如寄存器、移位寄存器和计数器的设计方法。最后,涉及555定时器的内部结构和其在电路中的应用。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?