三、集成逻辑门器件

3.1 概述

- 门电路:用来实现逻辑关系的电子电路

- 门电路分类(按采用的半导体器件进行分类):

- 分立元件门电路

- 集成门电路 { 双极型集成门(DTL、TTL) 和 MOS集成门(NMOS、PMOS、CMOS)}

- 逻辑电平:高电平(“1”)2.4V~5V

和 低电平(“0”)0V~0.8V

3.2 半导体元件的开关特性

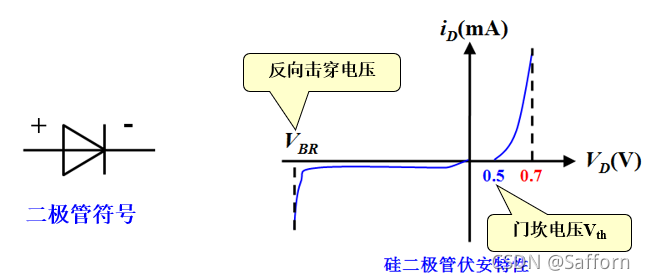

1. 半导体二极管

- 伏安特性

- 单向导电性

- 外加正向电压(大于Vth=0.5(硅)),二极管导通,此时二极管两端存在压差 0.7V

- 外加反向电压,二极管截止

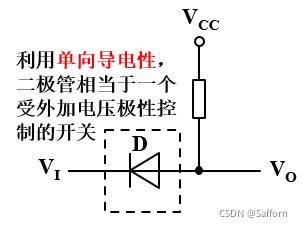

- 开关特性

假定:VCC端接+5V电源,VIH=VCC,VIL=0

当VI=VIH(=VCC) 输入高电平时,二极管D截止,VO = VCC 输出高电平 —— 相当于开关断开

当VI=VIL(=0V) 输入低电平时,二极管D导通,VO端 受VI的低电平和二极管压差限制,VO = 0.7V 输出低电平 —— 相当于开关闭合

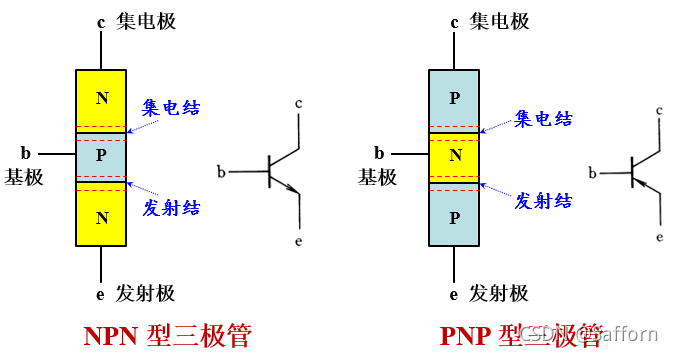

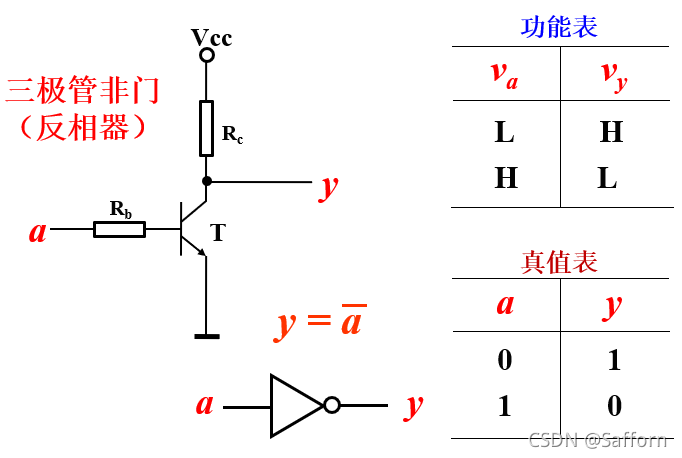

2. 半导体三极管

- 物理结构:因有电子和空穴两种载流子参与导电,也称为双极型三极管

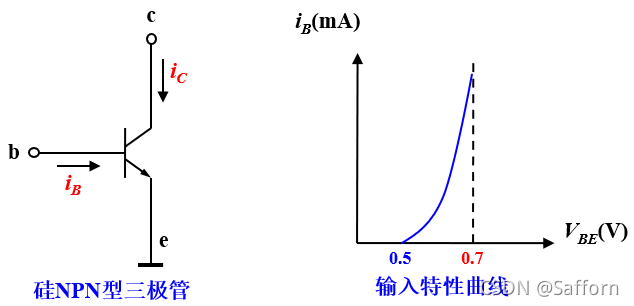

- 输入特性

- 通过b,e间的电流 iB 控制集电极电流 iC实现其电路功能

- VT(阈值电压)= 0.5V

- 输出特性

- 饱和区:发射结、集电极均正偏( vbe>VT(=0.5V)、vbc>VT(=0.5V))深度饱和状态下,c,e两极压差为 VCES = 0.2V

- 截止区:发射结、集电极均反偏(vbe<0V,vbc<0V);vbe<0.7V时, ib ≈ 0mA,ic ≈ 0mA,三极管截止

- 放大区:发射结正偏,集电结反偏(vbe>VT,vbc<0)起放大作用,ic = β*ib (属于模电内容)

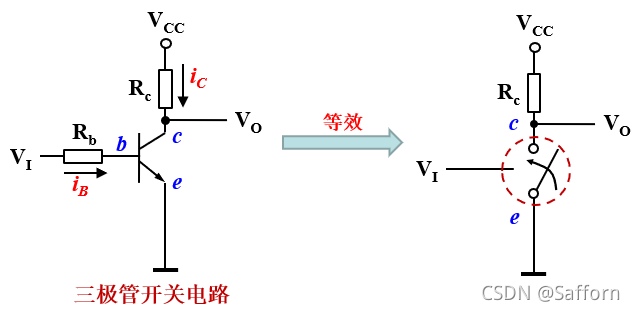

- 开关特性

假定:VCC端接+5V电源,VIH=VCC,VIL=0

当VI=VIH(=VCC) 输入高电平时,三极管深度饱和,VO = VCES 输出低电平 —— 相当于开关闭合

当VI=VIL(=0V) 输入低电平时,三极管截止,VO = VCC 输出高电平 —— 相当于开关截止

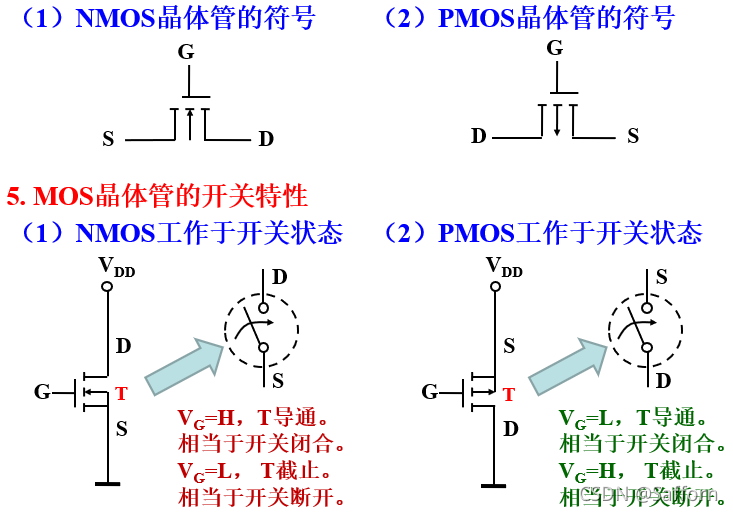

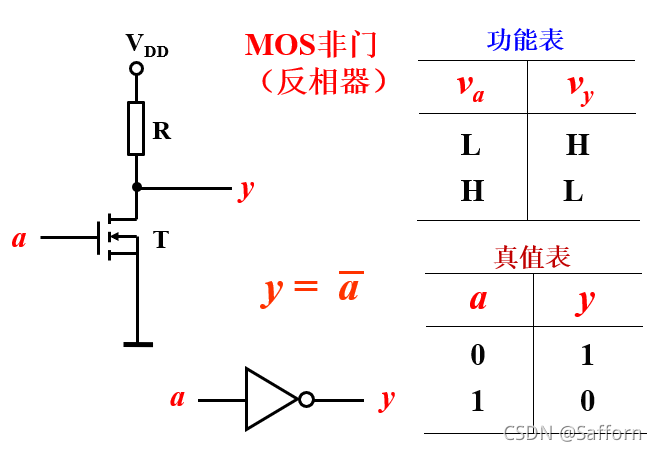

3. MOS场效应管

-

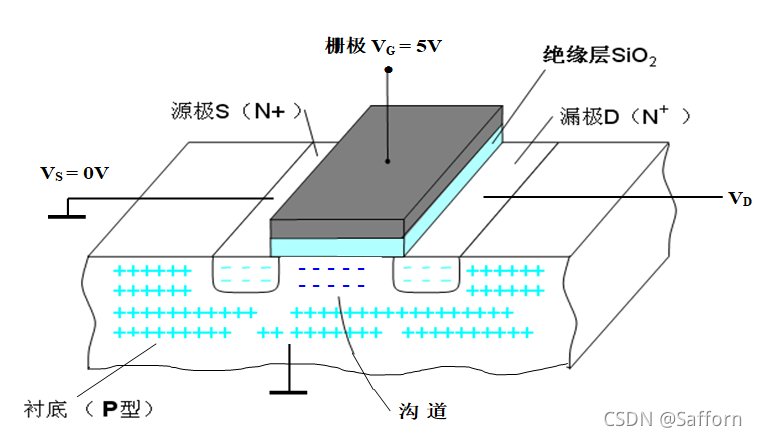

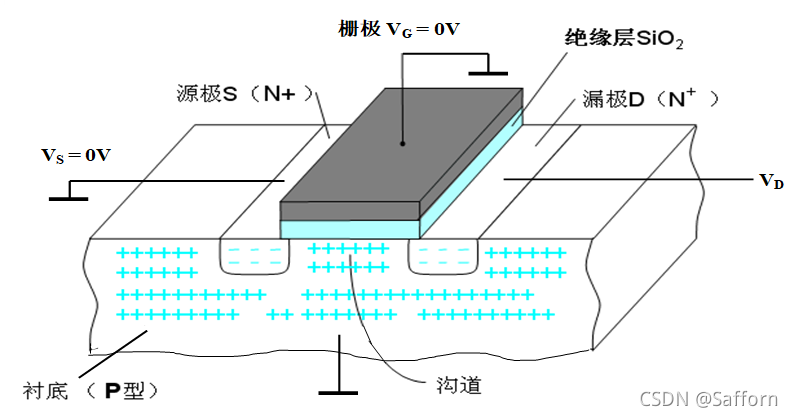

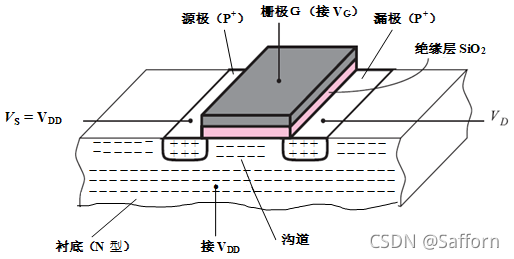

MOS物理结构:Metal - Oxide - Semiconductor(N/P) (金属-氧化物-N/P型半导体)

-

NMOS工作原理

VGS = 5V时,形成N型导电沟道,NMOS管导通

VGS = 0V时,不形成导电沟道,NMOS管截止 -

PMOS工作原理

VGS = 0V时,形成P型导电沟道,PMOS管导通

VGS = 5V时,不形成导电沟道,PMOS管截止

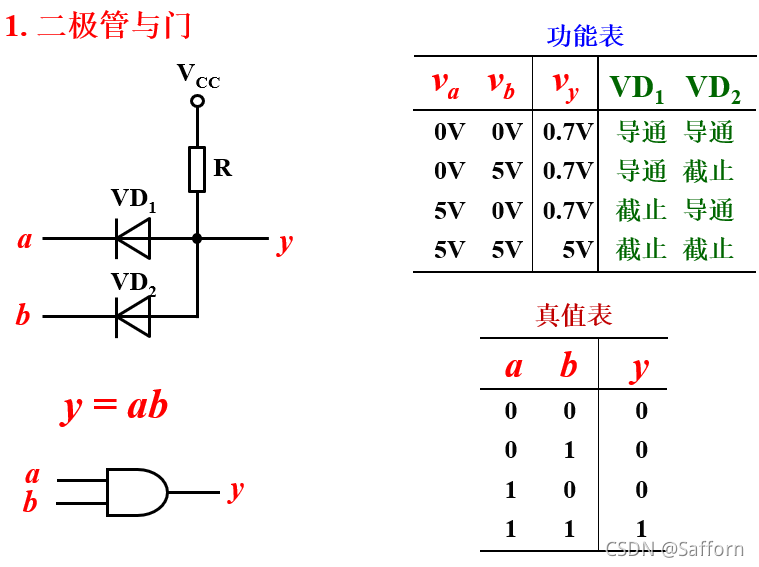

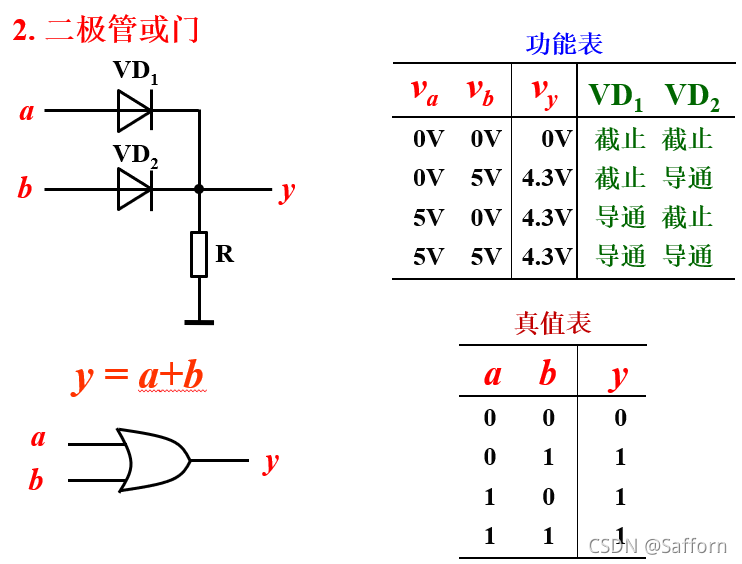

3.3 分立元件门电路

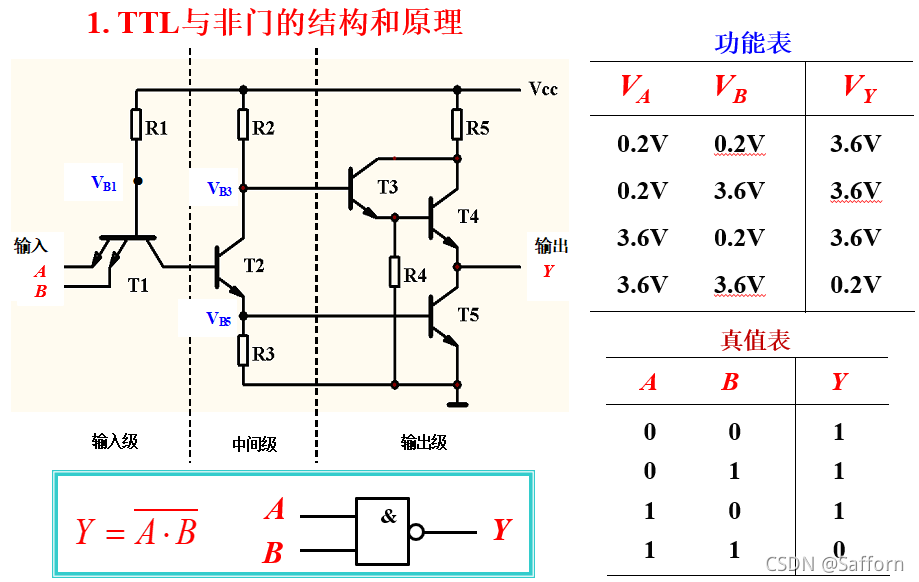

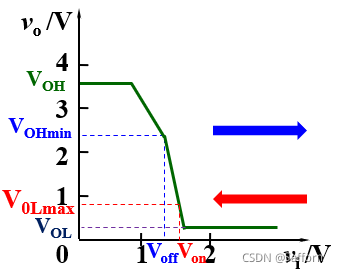

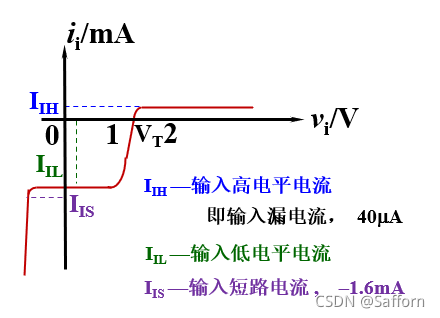

TTL的电压传输特性:

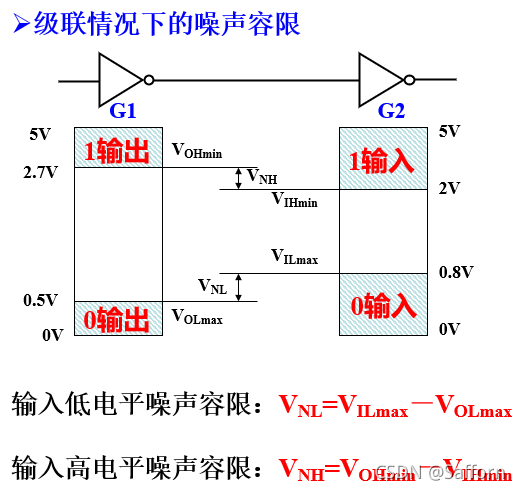

- Voff(关门电平):输出高电平达到最小值(VOHmin = 2.4V)时对应的输入电压,即输入低电平的最大值 VILmax

- Von(开门电平):输出低电平达到最大值(VOLmax = 0.8V)时对应的输入电压,即输入高电平的最小值 VIHmin

- VT(阈值电压 / 门槛电压)= 1.4V

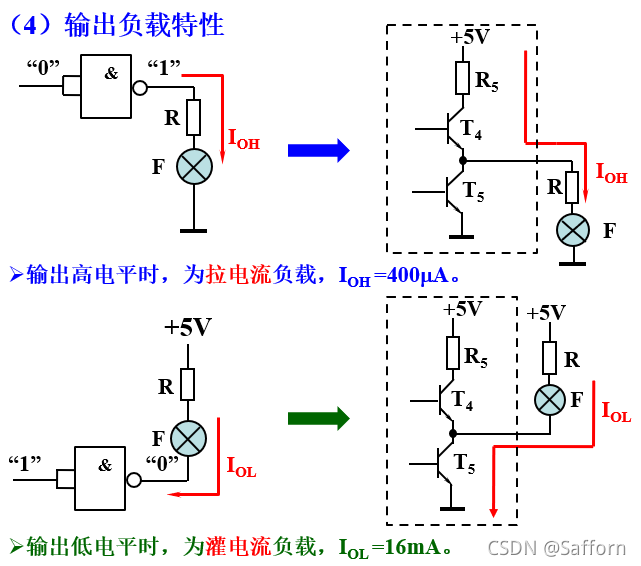

- 拉电流:电流方向与TTL逻辑门输出方向相同

- 灌电流:电流方向与TTL门输出方向相反

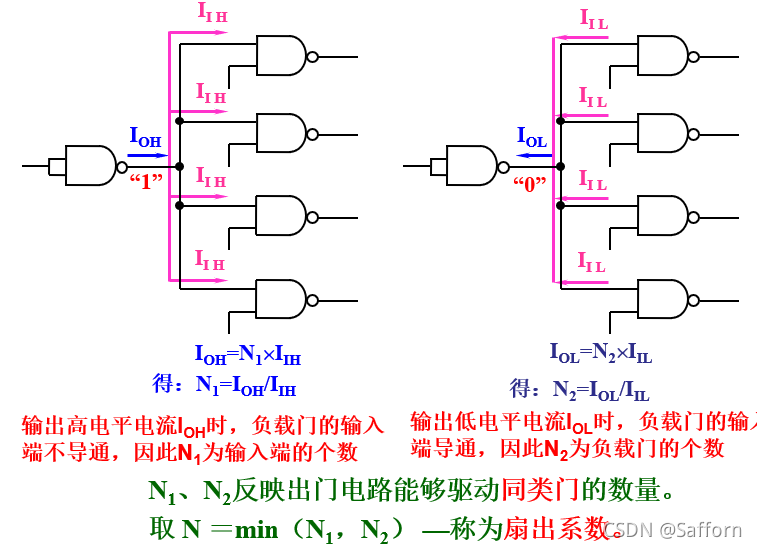

- 扇出系数:min(N1,N2) 反应 门电路能够驱动同类门的数量

- 噪声容限:为保证电路可靠工作,应对干扰的幅度有一定的限制

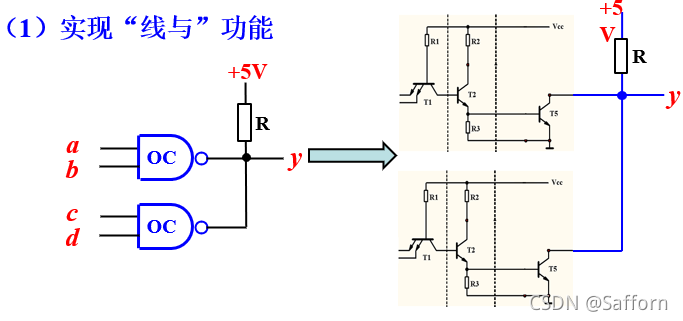

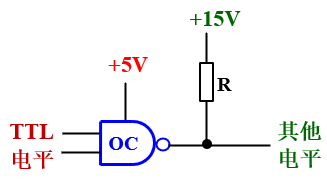

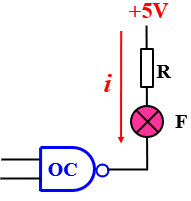

OC门

- 工作时需要外接上拉电阻和电源

OC门的应用 - 实现 “线与” 功能

- 电平转换

- 驱动电流型负载

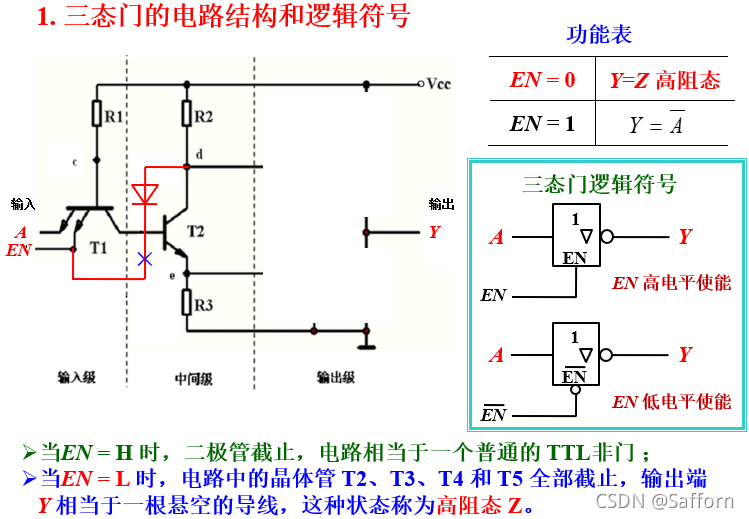

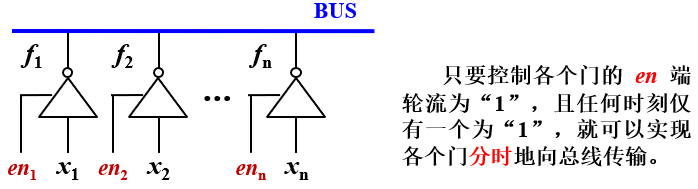

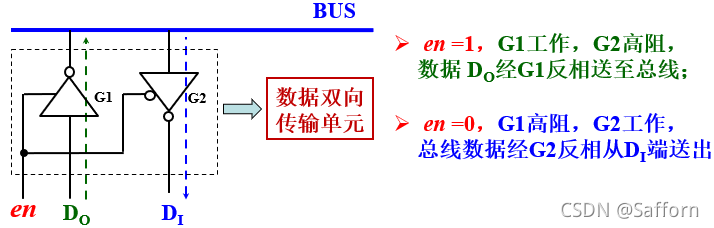

TS门(三态输出门电路)

- TS门的应用:

- 构建数据总线

- 构建数据总线

- 实现数据双向传输

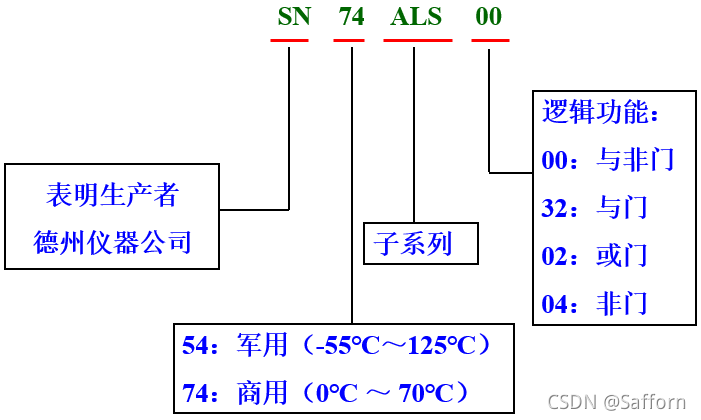

- TTL门电路命名方式

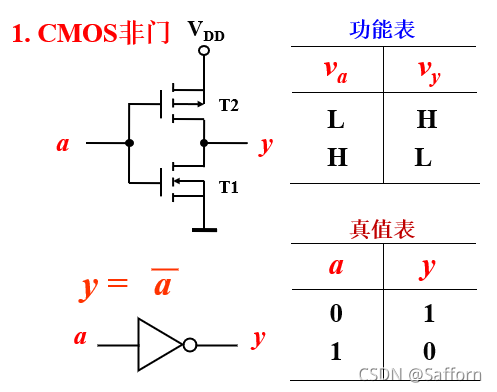

CMOS逻辑门电路

- CMOS反相器的抗干扰能力强

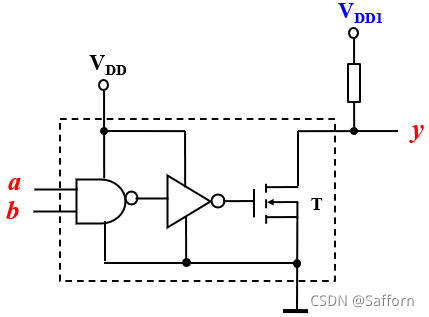

OD门(漏极开路CMOS门电路)

- 需要外接上拉电阻

- 输出端可以并接,实现 “线与” 功能

- 电平转换 (以上特点和应用与OC门类似)

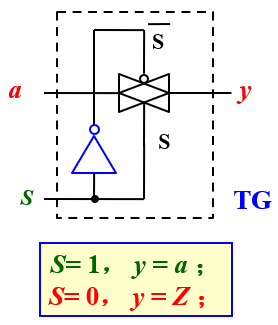

TG门(CMOS传输门)

- 当S = H 时,TI、T2均导通,y = a ,实现传输

- 当S = L 时,T1、T2全部截止,输出端 y 呈现高阻态(Z)

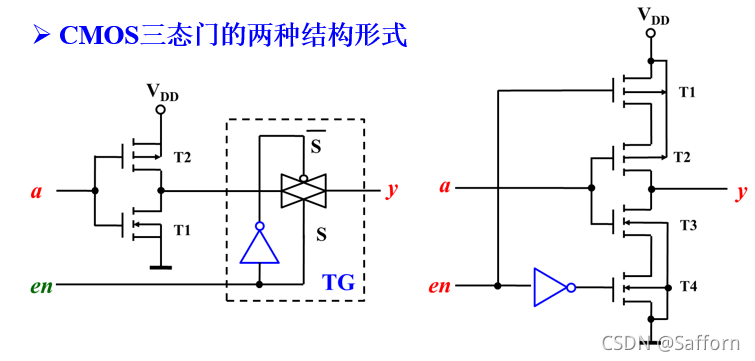

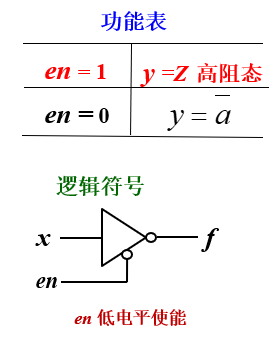

CMOS三态门

- 当en = H 时,传输门TG导通,相当于一个普通的 CMOS 非门

- 当en = L 时,传输门TG截止,输出端 呈现高阻态

CMOS门电路系列:

- HCT:与TTL兼容的高速CMOS

- HC:高速CMOS

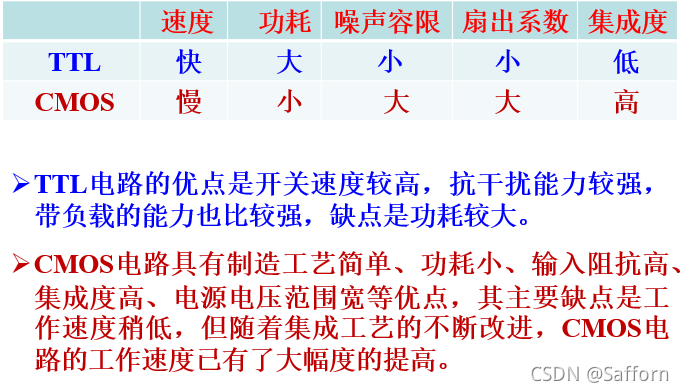

TTL 与 CMOS 门电路性能对比

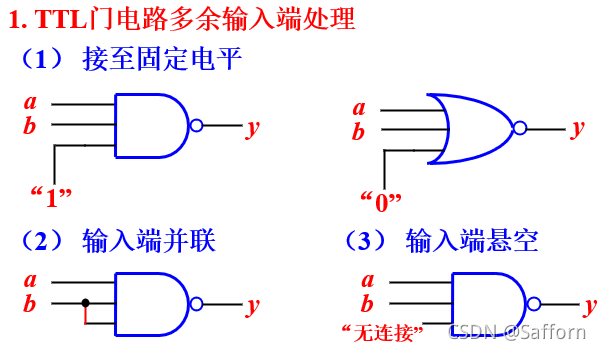

门电路多余输入端处理方法

2. CMOS门电路多余输入端处理

(1)可接固定电平 “0” / “1” 或 输入端并联

(2)多余输入端不能悬空

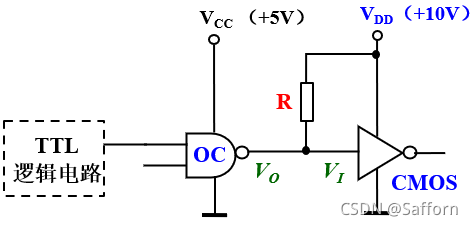

TTL 与 CMOS 电路的接口

-

TTL门电路 不能直接驱动 CMOS门电路

解决方案:- 在TTL门电路的输出端接 上拉电阻,R不是特别大

- 通过OC门进行电平转换

- 采用74HCT系列CMOS门电路(兼容)

-

用CMOS门电路可以直接驱动较少数量的TTL门电路

四、组合逻辑电路

4.1 概述

- 数字电路按其完成逻辑功能的不同特点,可以划分为 组合逻辑电路 和 时序逻辑电路 两大类

- 组合逻辑电路:电路无记忆功能,不存在反馈路径

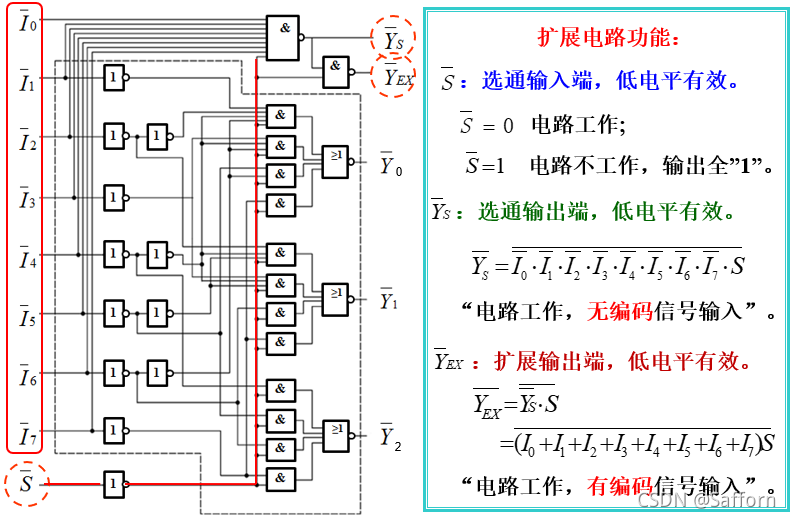

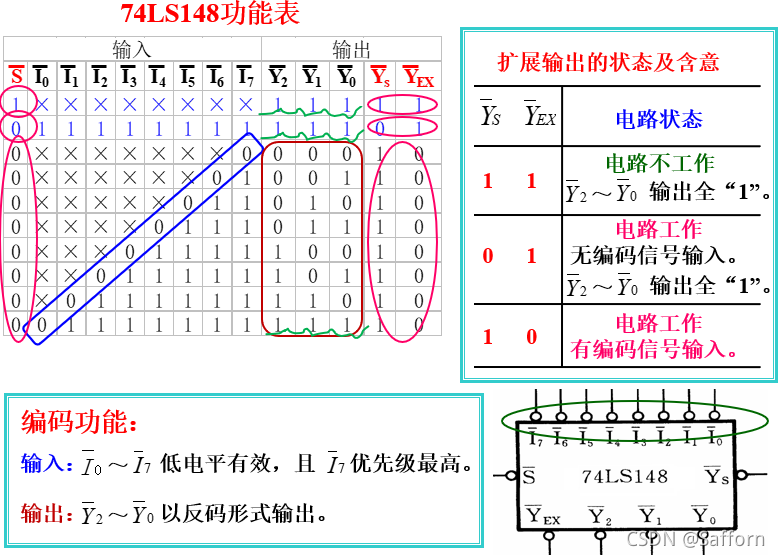

4.3 编码器

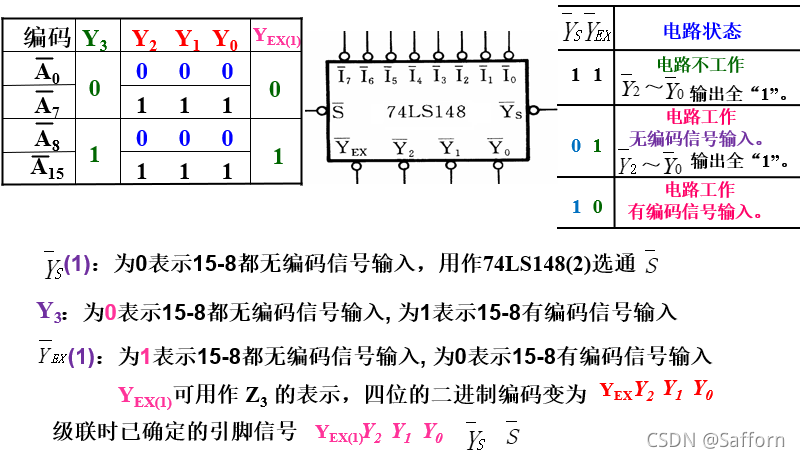

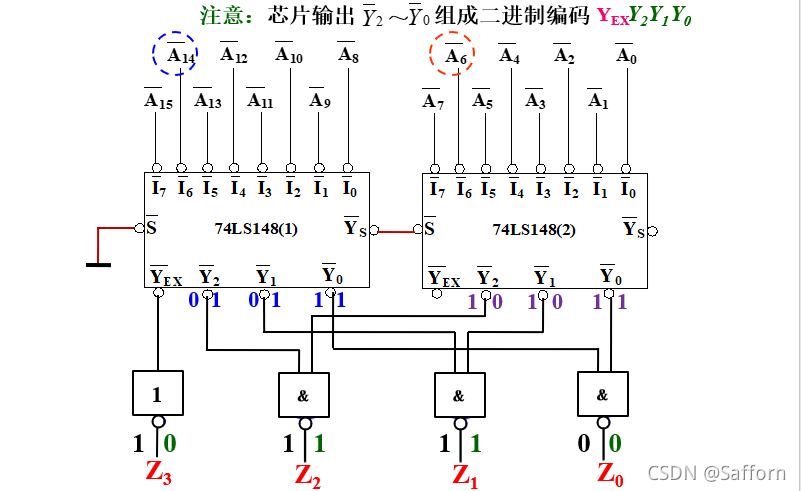

74LS148(8线-3线优先编码器)

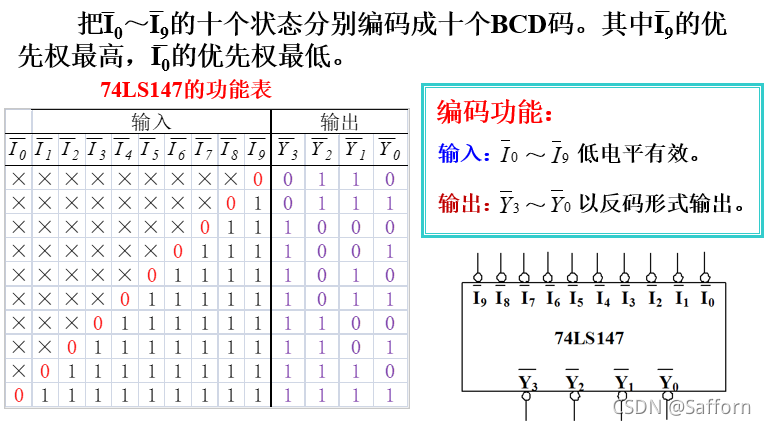

74LS147(二-十进制优先编码器)

4.4 译码器

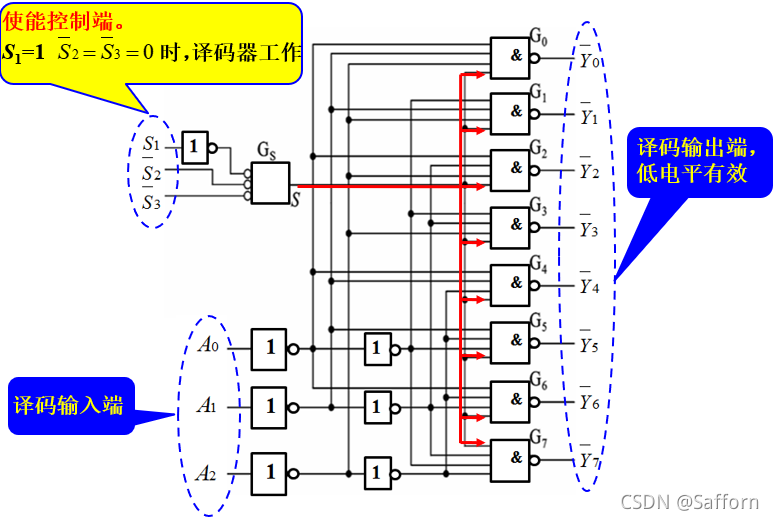

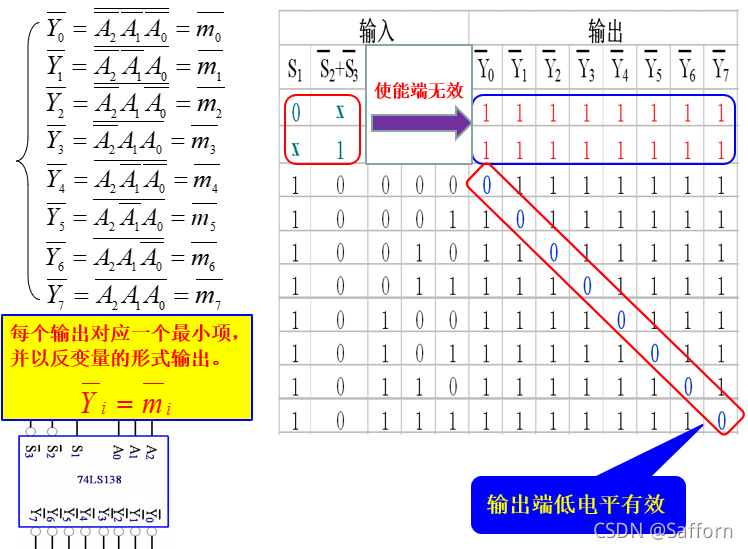

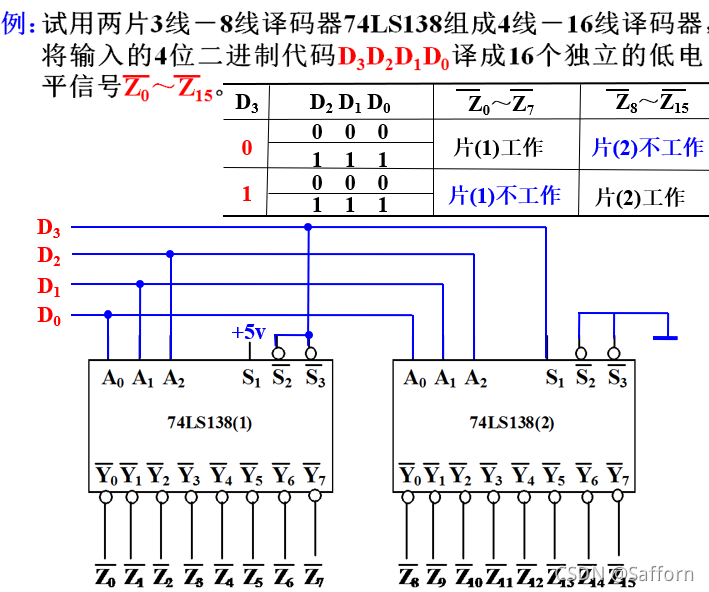

74LS138(3线-8线译码器)

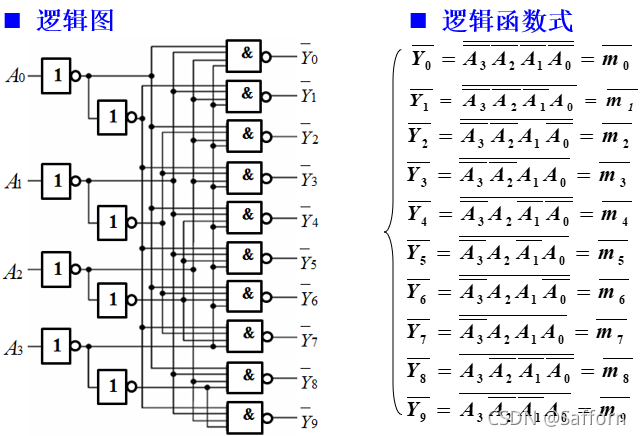

二-十进制译码器(BCD / 4线-10线)

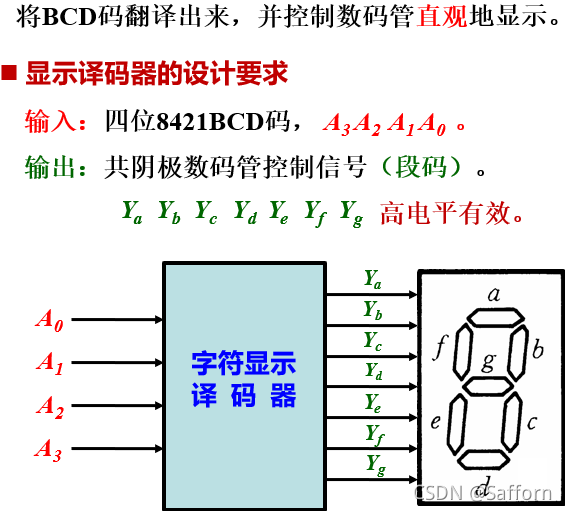

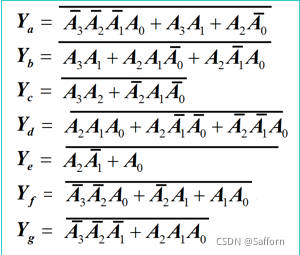

74LS48(BCD-共阴极七段字符显示译码器)

4.5 数据选择器

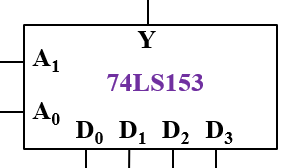

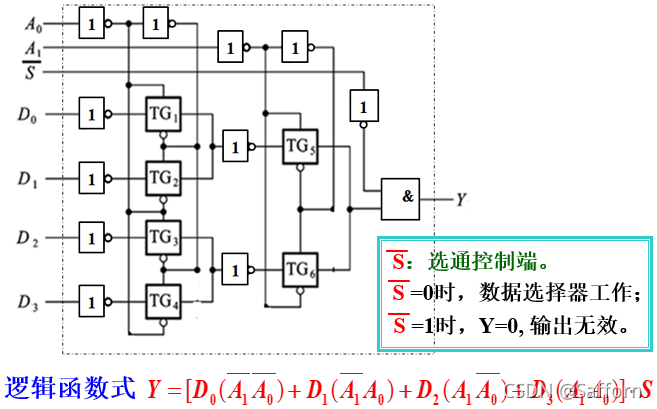

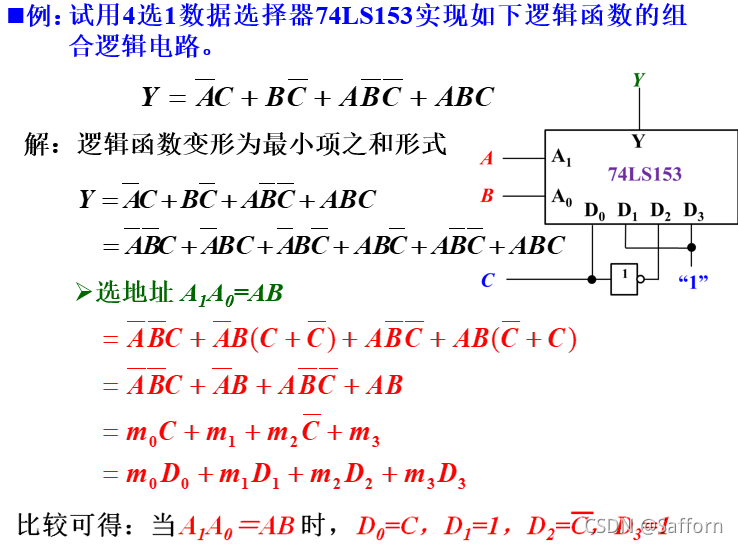

74HC153(双4选1数据选择器)

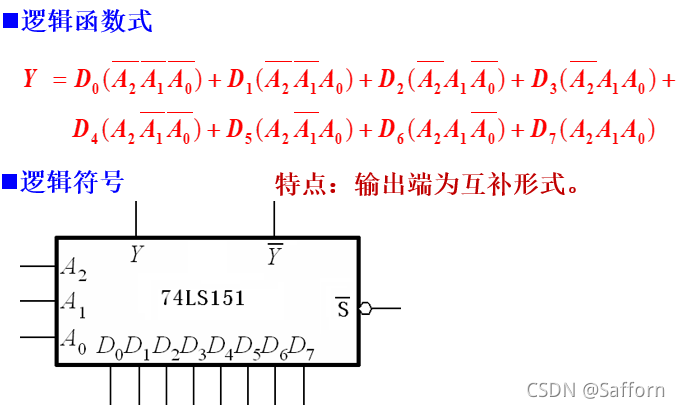

74LS151(8选1数据选择器)

4.6 加法器

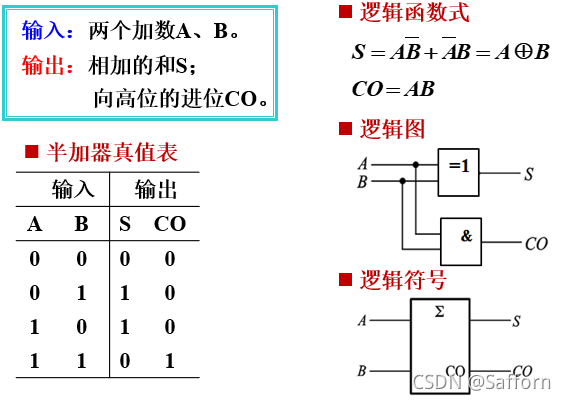

半加器

不考虑低位进位,将两个1位二进制数A和B相加

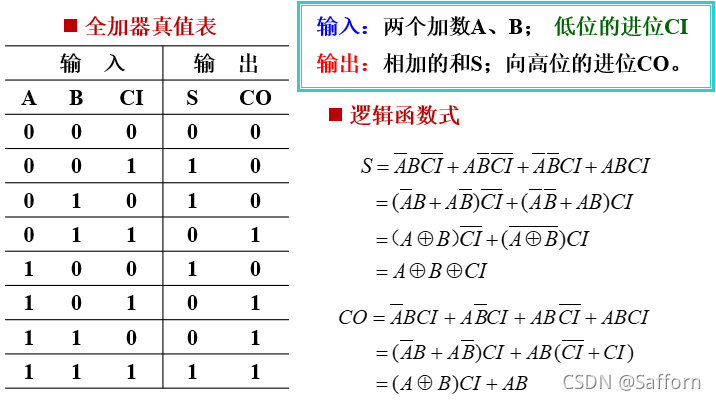

全加器

考虑低位进位,将两个加数和低位进位一起相加

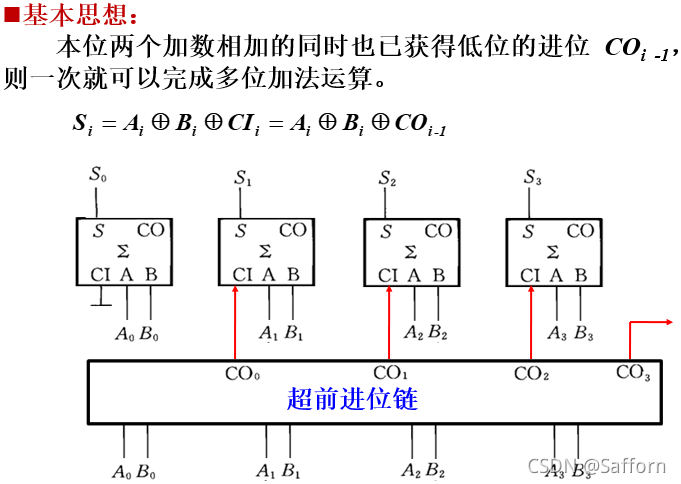

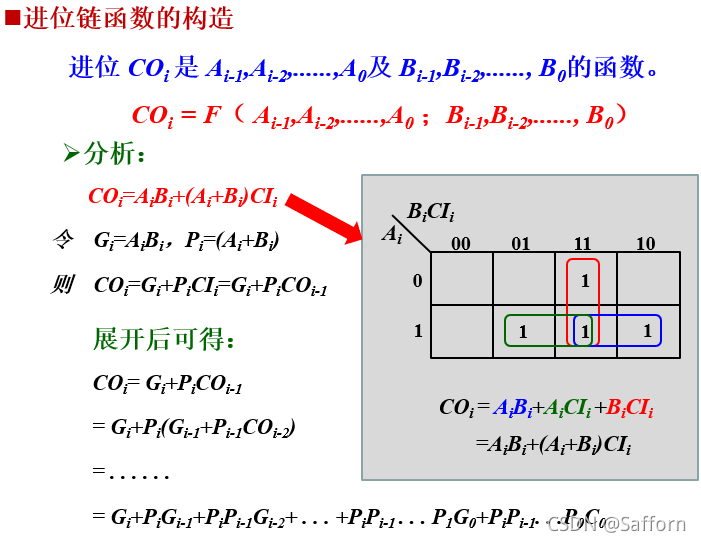

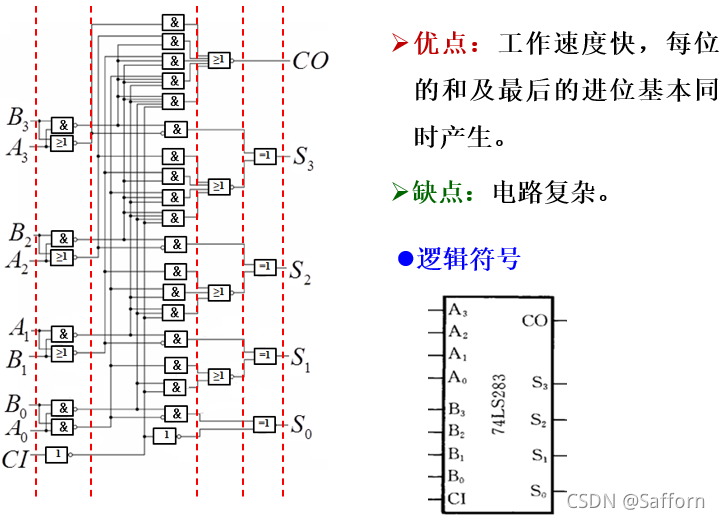

- 超前进位加法器

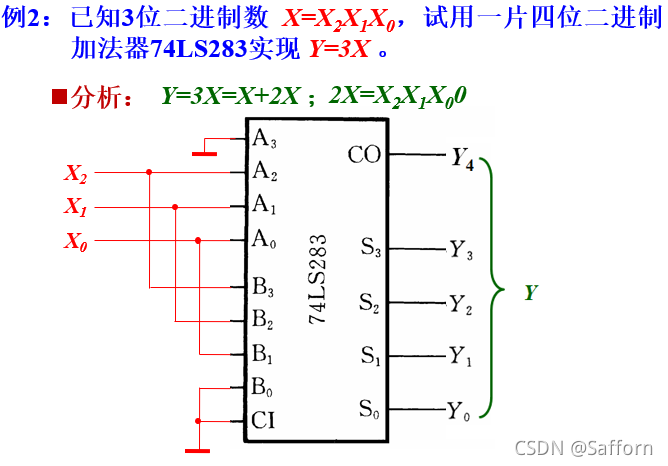

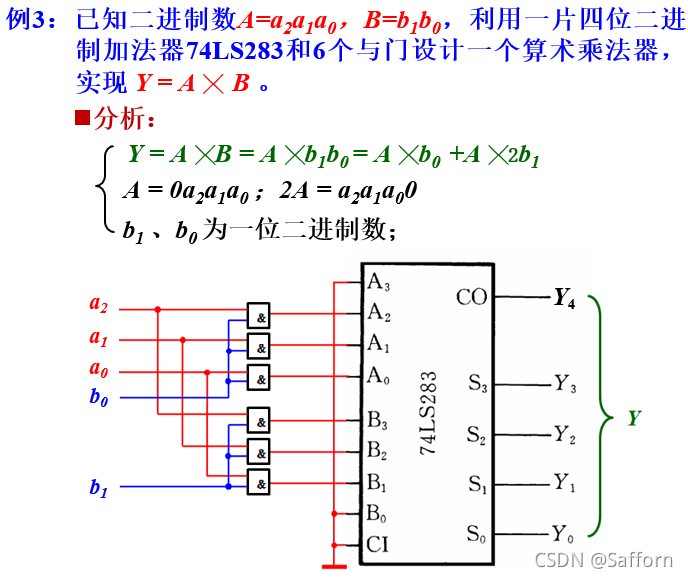

74LS283(4位超前进位加法器)

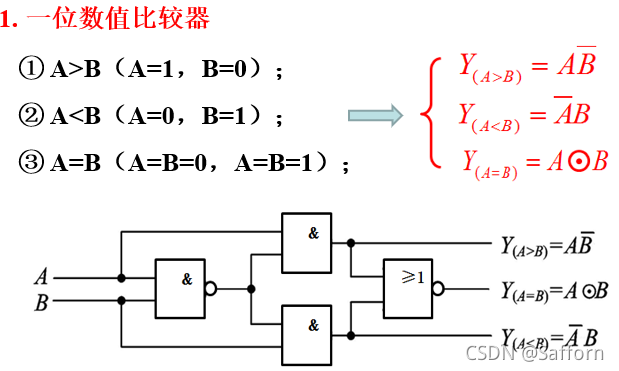

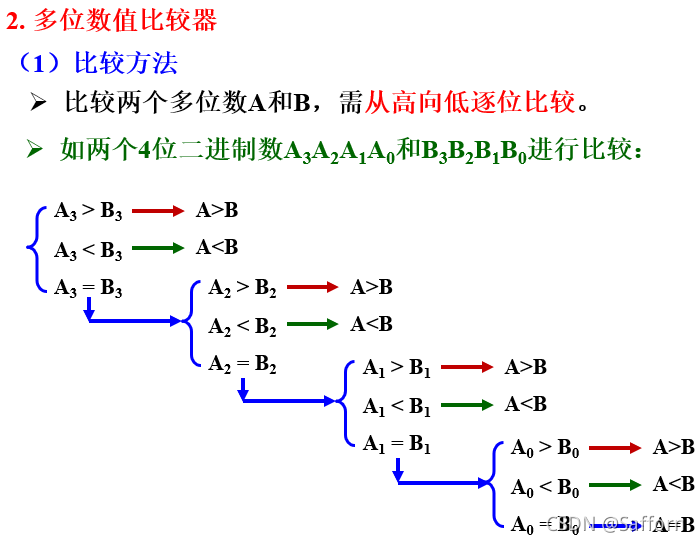

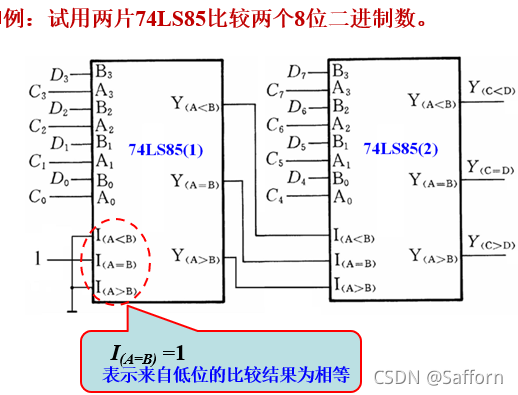

4.7 数值比较器

74LS85(4位数值比较器)

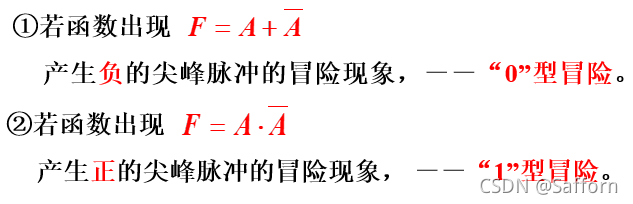

4.8 组合逻辑电路的竞争和冒险

- 竞争:由于门电路的传输延迟时间的不同,某一变量经不同途径传输后,到达某一会合点的时间不同

- 自竞争:由于不同传输路径的门电路延迟造成的竞争

- 冒险(出现尖峰脉冲/毛刺):由于竞争导致电路输出出现不符合门电路稳态的逻辑功能的现象

- “1”型冒险:出现正脉冲

- “0”型冒险:出现负脉冲

注意:竞争的存在不一定会产生冒险

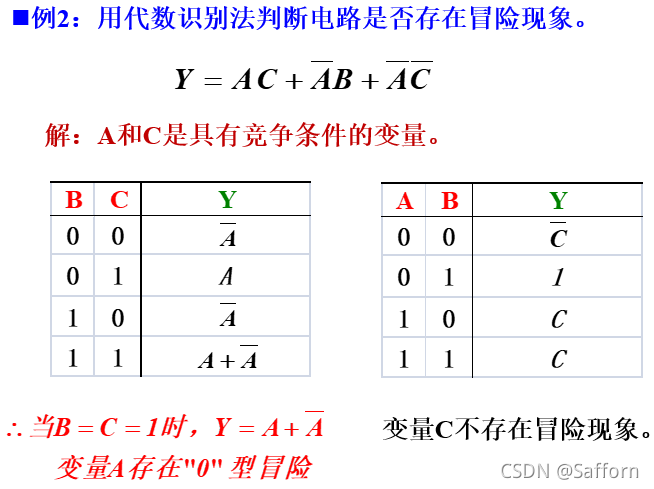

竞争-冒险现象的检查方法

- 代数识别法

一个变量以原变量和反变量出现在逻辑函数F中时,则该变量是具有竞争条件的变量

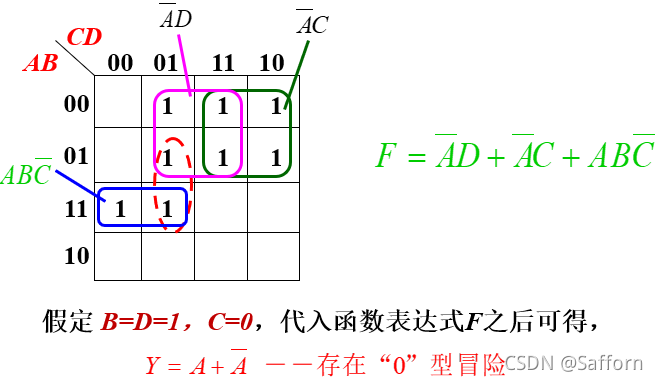

- 卡诺图识别法

存在 “相切” 的卡诺圈

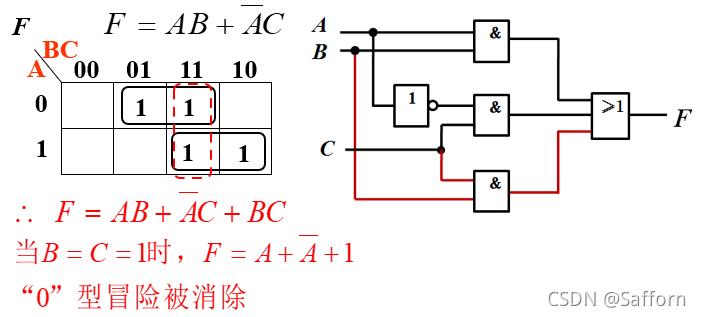

竞争-冒险现象的消除

- 接入滤波电容法

- 引入选通脉冲法:选通信号的作用时间和极性要合适

- 修改逻辑设计法(增加冗余项):在卡诺圈 “相切” 处,增加一个卡诺圈,即可消除冒险

七、可编程逻辑器件

-

任何组合逻辑电路都可以用“与门-或门”两级电路实现

-

任何时序逻辑电路都可以用组合逻辑电路和存储电路实现

-

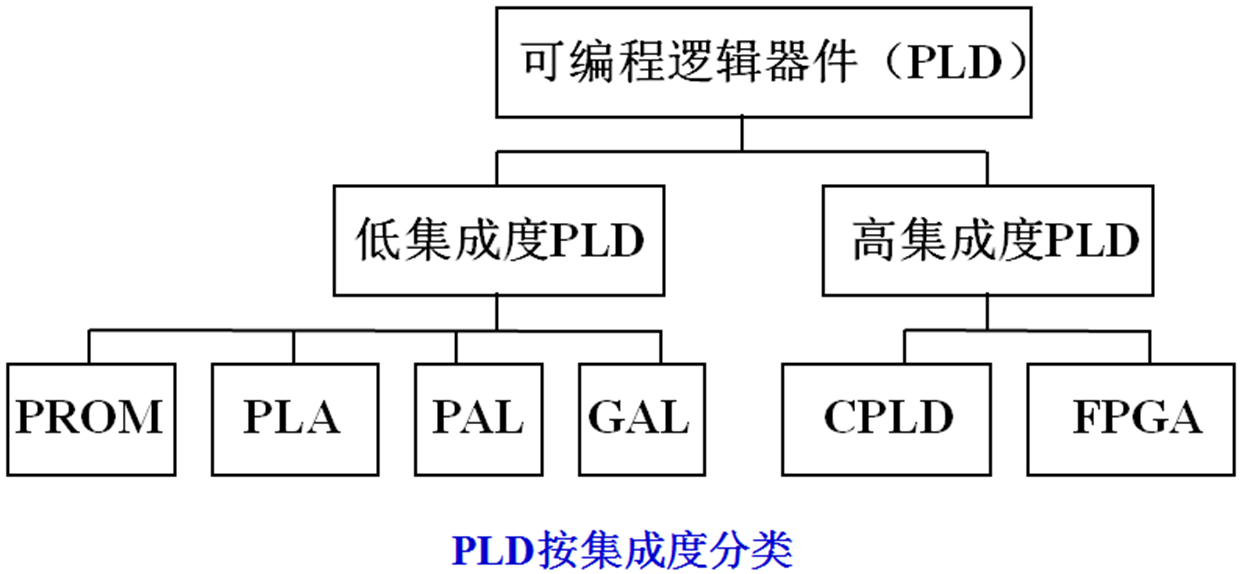

PLD(Programmable Logic Device) 发展历程:

PROM(可编程ROM) --> PLA(可编程逻辑阵列) --> PAL(可编程阵列逻辑) --> GAL(通用阵列逻辑) --(高密度)–>

EPLD(可擦除可编程) --> CPLD(复杂可编程) --> FPGA(现场可编程门阵列) --> SOPC(片上可编程系统)

-

低密度PLD(简单PLD/低集成度):集成度小于每片700等效门,包括PROM、PLA、PAL、GAL

-

高密度PLD(复杂PLD/高集成度):集成度大于每片1000等效门,包括CPLD和FPGA

-

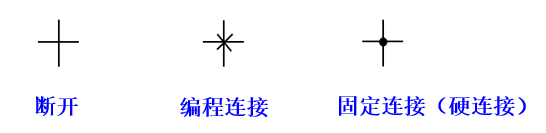

PLD连接表示:

-

四种低密度PLD结构特点:

-

MROM(掩膜只读存储器)

- 只读,不写

- 非易失性:存储的数据不会因为断电而消失

-

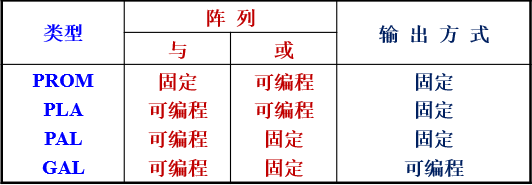

PROM(可编程只读存储器)

- 实现组合逻辑函数,能写成最小项之和形式

- 容量 = 与门数 × 或门数 = 2n×m

- 缺点:逻辑门利用效率低

-

熔丝型PROM:一次性可编程(OTP)

-

EPROM(紫外线擦除型PROM)

- 通过紫外线照射擦除内容,可重复擦除上万次

- 离线擦除和写入,需要专用设备

-

E2PROM(电可擦除PROM)

- 电擦除,可重复擦写100次,擦除速度快

- 电擦除过程就是改写过程,具有ROM的非易失性,又具备RAM的功能

-

Flash Memory(快闪存储器)

- 数据的擦除和写入分开进行

- 数据写入方式与EPROM相同,可擦除/写入100w次以上

-

PLA(可编程阵列逻辑)

- 与阵列 和 或阵列 都可编程

- 实现组合逻辑函数,用最简与或形式表示

- 容量 = 与门数 × 或门数

- 缺点:制造工艺复杂

-

PAL(可编程阵列逻辑)

- 与阵列 可编程,或阵列 固定

- 实现组合逻辑函数,用最简与或形式表示

- 容量 = 或门输入端数 × 或门数

- 缺点:输出包含的乘积项受限

-

GAL(通用阵列逻辑)

- 基于PAL和E2PROM,与阵列 可编程,或阵列 固定

- 输出端设有可编程的OLMC(输出逻辑宏单元)

-

PLD设计流程:首先根据设计要求写出相应的逻辑表达式,在计算机上利用PLD软件通过原理图输入方式或硬件描述语言(HDL) 输入方式输入逻辑设计描述,经计算机仿真验证后,下载到PLD器件中

-

传统电子设计方法:自底向上,任意时刻最低层目标器件的更换都可能需要重新开始设计

-

PLD设计特点:自顶向下,采用硬件描述语言作为设计输入,用HDL对数字电子系统进行抽象与功能描述

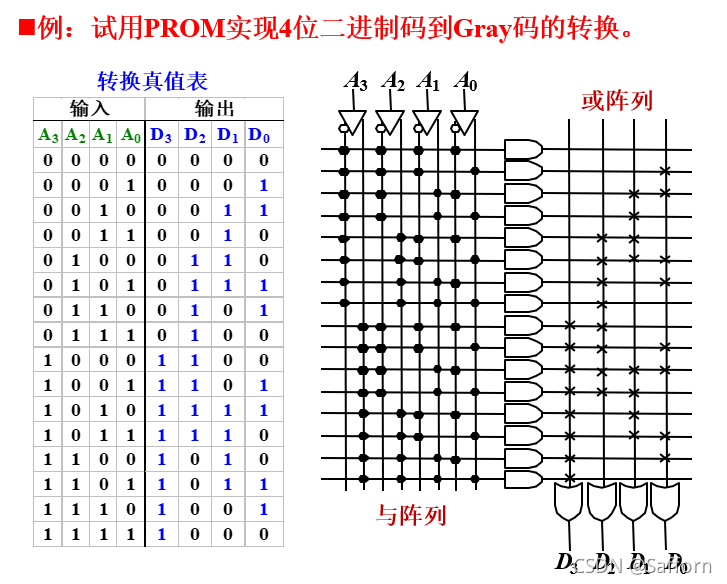

八、脉冲波形的产生与整形

- 获得矩形脉冲的方法:

- 脉冲波形发生电路(多谐振荡器)

- 脉冲波形整形电路:利用整形电路把周期性变化的波形变换为符合要求的矩形脉冲

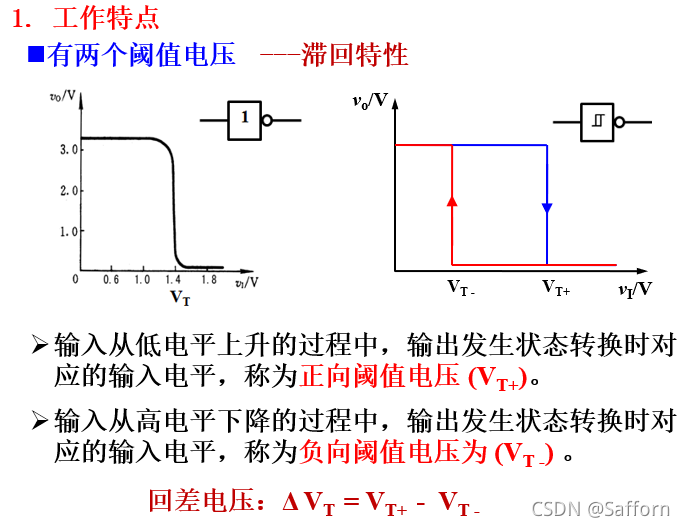

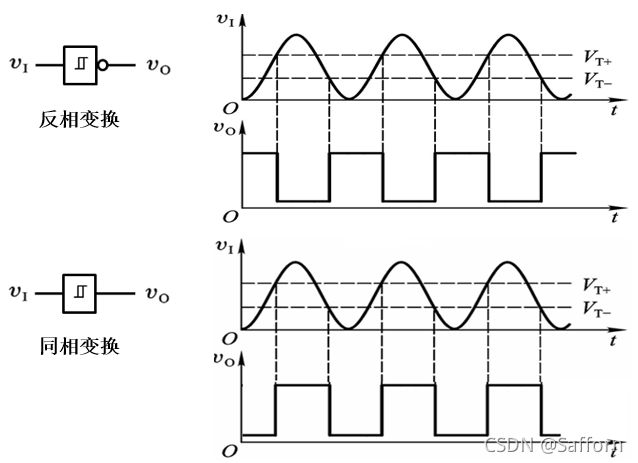

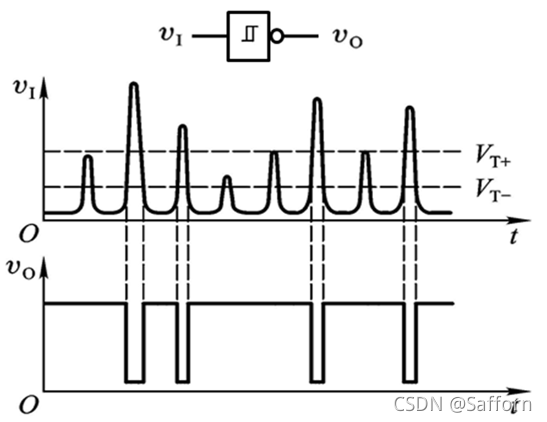

- 施密特触发器(一种特殊的数组传输门)

-

波形变换:将周期性变化的波形转换为矩形脉冲

-

鉴幅:将幅度大于 VT+ 的脉冲信号选出

-

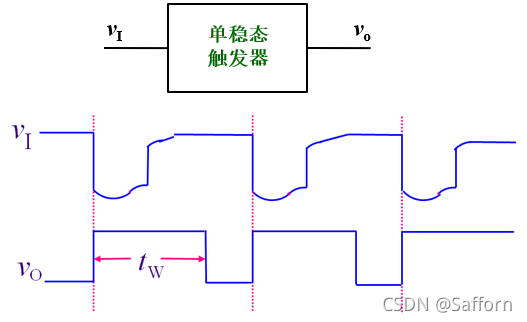

- 单稳态触发器

-

电路具有稳态和暂稳态两个工作状态,在外界触发脉冲作用下,能由稳态暂时反转到暂稳态,维持一段时间后自动返回稳态

-

暂稳态持续时间与电路自身参数有关,与外界触发脉冲无关

-

脉冲整形:能够把输入的不规则脉冲信号 vI,整形为具有一定幅度和一定宽度的标准矩形脉冲 vO。vO 的幅度取决于单稳态电路输出的高、低电平,宽度 tW 决定于电路元件的参数

-

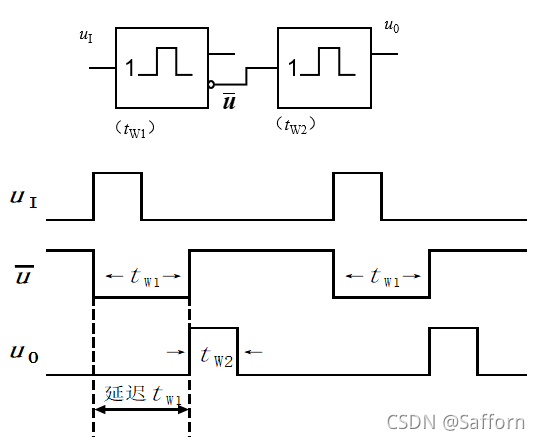

脉冲延时:脉冲延时电路一般要用两个单稳态触发器完成。延时时间为 tW1,它决定于第一级单稳态触发器的定时元件

-

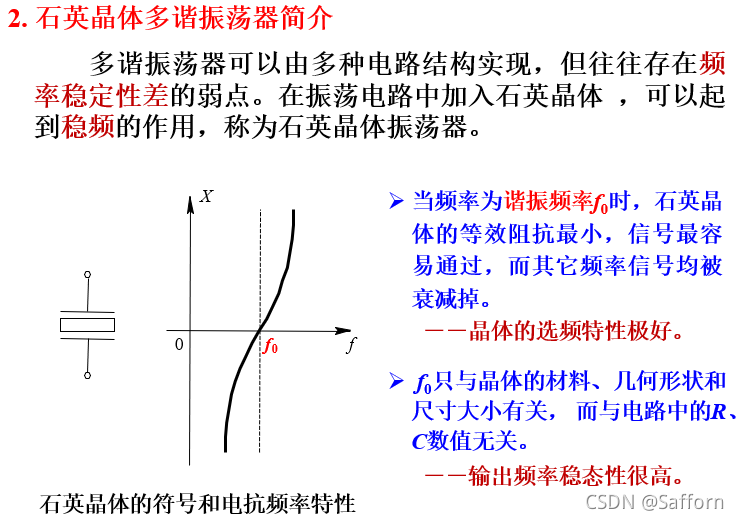

- 多谐振荡器

- 无稳态,有两个暂稳态

- 自激振荡器——在接通电源后,不需外加触发信号,便能自动产生矩形脉冲

- 矩形波中除基波外,还含有丰富的高次谐波——称为多谐振荡器

- 555定时器

- 多用途的数字-模拟混合集成电路,内部有3个精密的5KΩ电阻

- 双极型产品:最后数码为555,如5G555

- CMOS型产品:最后数码为7555,如CC7555

- 实际应用:构成施密特触发器、单稳态触发器、多谐振荡器

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?