加法器

一位加法器:

Si=Ai⊕Bi⊕CiCi+1=AiBi+(Ai⊕Bi)Ci\n延迟运算: 与门、或门 1T;异或门3T\n\n行波进位的补码加法/减法器

当M=0时,B数各位经过0异或保持原数B不变,最低位进位为0,结果就是A与B相加;当M=1时,B数各位经过1异或取反,再结合最低位的进位1,结果就是A+(-B)= A-B\n\n定点乘法\n\n在定点计算机中,两个原码表示的数相乘的运算规则是:乘积的符号位由两数的符号位按异或运算得到,而乘积的数值部分则是两个正数相乘之积。

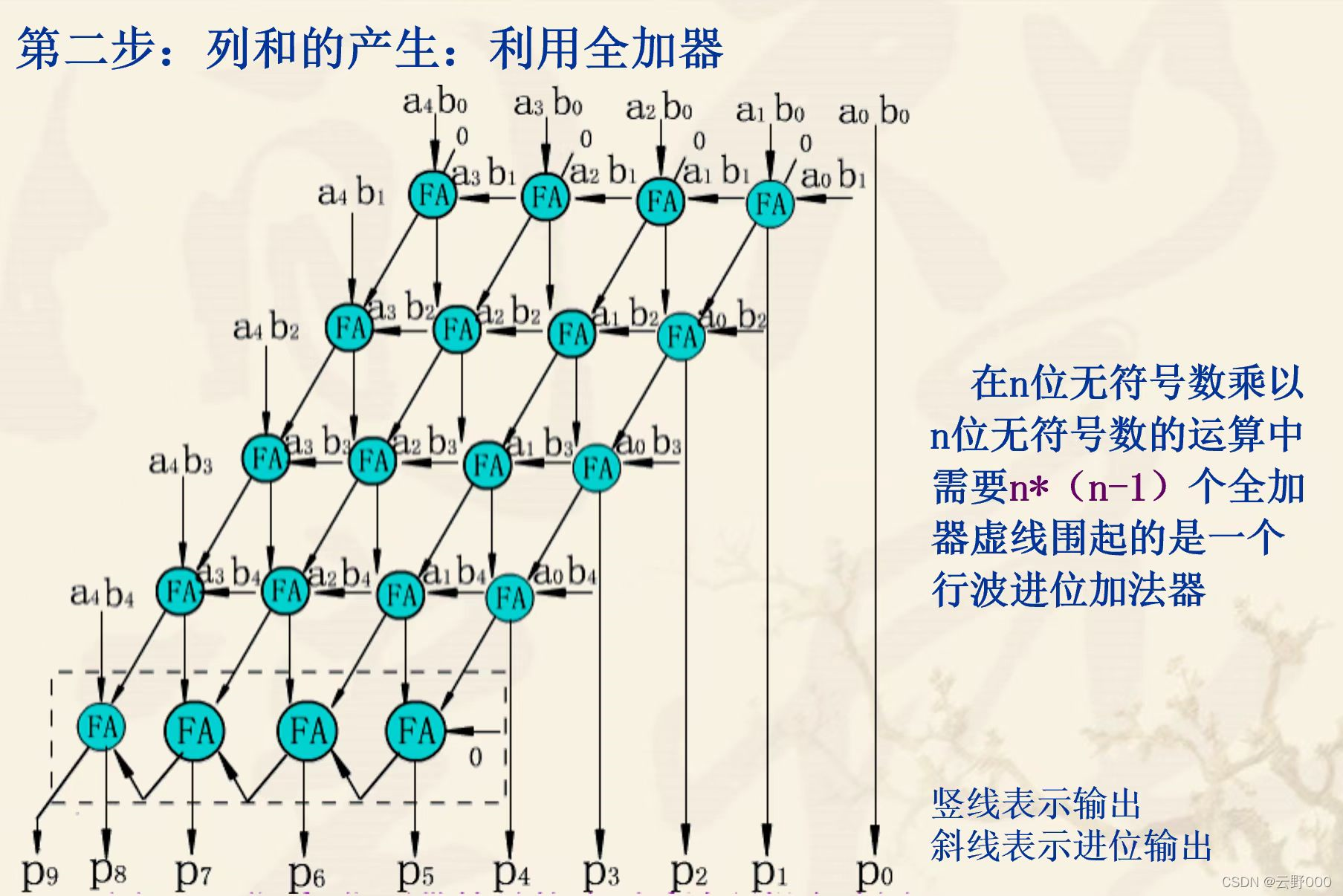

介于串行乘法器已经被淘汰,下面只介绍并行乘法器。并行乘法器的关键是快速产生n*n个位积,然后对位积进行相加运算产生n+n-1个列和。\n\n并行乘法器:\n第一步是并行计算nn个位积,为此需要nn个与门;\n第二步是利用n*(n-1)个全加器计算列和。

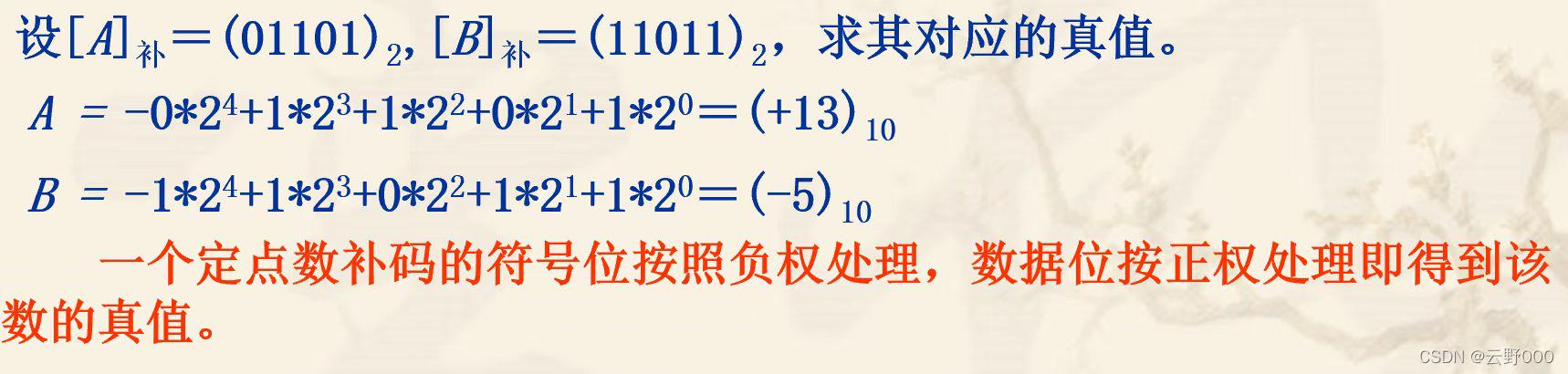

间接补码乘法运算\n由于在计算机内数据是以补码形式存在,必须考虑补码乘法运算中由补码、原码之间简便的互换运算\n\n由补码直接求原码的运算:\n\n正数的补码不变,负数的补码等于从右边开始遇到的第一个真值的1以后除了符号位以外1变0,0变1。\n\n求补电路的思想:\n\n如果符号位是0,数据不变\n\n如果符号位是1,则符号位保持不变,数据位从lowbit(x)左边除符号位以外全部求反

串联的或门陆续接受来自低位的数字和上一次的或门输出,一旦某一次低位数字为1,这一次的或门输出及后续的或门输出均为1。每一级的或门输出都会与使能端E相与,当使能端E=1时,简化为直接由或门输出控制。与门输出接异或门,当或门为1,E=1时,异或门发挥求反功能。当使能端为0时,各级异或门均为0,不发挥求反功能,即各位均保持不变。因此,可以将使能端接数的符号位。\n\n间接补码乘法器,即先将两个数经过算前求补器转化为原码,然后经过乘法器,再将结果经过算后求补器转化为补码。

直接补码乘法运算

根据这一特点,我们可以设计输入带有负权的加法器,用来构造直接补码并行乘法器。根据带有负权的输入端数量,可以分为0,1,2,3四类加法器。用混合加法器构造出的并行乘法器如下图:

1882

1882

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?