目录

近来有空闲,把前几个学期做的实验上传上来。如有错误的地方欢迎大佬批评指正,有更好的方法也期待您的分享~

一、8位运算器

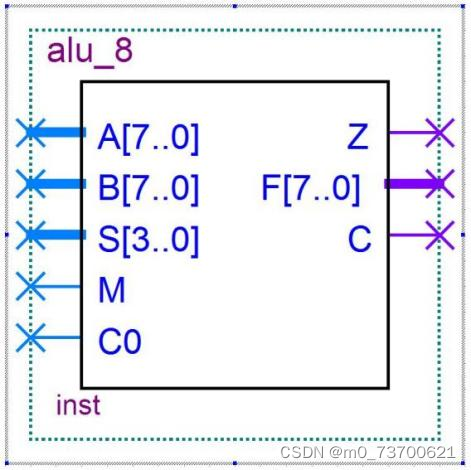

1. 设计8位运算器

用两片74181实现8位运算器

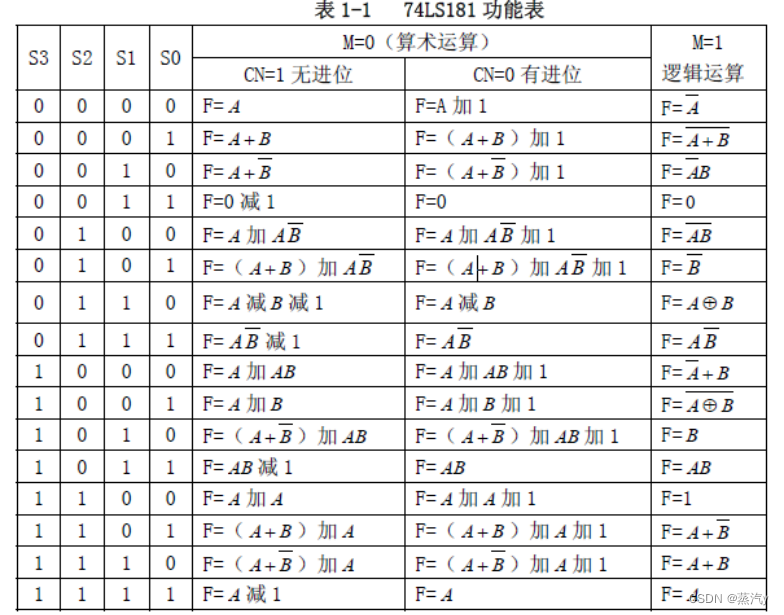

图中,A[7..0];B[7..0]是输入;C是低位来的进位;F[7..0]是输出;C是向高位的进位;S0到S3是四个控制端,用于选择进行何种运算;M用于控制ALU进行算术运算还是逻辑运算。

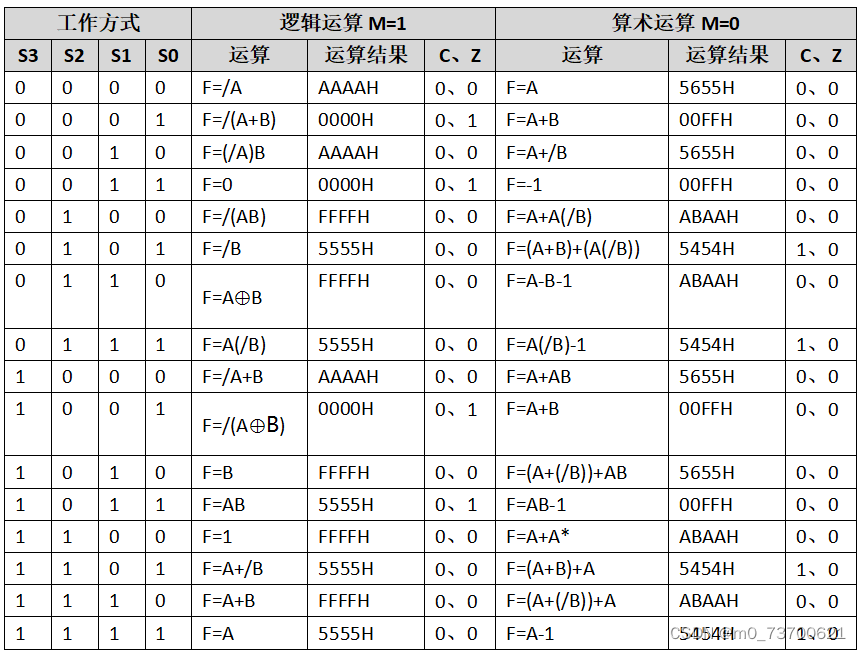

当M=0时,M对进位信号没有任何影响,Fi值与操作数Ai,Bi以及地位向本位进位Cn+1有关,所以M=0时进行算术运算。操作数用补码表示,“加”只算术加,运算时考虑进位;“+”指逻辑加,不考虑进位;减法运算时,减法取反码运算后用加法器实现,结果输出为A减B减1在最末位产生一个强迫进位(加),以得到A减B的结果。

当M=1时,封锁了各位的进位输出Cn+i=O,因此各位的运算结果Fi仅与操作数Ai,Bi有关,此时进行逻辑运算。

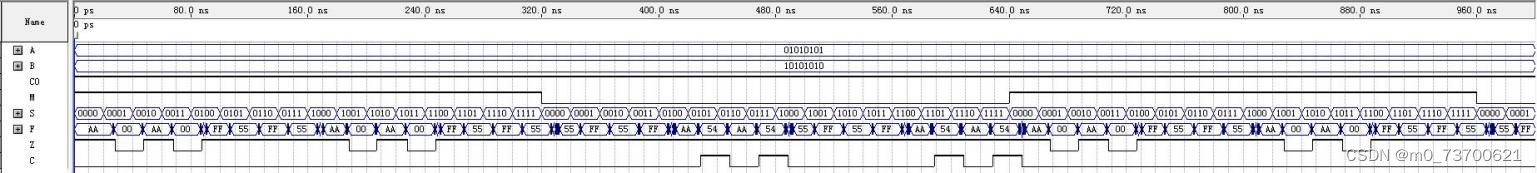

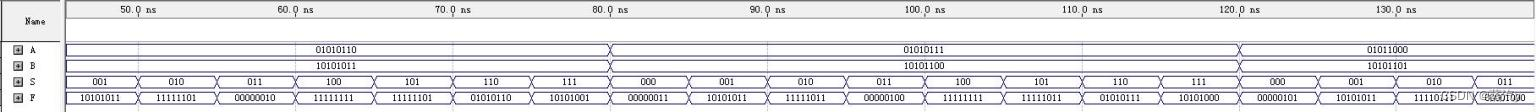

2. 8位运算器功能仿真

设定数据为A=55H,B=0AAH,进行功能仿真。

将仿真结果图对比运算表格图,运算正确。

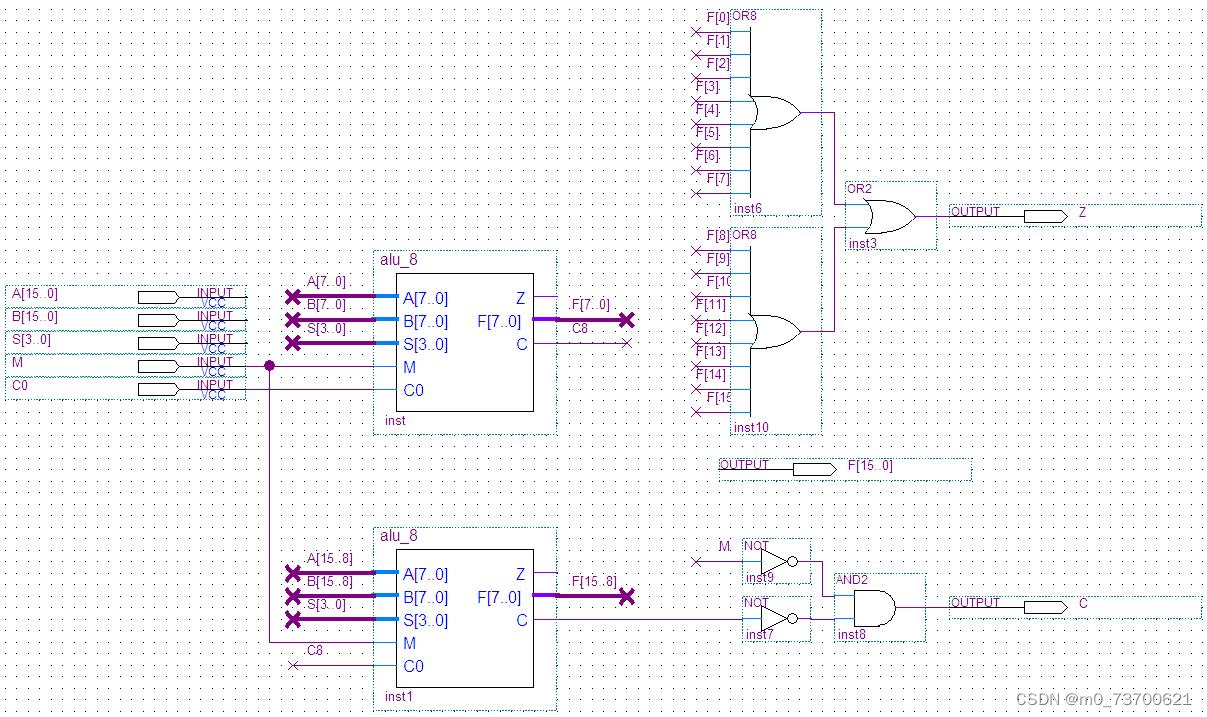

二、16位运算器

1. 设计16位运算器

(1)将8位运算器打包封装

(2)用两片封装好的8位运算器实现16位运算器

2. 16位运算器功能仿真

设定数据为A=0101010101010101;B=1010101010101010,进行功能仿真。

由运算表格知,该16位运算器运算结果均正确,则该电路能正常工作。

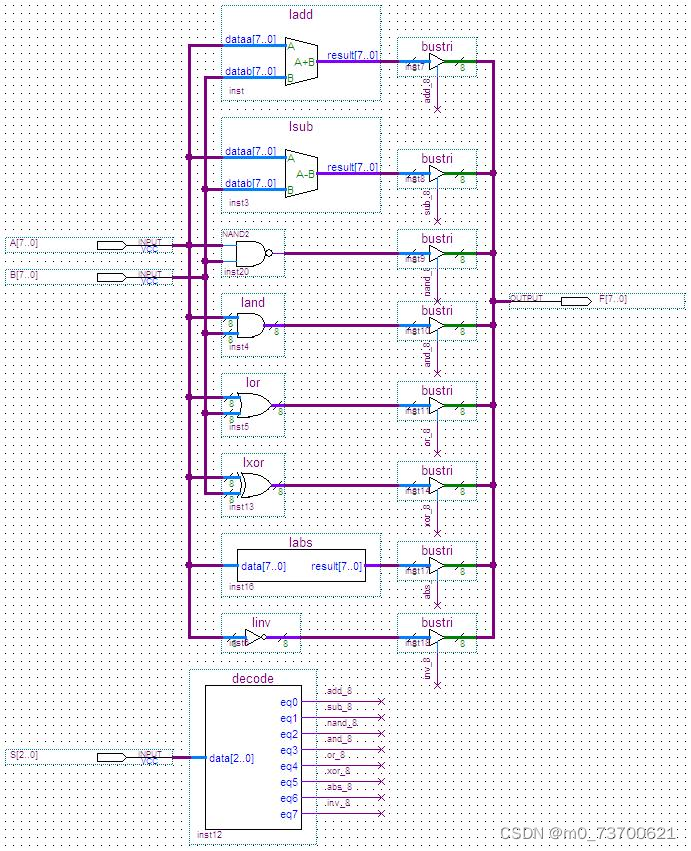

三、实现8种运算的运算器

1. 设计能实现8种运算的运算器

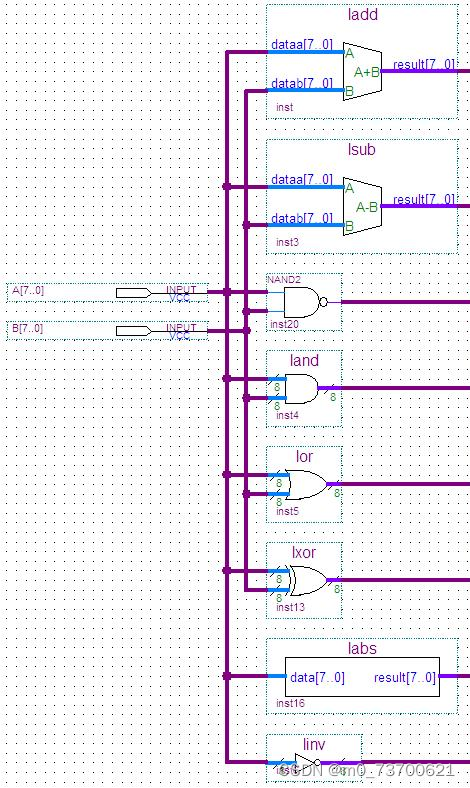

(1)添加实现8种运算的宏功能模块元件

添加输入信号:input ,修改输入信号依次为A、B。

添加8种实现运算功能的宏功能模块:①lpm_add参数化的加法器;②lpm_sub参数化的减法器;③nand2 与非门;④lpm_and参数化与门;⑤lpm_or参数化或门;⑥lpm_xor参数化异或门;⑦lpm_abs参数化绝对值运算;⑧lpm_inv参数化反向器。

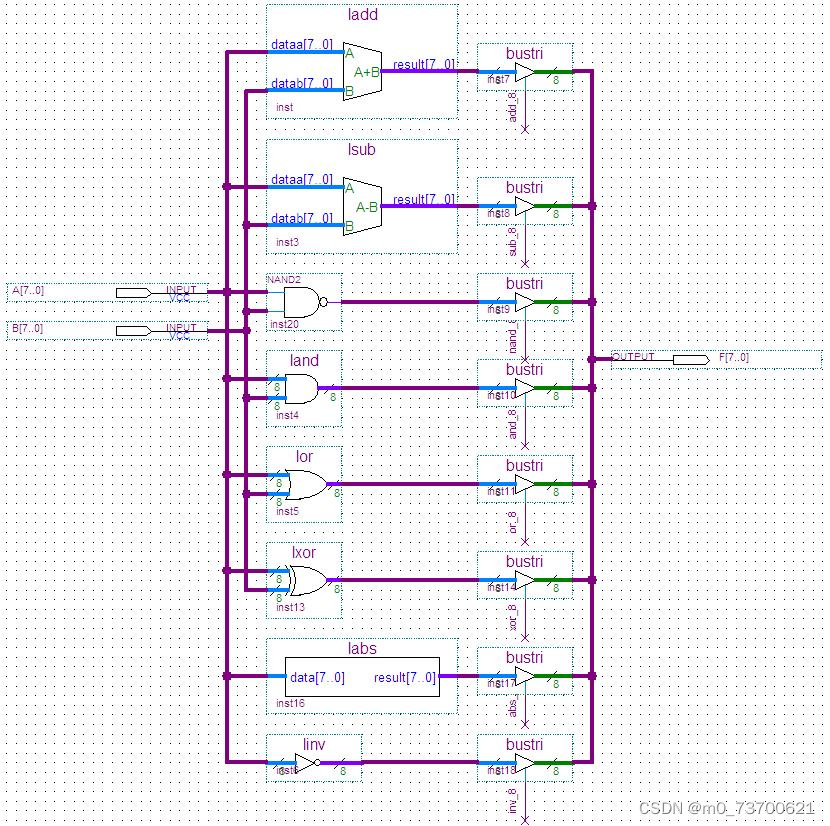

(2)使用三态门做控制

使用lpm_bustri参数化三态缓冲器来做控制。在每一块宏功能模块后面都接一个三态门,当使能信号有效的时候,三态门导通;当使能信号无效的时候,三态门不工作,就像开关一样。

三态门由于选中才工作,不选中相当于短路,首先保证8个三态门当中,一次只有一个是导通的,任何时刻只有一个三态门的使能端有效,所以所有的三态门接到一起,不需要使用数据选择器,后端接一个输出端output,修改命名为F。

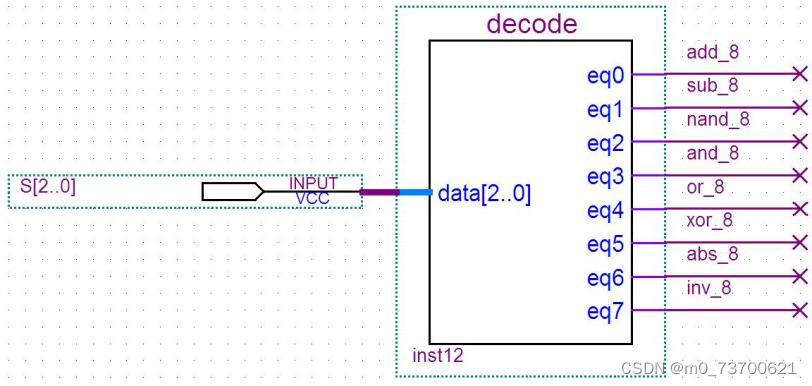

(3)使用3-8译码器实现功能的选择

为保证三态门在任何时刻只有一个三态门的使能端有效,使用lpm_decode参数化译码器制作3-8译码器。

3-8译码器每一个引脚使用命名法连接一块三态门的使能端,从而实现8种运算功能的控制。

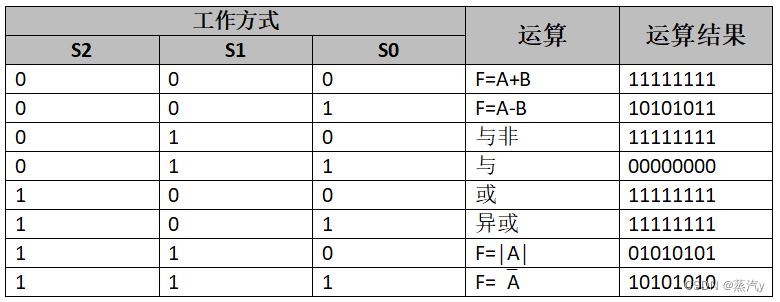

2. 实现8种运算的运算器的功能仿真

设定数据为A=01010101;B=10101010。

(1)设定数据为A=01010101;B=10101010

由运算表格知,该运算器8种功能运算结果均正确,则该电路能正常工作。

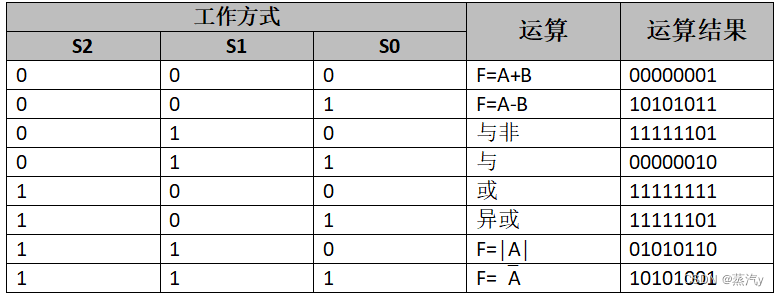

(2)设定数据为A=01010110;B=10101011

由运算表格知,该运算器8种功能运算结果均正确,则该电路能正常工作。

附:181功能表

1306

1306

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?