一、CPU 架构

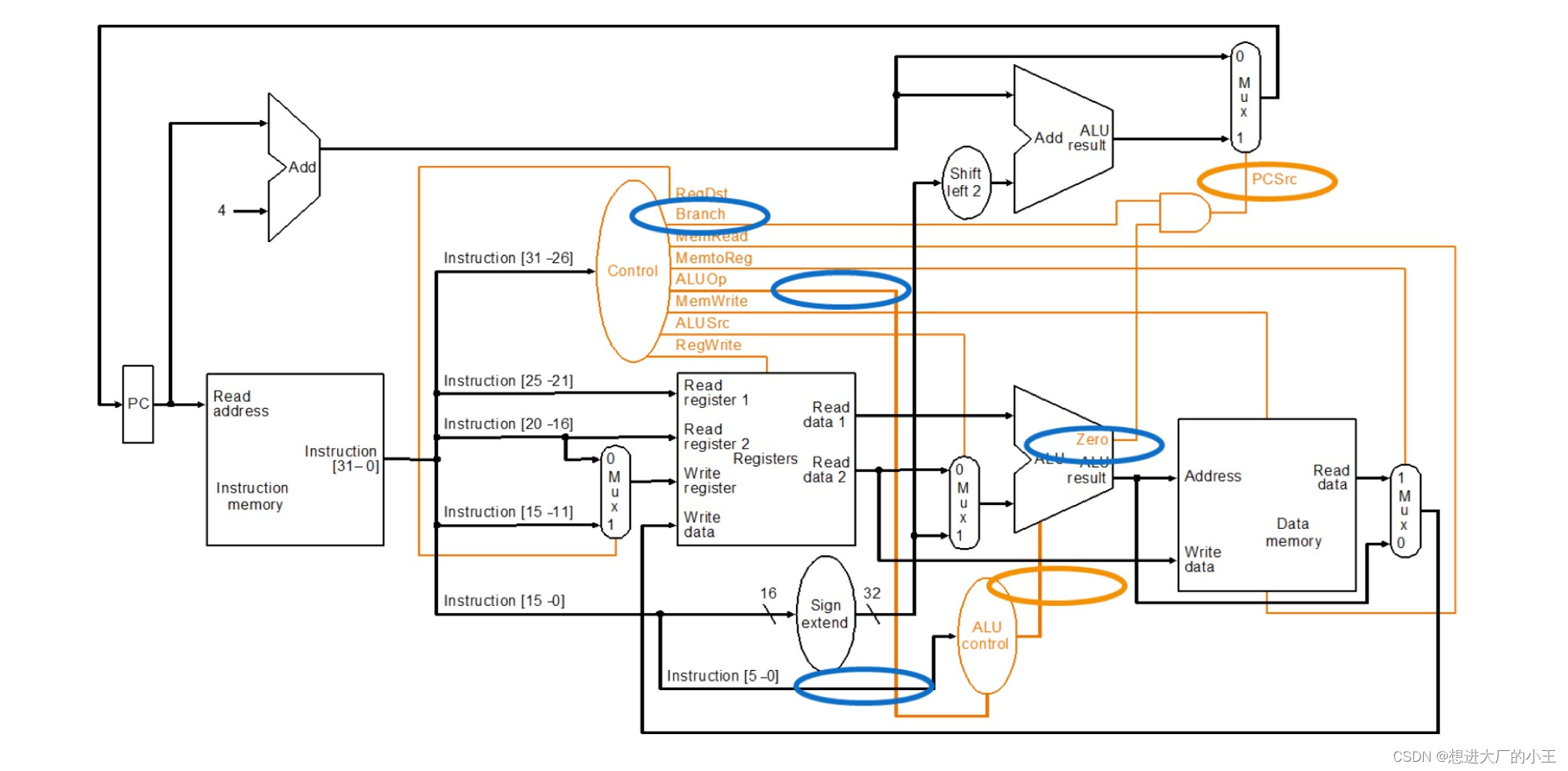

以下图片展示的是基于MIPS ISA 的 单周期CPU的结构图。这种CPU在每个时钟周期完成一条指令的所有阶段,包括取指令、译码、执行、存储器访问以及结果写回。

图中的主要部分包括:

- 程序计数器(PC) - 存储当前指令的地址。

- 指令存储器 - 根据PC的地址读取指令。

- 控制单元 - 根据指令的操作码生成控制信号,控制其他硬件部件的行为。

- 寄存器堆 - 存储CPU内的临时数据。

- 算术逻辑单元(ALU) - 执行所有的算术和逻辑运算。

- 数据存储器 - 用于读写操作的数据存储区。

控制单元的输出信号控制着数据路径中的多路选择器(MUX)、信号扩展单元(Sign extend)以及ALU的操作。这张图也显示了如何根据指令的类型(如分支指令)选择不同的操作路径。

MIPS指令如何被转换成对应的CPU指令,并实现对应的功能,我们可以以add指令为例,结合CPU数据路径图进行说明。

二、add 指令 在 CPU 中拆解与实施

add指令的格式如下:

这条指令的意思是将寄存器rs和rt中的值相加,并将结果存储在寄存器rd中。add指令是R型指令,其格式如下: 对于

对于add指令

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

889

889

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?