1. MIPI

MIPI(Mobile Industry Processor Interface)移动通信行业处理器接口

- MIPI是MIPI联盟发起的为移动应用处理器制定的开放标准。

- 目的是把手机内部的接口,如摄像头、显示屏接口、射频/基带接口等标准化,从而减少手机设计的复杂程度和增加设计灵活性。

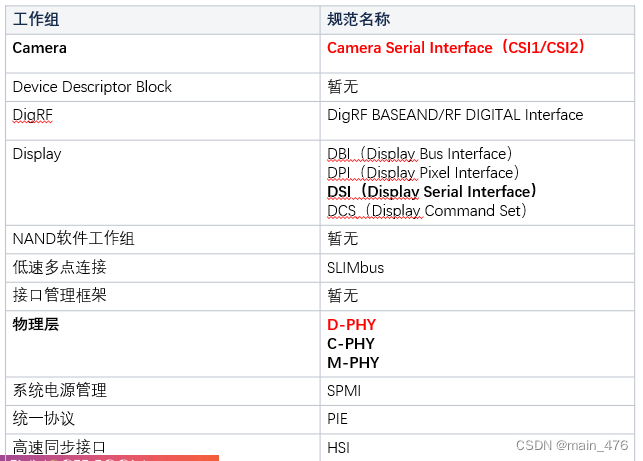

已经完成和正在计划中的规范如下:

1.1.

2. CSI

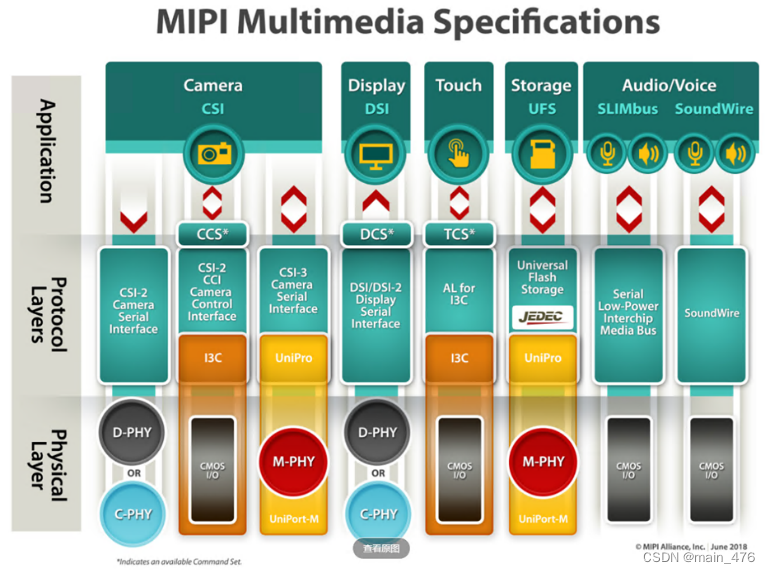

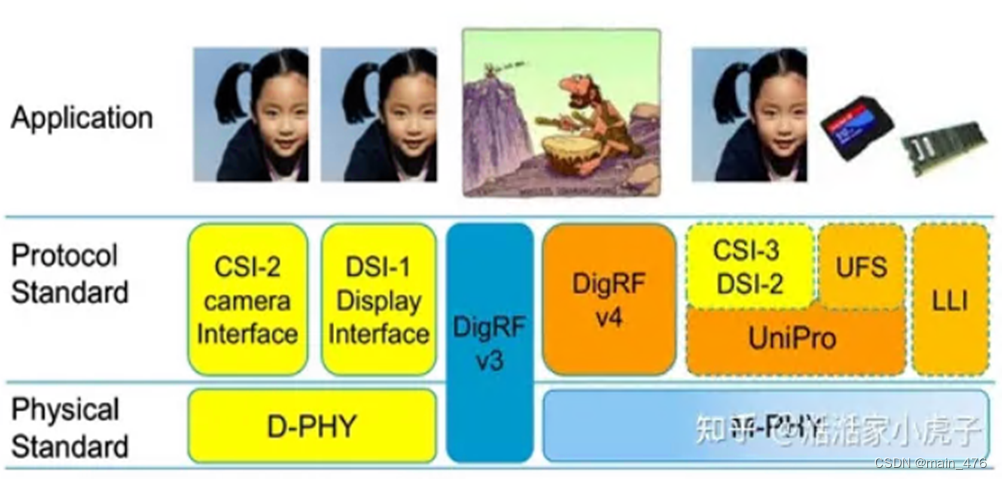

MIPI 协议主要分为三层:应用层,协议层和物理层,应用于摄像头,显示器等设备的接口 DSI(Display Serial Interface)

,这里重点介绍摄像头接口CSI( Camera Serial Interface)显示

- 应用层(Application Layer),主要描述了上层数据流中的数据编码和解析

- 协议层(Protocol Layer),包含了几个不同的子层,每个子层都有各个明确的职责,主要包括:

Pixel/Byte Packing/UnpackingLayer:像素/字节打包/解包层

LowLevelProtocol Layer:LLP组织串行数据

LaneManagement:通道管理层

物理层(PHYLayer),定义了传输介质,输入输出信号的电气特性和时钟机制,即如何从串行位流中获取 “0” 和 “1”信号,同时生成SoT与EoT等信号

3. D-PHY概述

D-PHY定义了一种源同步,高速,低功耗以及低成本的PHY

PHY的配置项

(1)一条clock lane

(2)1/2/4条data lane

D-PHY有三种不同类型的通道:

(1)单向时钟通道Unidirectional Clock Lane

(2)单向数据通道Unidirectional Data Lane

(3)双向数据通道Bi-directional Data Lane (CSI没用,主要是DSI的lane 0)

D-PHY有两种传输模式

(1)HS高速传输模式,用于传输突发数据,同步传输,信号为差分信号,电平范围为100mv-300mv,传输速度范围是80-1500Mbps,(速率和d-phy版本相关,这里是dphy-1.1版本的速度,目前市面上大部分还是v1.1,甚至1.0版本)

(2)LP低功耗模式,用于传输控制指令,异步传输,信号线为单端,电平范围是0-1.2V,没有用时钟线,时钟是通过两个数据线异或而来

的,速度只有10Mbps

3.1. D-PHY PPI接口

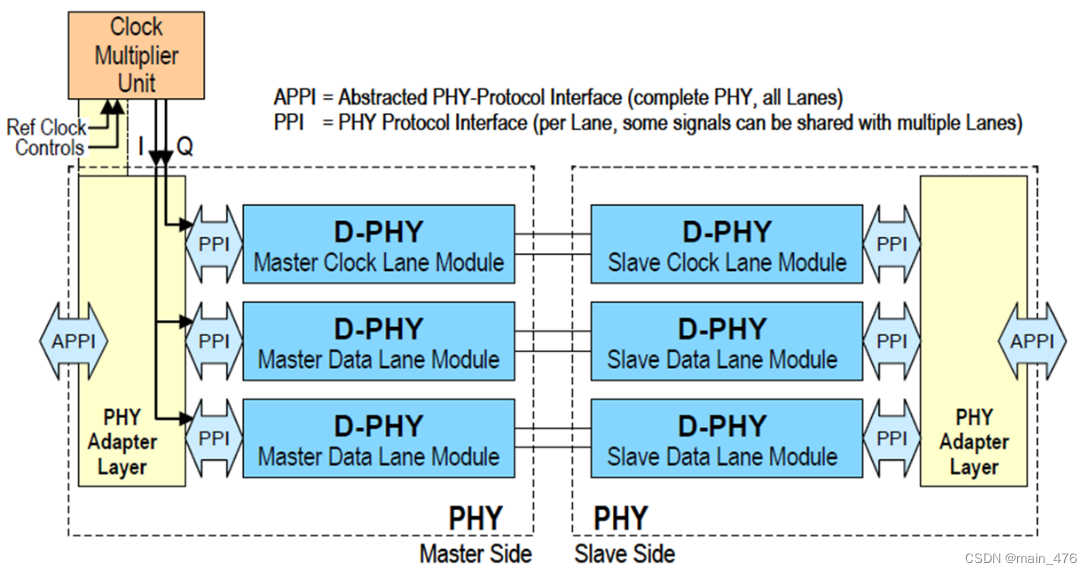

下图是主控制器和外围设备通过mipi d-phy连接示意图:

Lane Module:用来发送或接收lane 上的信号

PPl: PHY-ProtocolInterface PHY协议接口

PHYAdapter Layer: APPI接口与PPI接口的转换

APPI: 抽象物理层协议接口(用于再不同通信协议与物理层之间建立通用的、独立硬件和接口协议)

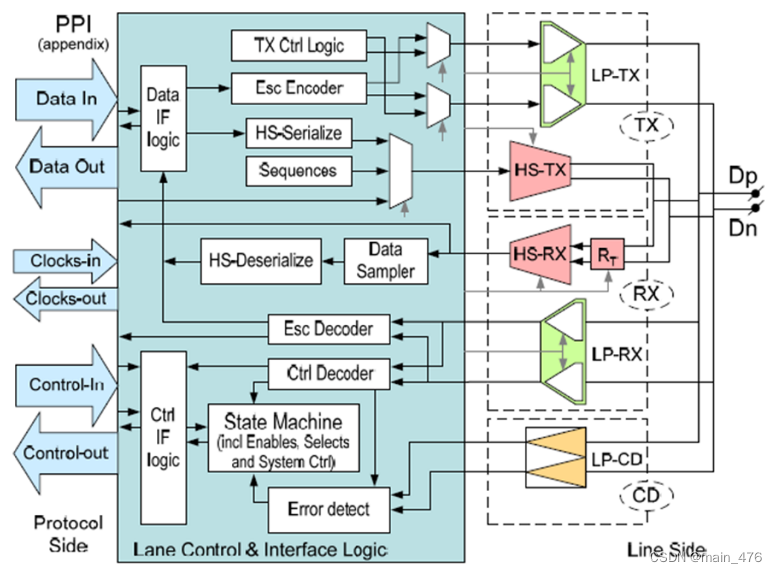

3.2. D-PHY Lane Module

右图是一个通用的 Module内部结构图

功能:

取决于Lane 类型 (时钟,数据单向, 数据双向) Lane 以及lane module是发送端还是接收端

构成:

一个或多个高速收发模块 ((HS-TXHS-RX) 一个或多个单端低功耗收发模块(LP-TXLP-RX)以及lane控制和接口逻辑模块Logicy Control&lnterface Lane 组成

3.3. D-PHY Lane Levels & Lane States

Line Levels (typical)

本文详细介绍了MIPI及其子协议CSI和D-PHY,包括它们在移动设备内部接口标准化中的作用,物理层设计,以及应用在摄像头、显示和通信方面的具体实现。此外,还涵盖了CSI-2协议的三层结构,特别是像素字节转换、低级协议和lane管理。文章最后讨论了宽动态范围模式和InnoWriteback技术在实际应用中的实现。

本文详细介绍了MIPI及其子协议CSI和D-PHY,包括它们在移动设备内部接口标准化中的作用,物理层设计,以及应用在摄像头、显示和通信方面的具体实现。此外,还涵盖了CSI-2协议的三层结构,特别是像素字节转换、低级协议和lane管理。文章最后讨论了宽动态范围模式和InnoWriteback技术在实际应用中的实现。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?