验证技术

动态验证技术(SV+UVM)

-

通俗而言,就是依靠仿真器(simulator)来对数字电路进行激励发送和结果检查

-

相比于20年前的定向激励和测试通过率,目前SOC的动态验证技术讲依赖更多的途径来量化验证进度

-

最近的10年中,IC/ASIC市场经历了巨大的痛苦,已解决日益增加的验证复杂性,而这主要是采用SOC级设计所带来的

-

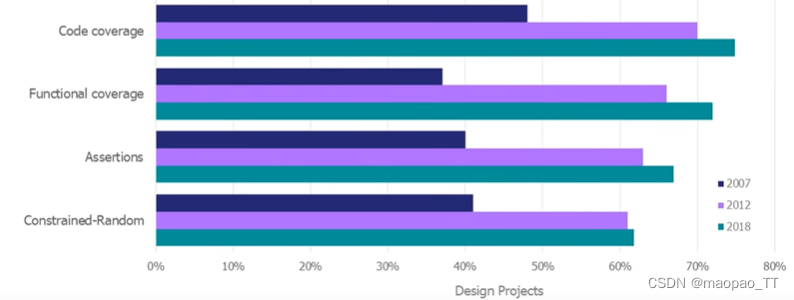

下图比较2007、2012和2018年各种基于仿真的验证技术的采用趋势时,可以清楚地看到IC/ASIC项目流程的这种成熟性

-

code coverage:代码覆盖率

-

functional coverage:功能覆盖率

-

assertions:断言

-

constrained-random:随机约束

-

静态验证技术

-

静态验证技术与动态验证技术是两种完全不同的技术

-

静态验证技术又可以分为人工形式验证技术,即属性检查(property check)和自动形式验证技术

-

属性检查指的是通过断言结合形式验证工具对设计功能进行穷举检查,从数学意义上判断设计的正确性

-

自动验证技术包括SoC集成连接检查,死锁检测,X语义安全检查,覆盖范围可及行分析及许多其他科自动提取然后正式证明的属性

硬件加速(Emulation及FPGA原型开发)

-

SoC尺寸增大的同时,也让原有的仿真方案速度降低,而对于一些复杂场景,性能测试,软件开发的要求无法满足

-

Emulation和FPGA原型开发即是在SoC开发中后期系统趋于稳定是,将其作为逻辑功能容器进行原型(prototyping)开发

-

相比于仿真技术,其速度更快,而可调试性不及仿真,同时其单体售价较仿真器要昂贵

-

目前SoC尺寸增加,市场比例增加的情况下,越来越多的IC设计公司都将Emulation/FPGA原型开发引入了验证流程中

1329

1329

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?