Chapter 1 介绍

这个章节介绍Cortex-M0处理器和它的特点。

1.1 关于Cortex-M0处理器和核心外设

Cortex-M0处理器一个入门级32bit ARM Cortex处理器,它是为广泛的嵌入式应用而设计。在对于开发者而言,Cortex-M0处理器提供了如下优势:

- 简单易用的编程模型

- 超低功耗操作

- 优秀的代码密码

- 精准高效的中断处理能力

- 向上兼容其它Cortex-M处理器系列

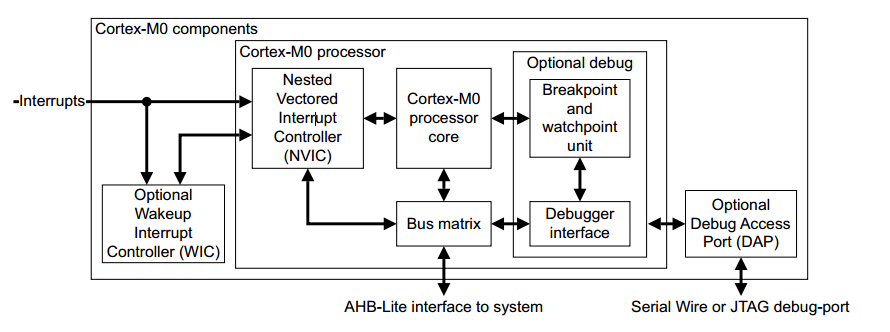

Cortex-M0是构建在一个高性能的处理器核心基础之上,采用三级流水线的冯·诺伊曼结构,并满足嵌入式应用要求。 这个处理器在在低功耗和面积上面做了很大的优化,通过其高效的指令集来提供特殊的功率效率,并包括了高端的处理器硬件:

- 单时钟周期的乘法器,为高性能而优化设计

- 32个时钟周期乘法器,为降低芯片面积而优化设计

Cortex-M0处理器实现了ARMv6-M 架构,采用的是ARMv6-M中的thumb指令集,其中包括了thumb-2技术。它在代码密码方面比其它8-bit和16-bit微控制器更优秀,是一个高性能的32-bit架构。

Cortex-M0处理器高度集成了一个可配置的嵌套矢量中断控制器(NVIC), 并且中断技术性能在业界处于依靠地位。NVIC包括:

- 包括一个不可屏蔽中断(NMI)

- 提供一个零抖动的中断选项和四个中断优先级别

NVIC和处理器核心紧密的结合和高度的集成,保证了中断服务程序的快速执行,大大的减少了中断延迟。这可以通过硬件栈寄存器来实现,并能够停止和重启load-multiple 和store-multiple操作。中断处理函数不需要任何汇编保护代码,因为硬件会全部搞定这些工作。当从一个中断切换到另一个中断的时候,Tail-chaining优化同样可以减少一些开销。

为了降低功耗,NVIC集成了一个休眠模式。休眠模式可以包括支持一个深度休眠功能,它允许整个设备能够迅速关闭。

1.1.1 系统级接口

Cortex-M0处理器提供了一个单系统级接口–AMBA技术。AMBA能够保证提供一个高速,低延时内存访问接口。

1.1.2 集成可配置的调试接口

Cortex-M0处理器实现了一个全硬件调试方案,并有扩展的硬件断点和观察点选项。调试器有助于我们全方面的查看处理器,内存和外设的情况。对于目前的微控制器和小封装的芯片来说,一个JTAG接口和两线SWD接口是很理想的方式。其中选用哪种方式是由生产厂商而决定。

1.1.3 Cortex-M0处理器特点总结

- 在32-bit系统性能上有高代码密度

- 能够在Cortex-M系列架构中向上兼容所有

- 集成低功耗休眠模式

- 执行代码的高效性

- 硬件乘法器

- 零抖动中断处理

- 丰富的中断调试接口

1.1.4 Cortex-M0核心外设

Cortex-M0核心外设包括:

NVIC 一个能够支持低延迟的中断处理的嵌入式中断控制器。

SCB 系统控制块(SCB)是程序员模型接口,它提供了系统实现信息和系统控制,包括配置,控制和系统异常报告。

Optional system timer 操作系统时钟,是一个 24位时钟定时器。可以用作为RTOS 基准时钟,或者一个简单计数。

本文介绍了Cortex-M0处理器及其特点,包括简单的编程模型、超低功耗操作、优秀的代码密度、高效的中断处理能力及与其他Cortex-M系列的兼容性。Cortex-M0处理器采用三级流水线的冯·诺伊曼结构,支持thumb-2指令集,具有单时钟周期乘法器等高级硬件特性。

本文介绍了Cortex-M0处理器及其特点,包括简单的编程模型、超低功耗操作、优秀的代码密度、高效的中断处理能力及与其他Cortex-M系列的兼容性。Cortex-M0处理器采用三级流水线的冯·诺伊曼结构,支持thumb-2指令集,具有单时钟周期乘法器等高级硬件特性。

400

400

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?