本文系本站原创,欢迎转载! 转载请注明出处:

http://blog.csdn.net/mr_raptor/article/details/6621741

++++++++++++++++++++++++++++++++++++++++++

1. 概述

S3C6410内存控制器是采用的PL340内存控制芯片。AMBA APB3.0接口协议规定,可以通过编程将AXI从总线接口和APB主总线接口进行桥接,实现二者总线上的数据的传输。

DRAM控制器可以通过配置兼容SDRAM类型芯片。通过向DRAM控制器中PL340写入内存芯片配置参数,内存时序,来控制内存工作。

DRAM控制器可以直接从SDRAM或DRAM接收一个控制命令。通过将操作命令写入direct_cmd寄存器,操作SDRAM进行对应操作。通过向memc_cmd寄存器写入状态模式命令,使DRAM控制器进入对应的工作模式。例如:向direct_cmd寄存器写入:Prechargeall’,‘Autorefresh’,‘NOP’,and ‘MRS’ 等命令,可以让SDRAM芯片分别执行不同操作,向memc_cmd寄存器写入一些状态命令可以让SDRAM芯片进入’Config’, ‘Ready’, and ‘Low_power’等工作模式。

DRAM控制器支持两种节能模式。当SDRAM处于不活动状态并且持续一定的时钟周期时,DRAM控制器会自动将SDRAM进入预充电节能模式或正常节能模式下以降低系统功耗。当驱动操作DRAM控制器进入对应的STOP(停止),Deep Stop(深度睡眠),Sleep Mode(睡眠)等模式时,SDRAM芯片进入自刷新的节能模式。

l 支持SDR SDRAM,Mobile SDR SDRAM,DDR SDRAM和Mobile DDR SDRAM类型芯片

l 支持两个内存芯片

l 支持64位的AMBA AXI总线类型

l 支持16位、64位内存总线

n 存储器接口1:支持16位DDR SDRAM和Mobile DDR SDRAM类型芯片

支持32位DDR SDRAM,Mobile DDR SDRAM,Mobile SDR SDRAM和SDR SDRAM类型芯片

不支持16位Mobile SDR SDRAM和SDR SDRAM类型芯片

l 地址空间:存储器接口1支持最多2Gb地址空间

l 支持正常节能模式和预充电的节能模式

l 数据传输低延迟特性

l 外部存储器总线优化

l 通过设置SFR寄存器支持选择外部存储器选型

l 通过SFR寄存器配置存储器的时序

l 支持扩展MRS指令集

l 工作电压:存储器接口1: 1.8V,2.5V

2. SDRAM类型内存接口

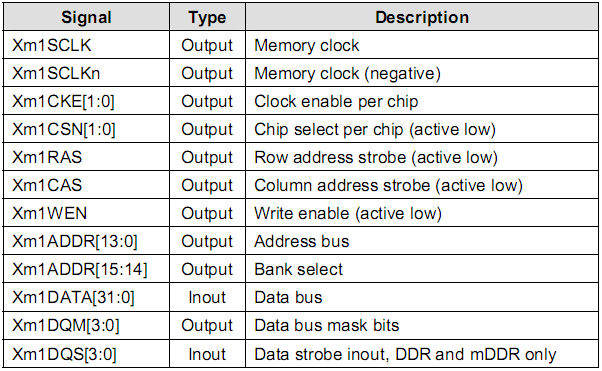

DRAM控制器支持最多两个相同类型的内存芯片,每个芯片最大容量256M。所有芯片共享相同引脚(时钟使能引脚和片选引脚除外),如表1-1所示给出了DRAM控制器的外部存储器引脚配置信息。

3. SDRAM初始化

在系统上电后,必须通过软件配置SDRAM接入DRAM控制器并且初始化DRAM控制器,下面给出DDR、MOBILE DDR SDRAM的初始化流程。

a) 向mem_cmd寄存器写入0b10,使其进入NOP工作状态

b) 向mem_cmd寄存器写入0b00,使其进入Prechargeall(整片预充电)工作状态

c) 向mem_cmd寄存器写入0b11,使其进入Autorefresh(自刷新)工作状态

d) 再次向mem_cmd寄存器写入0b11,使其进入Autorefresh(自刷新)工作状态

e) 向mem_cmd寄存器写入0b10,使其进入MRS工作状态,并且地址空间内的EMRS必须置位

f) 再次向mem_cmd寄存器写入0b10,使其进入MRS工作状态,并且地址空间内的MRS必须置位

4. DRAM寄存器

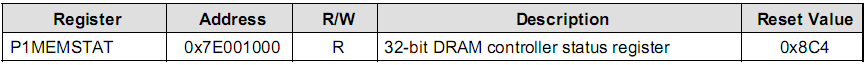

1) DRAM控制器状态寄存器(P1MEMSTAT)

| P1MEMSTAT | 位 | 描述 | 初始值 |

| 保留 | [31:9] | - | - |

| 芯片数量 | [8:7] | 内存控制器支持的芯片最大数量: 01 = 2片 6410只支持2片芯片,初始化为只读的01 | 01 |

| 芯片类型 | [6:4] | 内存控制器支持的芯片类型: 100 = MSDR/SDR/MDDR/DDR中任一类型 | 100 |

| 芯片位宽 | [3:2] | 接入内存芯片的位宽: 00 = 16位 01 = 32位 10 = 保留 11 = 保留 | 01 |

| 控制器状态 | [1:0] | DRAM控制器状态: 00 = Config配置状态 01 = Ready就绪状态 10 = Pause暂停状态 11 = Low-Power节能状态 | 00 |

实际上,读到的有用信息就是Controller Status和Memory width。

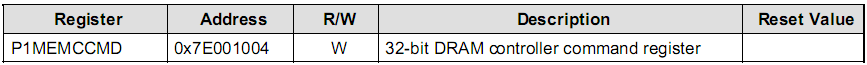

2) DRAM控制器命令寄存器(P1MEMCCMD)

| P1MEMCCMD | 位 | 描述 | 初始值 |

| 保留 | [31:3] | 未定义,写入0 | - |

| Memc_cmd | [2:0] | 设置内存控制器的工作状态: 000 = Go 001 = sleep 010 = wakeup 011 = Pause 100 = Configure 101~111 = 保留 |

|

最开始应该配置为0x4,是处于Configure状态。在配置完所有的DRAM之后,将该寄存器设置为0x0,处于运行状态。

3) 直接命令寄存器(P1DIRECTCMD)

| P1DIRECTCMD | 位 | 描述 | 初始值 |

| 保留 | [31:23] | 未定义,写入0 |

|

| 扩展内存命令 | [22] | (见下表) |

|

| 芯片号 | [21:20] | 映射到外部存储芯片地址的位 |

|

| 命令 | [19:18] | 具体命令(见下表) |

|

| Bank地址 | [17:16] | 当以MRS或EMRS命令访问时,映射到外部存储器的Bank地址位 |

|

|

| [15:14] | 未定义,写入0 |

|

| 地址线0~13 | [13:0] | 当以MRS或EMRS命令访问时,映射到外部存储器的内存地址位 |

|

用于发送命令到DRAM和访问DRAM中的MRS和EMRS寄存器。通过该寄存器初始化DRAM,先设置为NOP模式,然后设置为PrechargeAll进行充电,然后设置EMRS和MRS寄存器,一般是这么一个流程。具体的要参见你所使用的DRAM的datasheet。

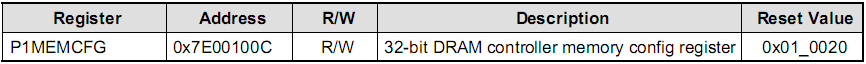

4) 内存配置寄存器(P1MEMCFG)

| P1MEMCFG | 位 | 描述 | 初始值 |

| 保留 | [31:23] | 未定义 |

|

| 启动芯片 | [22] | 使能下面数量的芯片开始执行刷新操作: 00 = 1芯片 01 = 2芯片 10/11 = 保留 | 00 |

QoS master位 | [20:18] | 设置QoS值: 000 = ARID[3:0] 001= ARID[4:1] 010 = ARID[5:2] 011 = ARID[6:3] 100 = ARID[7:4] 101~111 = 保留 | 000 |

| 内存突发访问 | [17:15] | 在内存读写时,设置突发访问数据的数量: 000 = 突发访问1个数据 001 = 突发访问2个数据 010 = 突发访问4个数据 011 = 突发访问8个数据 100 = 突发访问16个数据 101~111 = 保留 该值必须通过DIRECTORYCMD寄存器,写入到内存的模式寄存器中,并且数据必须匹配 | 010 |

| Bank地址 | [17:16] | 当以MRS或EMRS命令访问时,映射到外部存储器的Bank地址位 |

|

| Stop_mem_clock | [14] | 当停止芯片时钟,不允许访问内存数据时,置位 | 0 |

| 自动节能 | [13] | 当该位置位时,芯片自动进入节能状态 | 0 |

| 关闭芯片延迟时间 | [12:7] | 当关闭内存芯片时,延迟的时钟个数 | 000000 |

| 自动预充电位 | [6] | 内存地址中自动预充电位的位置: 0 = ADDR[10] 1 = ADDR[8] | 0 |

| 行地址位数 | [5:3] | AXI地址线上的行地址位数: 000 = 11位 001 = 12位 010 = 13位 011 = 14位 100 = 15位 101= 16位 | 100 |

| 列地址位数 | [2:0] | AXI地址线上的列地址位数: 000 = 8位 001 = 9位 010 = 10位 011 = 11位 100 = 12位 | 000 |

参考DRAM的datasheet。

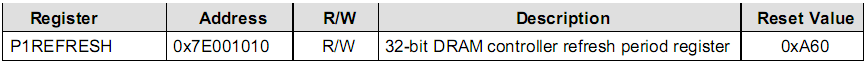

5) 内存刷新时间寄存器(P1REFRESH)

| P1REFRESH | 位 | 描述 | 初始值 |

|

| [31:15] | - |

|

| 刷新时间 | [14:0] | 内存刷新时钟周期数 | 0xA60 |

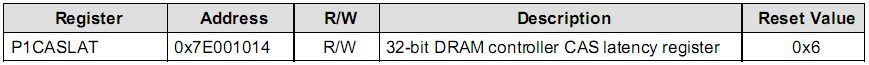

6) CAS 延迟寄存器(P1CASLAT)

| P1CASLAT | 位 | 描述 | 初始值 |

|

| [31:4] | - | - |

| CAS延迟 | [3:1] | 列地址选通延迟内存时钟周期数 | 0xA60 |

| CAS HALF周期 | [0] | 设置CAS延迟数是否为半个内存时钟周期 0 = 以[3:1]设置数为CAS延迟时钟周期 1 = 以[3:1]设置数的一半为CAS延迟时钟周期 | 0 |

参考DRAM的datasheet。

下面13个寄存器用于DRAM操作中所需时间和延时寄存器,具体可以参考PL340文档。

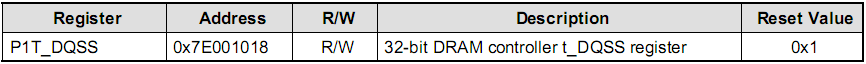

7) T_DQSS寄存器(P1T_DQSS)

| P1T_DQSS | 位 | 描述 | 初始值 |

|

| [31:2] | - | - |

| t_DQSS | [1:0] | 写入DQS的时钟周期 | 1 |

8) T_MRD寄存器(P1T_MRD)

| P1T_MRD | 位 | 描述 | 初始值 |

|

| [31:7] | - | - |

| t_ MRD | [6:0] | 设置模式寄存器命令时间(内存时钟周期为单位) | 0x02 |

9) T_RAS寄存器(P1T_RAS)

| P1T_RAS | 位 | 描述 | 初始值 |

|

| [31:4] | - | - |

| t_RAS | [3:0] | 设置行地址选通到预充电操作延迟时间(内存时钟周期为单位) | 0x7 |

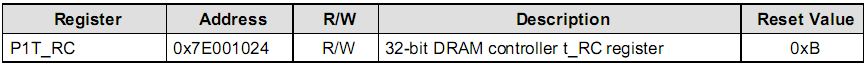

10) T_RC寄存器(P1T_RC)

| P1T_RC | 位 | 描述 | 初始值 |

|

| [31:4] | - | - |

| t_RC | [3:0] | 设置激活内存Bank x到激活另外一个Bank x操作的延迟时间(内存时钟周期为单位) | 0xB |

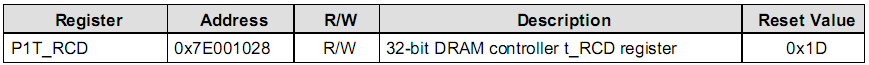

11) T_RCD寄存器(P1T_RCD)

| P1T_RCD | 位 | 描述 | 初始值 |

|

| [31:6] | - | - |

| Scheduled_RCD | [5:3] | 设置t_RCD-3 | 011 |

| t_RCD | [2:0] | 设置RAS到CAS操作的最小延迟时间(内存时钟周期为单位) | 101 |

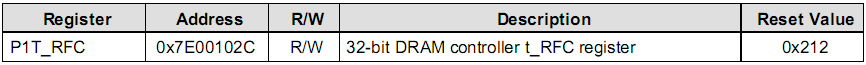

12) T_RFC寄存器(P1T_RFC)

| P1T_RFC | 位 | 描述 | 初始值 |

|

| [31:10] | - | - |

| Scheduled_RFC | [9:5] | 设置t_RFC-3 | 0x10 |

| t_RFC | [4:0] | 设置自动刷新命令操作延迟时间(内存时钟周期为单位) | 0x12 |

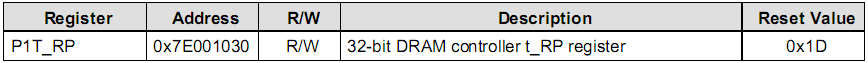

13) T_RP寄存器(P1T_RP)

| P1T_RP | 位 | 描述 | 初始值 |

|

| [31:6] | - | - |

| Scheduled_RP | [5:3] | 设置t_RP-3 | 011 |

| t_RFC | [2:0] | 设置预充电到RAS操作的延迟时间(内存时钟周期为单位) | 101 |

14) T_RRD寄存器(P1T_RRD)

| P1T_ RRD | 位 | 描述 | 初始值 |

|

| [31:4] | - | - |

| t_RRD | [3:0] | 设置激活内存Bank x到激活内存Bank y操作的延迟时间(内存时钟周期为单位) | 0x2 |

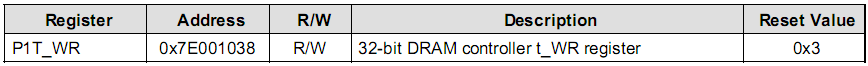

15) T_WR寄存器(P1T_WR)

| P1T_ WR | 位 | 描述 | 初始值 |

|

| [31:3] | - | - |

| t_WR | [2:0] | 设置写入数据到预充电操作的延迟时间(内存时钟周期为单位) | 011 |

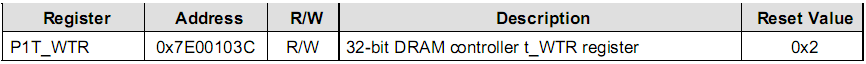

16) T_WTR寄存器(P1T_WTR)

| P1T_ WTR | 位 | 描述 | 初始值 |

|

| [31:3] | - | - |

| t_WTR | [2:0] | 设置写入数据到读取数据操作的延迟时间(内存时钟周期为单位) | 011 |

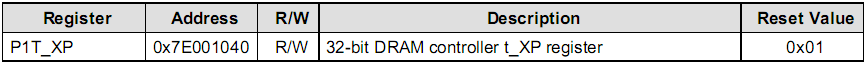

17) T_XP寄存器(P1T_XP)

| P1T_ XP | 位 | 描述 | 初始值 |

|

| [31:8] | - | - |

| t_XP | [7:0] | 设置退出关闭电源命令的延迟时间(内存时钟周期为单位) | 0x1 |

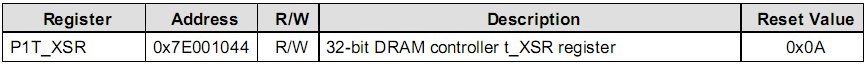

18) T_XSR寄存器(P1T_XSR)

| P1T_ XSR | 位 | 描述 | 初始值 |

|

| [31:8] | - | - |

| t_XSR | [7:0] | 设置退出自刷新命令的延迟时间(内存时钟周期为单位) | 0xA |

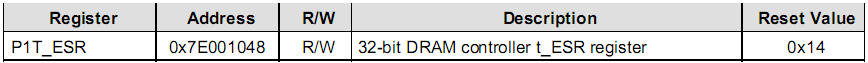

19) T_ESR寄存器(P1T_ESR)

| P1T_ ESR | 位 | 描述 | 初始值 |

|

| [31:8] | - | - |

| t_ESR | [7:0] | 设置自刷新命令的延迟时间(内存时钟周期为单位) | 0x14 |

内存初始化代码:

(开发环境为ADS1.2)

++++++++++++++++++++++++++++++++++++++++++

本文系本站原创,欢迎转载! 转载请注明出处:

145

145

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?