最近在学习uboot的移植,也看过很多文章,但多多少少都有些不尽人意的地方,自己手动移植也出现过种种问题。尤其是不能对移植的过程有很好的理解,基于这个原因,我打算深入学习一下uboot的移植过程,并对移植过程详细记录,方便那些想学习uboot移植确找不到门路的新手。

鉴于本人也是新手,文章难免有疏漏之处,也有自己不是很明白的地方,已经标记出来,还望各位多多指教。如果觉得好想转载,请注明出处。

一、建立自己的开发板并测试编译

1、建立自己的板文件(夹):

1) 首先找到uboot源码包,进入uboot目录。

找到与开发板最相近的一个目标板,在此基础上进行修改。我们选择SMDK2410:

[root@local 02:53/home/zhang]# cd uboot-2010.06/board/samsung/

[root@local 02:53/home/zhang/uboot-2010.06/board/samsung]# ls

goni smdk2400 smdk2410 smdk6400 smdkc100

2) 建立自己的目标板文件(夹):

[root@local 02:53/home/zhang/uboot-2010.06/board/samsung]# cp -R smdk2410/ tq2440

[root@local 02:56/home/zhang/uboot-2010.06/board/samsung]# ls

goni smdk2400 smdk2410 smdk6400 smdkc100 tq2440

修改文件名:

[root@local 03:00/home/zhang/uboot-2010.06/board/samsung/tq2440]# mv smdk2410.c tq2440.c

[root@local 03:00/home/zhang/uboot-2010.06/board/samsung/tq2440]# ls

config.mk flash.c lowlevel_init.S Makefile tq2440.c

修改Makefile,如下图:

![]()

建立头文件,在include/configs/目录下:

[root@local 03:05/home/zhang/uboot-2010.06/include/configs]# cp smdk2410.h tq2440.h

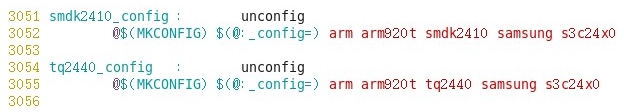

3) 修改根目录下的Makefile文件,添加配置:

复制smdk2410的配置,添加tq2440的两行配置,如下图:

说明:

arm:CPU的体系架构,对应uboot/arch/arm目录

arm920t: CPU的类型,对应uboot/arch/arm/cpu/arm920t/目录(每个版本uboot位置不尽相同)

tq2440: 自己的板文件目录

samsung: 自己的板文件目录的上级目录,如果是在uboot/board目录下,则设置为NULL

s3c24x0: CPU型号,SOC片上系统

指定交叉编译工具,如下图:

4) 测试编译:

[root@local 03:22/home/zhang/uboot-2010.06]# make distclean

[root@local 03:23 /home/zhang/uboot-2010.06]# maketq2440_config

Configuring fortq2440 board...

[root@local 03:25 /home/zhang/uboot-2010.06]# make all

如果没有错误就说明uboot和交叉编译工具基本上没问题了,这时候生成了uboot.bin。但是这时候实际生成的是针对smdk2410的uboot,下面对其进行修改,以适应tq2440。

二、Uboot启动过程分析

这一阶段本来打算写的,由于自己还没有弄的很明白,怕写出来出错会误导很多人,所以干脆就不写了,推荐大家去看一下韦东山的视频第9课,专门讲uboot的,能获取很大帮助。这里给出下载网址:http://dl.dbank.com/c03o1ebwlo

三、修改Uboot启动TQ2440开发板

1、修改SDRAM的配置

修改board/samsung/tq2440/lowlevel_init.S文件,这里是ARM的几个Bank(片选)总线宽度以及是否是能wait、UB/LB功能,需要参考硬件原理图的连接配置方式 :

54 #define B1_BWSCON (DW16) //(DW32)

55 #define B2_BWSCON (DW16)

56 #define B3_BWSCON (DW16 + WAIT + UBLB)

57 #define B4_BWSCON (DW16)

58 #defineB5_BWSCON (DW8) //)(DW16)

59 #define B6_BWSCON (DW32)

60 #define B7_BWSCON (DW32)

还有126行,SDRAM refresh control register,REFRESH,时钟刷新寄存器,根据具体情况需要修改其中某些位,这里仅修改了Refresh count位:

REFRESH[10:0]:

SDRAMrefresh count value. Refer to chapter 6 SDRAM refresh controller bus prioritysection.

Refresh period = (211-refresh_count+1)/HCLK

Ex) Ifrefresh period is 7.8 us and HCLK is 100MHz, the refresh count is as follows:

Refreshcount = 211 + 1 - 100x7.8 = 1269(0x4F5)。page210

126 #define REFCNT 0x4f4 /*period=7.8125us,HCLK=100Mhz,(2048+1-7.8125*100)=0x4F4*/

2、时钟一些概念与原理

1) 时钟比的概念

经常会看到这么一个时钟关系:FCLK:HCLK:PCLK=1:4:8,其意义是:HCLK=FCLK/4,PCLK=FCLK/8,在手册242页定义:

FCLK: FCLK is usedby ARM920T. 内核时钟,即主频

HCLK: HCLK is usedfor AHB bus, which is used by the ARM920T, the memory controller, the interruptcontroller, the LCD. 总线时钟,包括USB总线时钟。

PCLK: PCLK is usedfor APB bus, which is used by the peripherals such as WDT, IIS, I2C, PWM timer,MMC interface ADC, UART, GPIO, RTC and SPI. IO接口时钟,例如串口的时钟就是从这里来的。

2) 时钟寄存器配置,page254

MPLL ControlRegister:

MPLL = (2 * m *Fin) / (p * 2s)

m = (MDIV + 8), p= (PDIV + 2), s = SDIV

UPLL ControlRegister:

UPLL = (m * Fin) /(p * 2s)

m = (MDIV + 8), p= (PDIV + 2), s = SDIV

其中MDIV、PDIV、SDIV是MPLLCON、UPLLCON寄存器的分频因子。由于计算比较复杂,手册上一般都会给出几种常见的分频值,pege255。

例如:

| Input Frequency |

Output Frequency |

MDIV |

PDIV |

SDIV |

| 12.0000MHZ |

405.00MHZ |

127(0x7f) |

2 |

1 |

| 12.0000MHZ |

48.00MHZ(UPLLCON) |

56(0x38) |

2 |

2 |

即:

MPLLCON[19:12] =0x7f

MPLLCON[9:4] = 2

MPLLCON[1:0] = 1

未指明的位清零,由此计算出:MPLLCON=0x7F021,UPLLCON=0x38022

NOTE: Whenyou set MPLL&UPLL values, you have to set the UPLL value first and then theMPLL value. (Needs intervals approximately 7 NOP)。先配置UPLLCON后配置MPLLCON。

3) 时钟比的控制

设置好了FCLK=405MHZ,USB PLLCLK=48MHZ,设置FCLK:HCLK:PCLK=1:4:8,即HCLK=FCLK/4,PCLK=FCLK/8,时钟频率按照第二步计算,由此可以推算出:

CLKDIVN寄存器的值为:0x5。

CAMDIVN[9] = 0(HCLK4_HALF,由于HCLK=FCLK/4),该位初始值为0

HDIVN=2,page242。

NOTE:If HDIVN is not 0, the CPU bus mode

本文详细记录了移植Uboot2010.06到TQ2440开发板的过程,包括建立板文件、修改配置、时钟配置、Flash支持以及Nand读写等功能的实现。通过建立自己的开发板文件,修改Makefile,设置时钟分频和模式,以及添加NAND Flash控制器的硬件支持,最终实现了Uboot的移植和验证。

本文详细记录了移植Uboot2010.06到TQ2440开发板的过程,包括建立板文件、修改配置、时钟配置、Flash支持以及Nand读写等功能的实现。通过建立自己的开发板文件,修改Makefile,设置时钟分频和模式,以及添加NAND Flash控制器的硬件支持,最终实现了Uboot的移植和验证。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4908

4908

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?