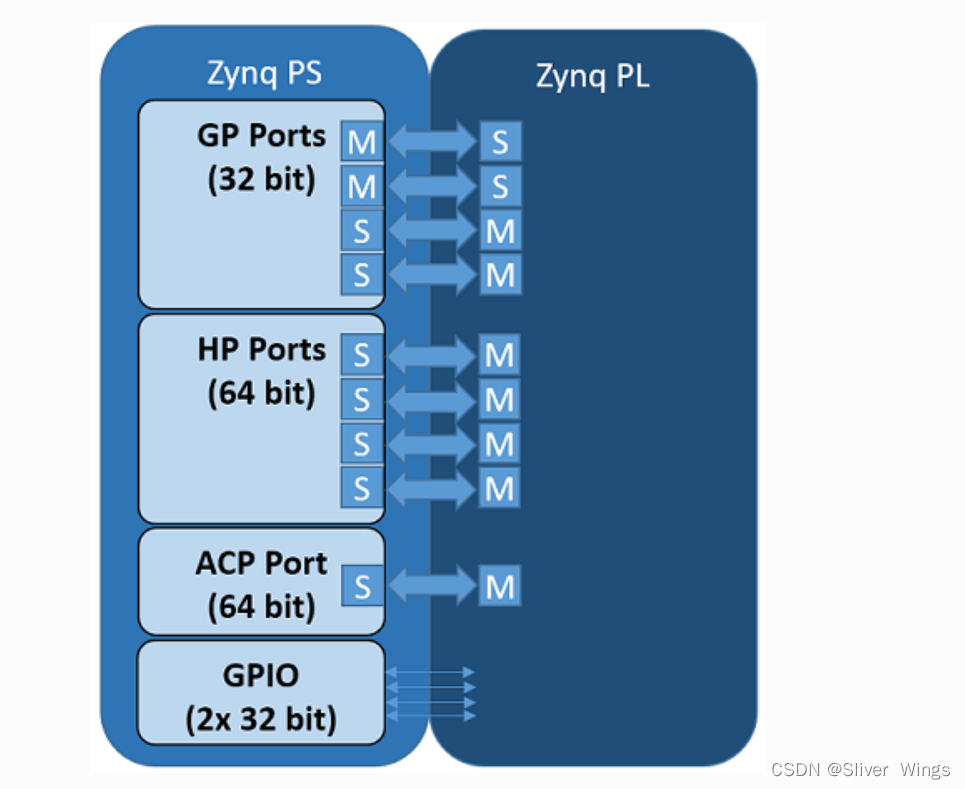

PYNQ的PS、PL接口接口

PS:(Processing System),ZYNQ可以大概分为ARM和FPGA两部分,PS就是ARM的SOC部分,是整块板子的处理系统。

PL:(Progarmmable Logic),意为可编程逻辑,也就是ZYNQ上的FPGA部分。

PS和PL之间采用AXI进行数据交互。连接到AXI主端口的IP不受PS的直接控制。AXI主端口允许IP直接访问DRAM。在这样做之前,应该分配内存给IP使用。可以使用allocate函数来完成这项工作。为了在PS DRAM和IP之间实现更高性能的数据传输,可以使用DMAs。PYNQ提供了一个DMA类。

常用这两类来控制。

权重与偏差的复制

分配空间

weight_base_buffer = allocate(shape=(25470896,), dtype=np.uint32)#分配空间

print("100M",weight_base_buffer.physical_address)

WEIGHT_BASE = weight_base_buffer.physical_address

bate_base_buffer = allocate(shape=(5381,), dtype=np.uint32)

print("32k",bate_base_buffer.physical_address)

BETA_BASE=bate_base_buffer.physical_address

img_base_buffer = allocate(shape=(4194304,), dtype=np.int32)

print("16M",img_base_buffer.physical_address)

IMG_MEM = img_base_buffer.physical_address

数据复制

params_wight = np.fromfile("weightsv2_comb_reorg_ap16.bin", dtype=np.uint32)#复制

np.copyto(weight_base_buffer, params_wight)

print("yolov2_weight copy ok\n")

del params_wight

gc.collect()#回收空间,对多余的垃圾进行回收

params_bais = np.fromfile("biasv2_comb_ap16.bin", dtype=np.uint32)

np.copyto(bate_base_buffer, params_bais)

print("yolov2_bais copy ok\n")

del params_bais

gc.collect()

653

653

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?