svpwm verilog实现带死区设置,没有任何IP核,移植方便

ID:785000669113759918

ultraTech实验室

在现代电力电子系统中,无论是交流变频器、直流电机驱动器还是电力传递装置,都离不开功率开关器件的应用。这些功率开关器件的控制方法有很多种,其中一种被广泛采用的方法是空间矢量脉宽调制(Space Vector Pulse Width Modulation,SVPWM)。SVPWM是一种用于控制三相电压反馈信号的技术,通过调制特定的脉冲宽度和频率,可以实现电力系统的无级调速和运行控制。

为了实现SVPWM的控制,通常会使用硬件加速器,如FPGA(Field-Programmable Gate Array)或ASIC(Application-Specific Integrated Circuit),然而,这些硬件加速器的使用会增加系统的复杂性和成本。为了简化和降低系统的成本,一种基于纯软件实现的SVPWM方案应运而生。在这个方案中,我们使用了Verilog语言来实现SVPWM控制,而且还引入了死区时间的设置。

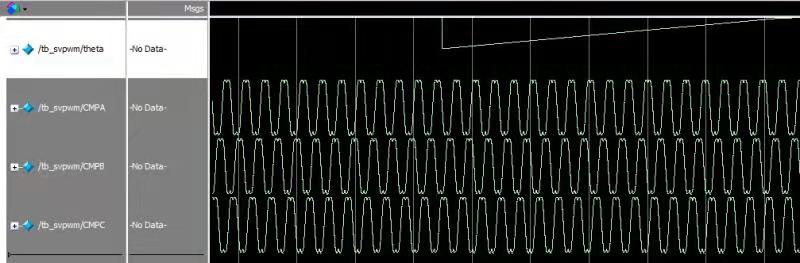

Verilog是一种硬件描述语言(Hardware Description Language,HDL),它可以描述和建模数字电路的行为和结构。我们利用Verilog中的逻辑门、时钟和触发器等基本构建模块来实现SVPWM的控制逻辑。具体而言,我们使用了三角波的周期性控制来生成电压矢量,然后将其转换为脉冲信号输出。为了防止两个相邻的开关同时导通而引起故障,我们在Verilog代码中引入了死区时间设置。

死区时间是指在两个相邻的开关导通或截止之间存在的一段时间,它可以有效地减少功率开关器件的损耗和电流漏泄。在Verilog实现中,我们可以通过在输出信号的改变之前或之后插入一个固定时间的延迟来实现死区时间的设置。这种方式可以很好地保证开关器件的稳定性和可靠性。

与传统的SVPWM控制方法相比,我们的Verilog实现方案具有以下优势。首先,我们完全依赖软件进行控制,无需任何IP核或硬件加速器的支持。这意味着我们可以在通用计算平台上实现SVPWM控制,大大简化了系统的设计和开发流程。其次,我们引入了死区时间设置,有效地提高了系统的稳定性和可靠性。最后,我们的Verilog实现方案具有很好的可移植性,可以轻松地在不同的平台和系统中进行移植和集成。

总之,通过使用Verilog语言实现SVPWM控制,并结合死区时间的设置,我们可以在不依赖任何IP核或硬件加速器的情况下,轻松实现电力电子系统的无级调速和运行控制。这种基于纯软件的实现方案具有简单、灵活和可移植的特点,可以大大降低系统的设计和开发成本,为工程师们提供了一种方便、高效的解决方案。希望这篇文章对您在SVPWM控制的应用和开发中有所帮助。

相关的代码,程序地址如下:http://nodep.cn/669113759918.html

443

443

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?