摘要: USB已通过UTMI快速推出USB2.0方案。

USB已稳坐主流接口宝座,内置USB接口的ASIC、集成电路也如雨后春笋般随着产品创意的衍生而蓬勃发展。有些IC设计公司为了加快产品推出速度,会选择向外购买前端PHY部分的IP(即USB Transceiver Macrocell),再搭配自行设计的后端部分,而UTMI标准接口则是整个集成过程中不可或缺的一环。

要完成前端与后端集成的设计,不难想像在UTM与SIE之间必须有一个共通的标准接口。此标准接口就称为UTMI(USB 2.0 Transceiver Macrocel Interface),规格版本依然是由Intel公司所主导,从2000年起经1.0/1.01/1.02/1.03/1.04/ 1.05版的逐步修正,目前遵循的版本是3/29/2001的1.05版,可以通过下面这个网站来取得相关技术文献:/technology/ usb/spec.htm(图1)。

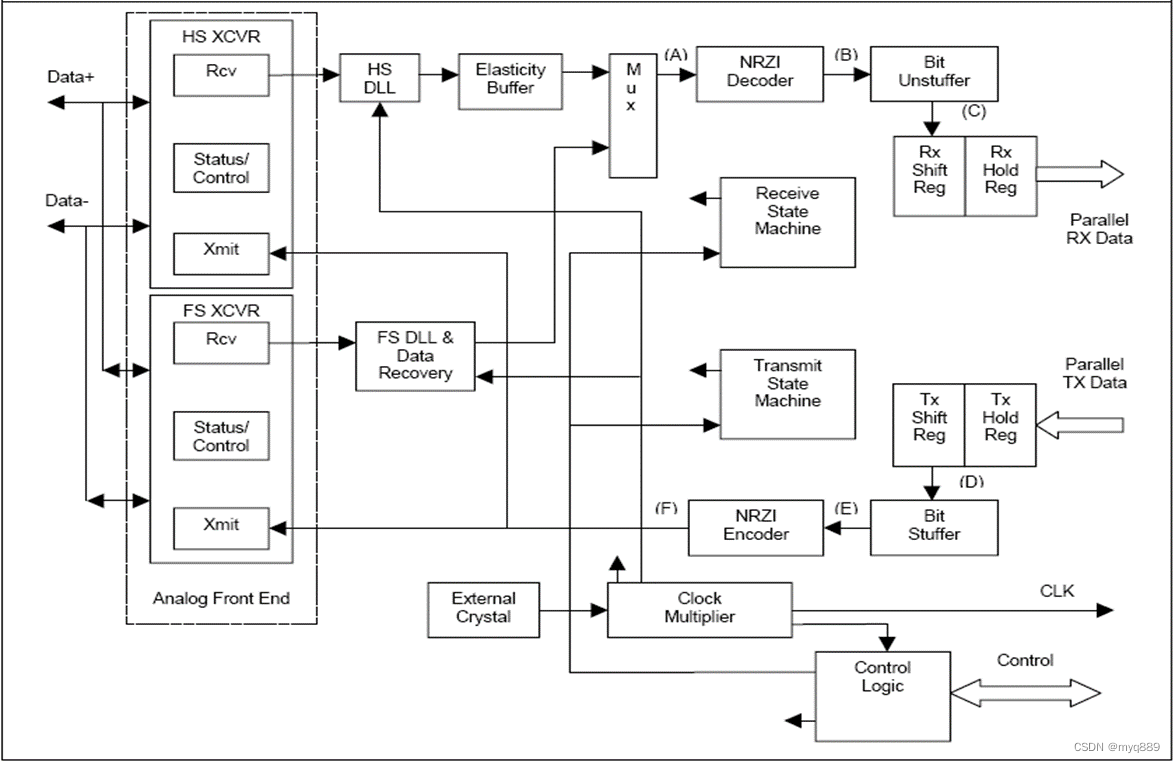

典型的外设装置所用的USB控制器,规格上分为三个功能方块。从最前端说起,顺序为UTM(USB 2.0 Transceiver Macrocell)、SIE(SerialInterface Engine),然后是后端的逻辑控制部分(图2)。

UTM就是底层的收发器,负责USB总线上协议与信号的处理。主要的工作任务当然离不开数据的串行化(Serialization)、数据的解串(Deserialization)、位填充(Bit Stuffing)、时钟恢复(Clock Recovery)以及达成同步(Synchronization)等USB接口所规定的法则。

UTMI的设计有个原则。依据数据传输速率,可以分为支持HS/FS、仅支持FS与支持LS三种。仅采用单一的SIE就足以搭配任何传输速率的收发器。当然,SYNC/EOP的产生与检查也是其职责 之一。

对于HS/FS双模式的支持,顾名思义就是可以操作在480Mbps的HS模式12Mbps的FS模式下。还要考虑终端阻抗的切换问题,因为支持USB 2.0 HS的外设有很多机会插入传统USB 1.1的主 机Host端,甚至传统的HUB装置。在仅支持FS与仅支持LS的情况,就没有速率选择的问题,也就 无需存在选择功用的控制信号。请注意USB 2.0收发器是利用“SuspendM”信号进入低功率省电模式(图3)。

SIE功能方块可进一步分成控制逻辑与端点(End-point)逻辑部分。USB数据交易(Transaction)的打包识别与顺序的状态机(State Machine)就是担任控制逻辑的工作,这是操作任何USB接口必要的功能。端点(Endpoint)逻辑部分会随着装置的不同、端点的形式与数量的差异而有所变化。

描述UTMI信号

UTMI的信号就是该规格的 精华,规格上将UTMI的信号分类来讨论。第一部分就是系统接口信号:

◆ “CLK”时钟输出信号,60MHz=HS/FS有8位接口,30MHz=HS/FS有16位接口,48MHz=FS Only有8位接口,6MHz=LS Only有8位接口。 正常时钟的准确度规定范围是 ±500ppm。

◆ “Reset”复位信号,复位UTM的所有的State Machine。

◆“XcvrSelect”输入信号等于 Transceiver Select的意思,用来选择HS或FS模式。规则是逻辑0使能HS收发器,逻辑1则是使能FS收发器。

◆“TermSelect”输入信号等于 Termination Select的意思。逻辑0是使能HS模式,FS驱动器在USB接口上驱动SE0状态,并且提供50Ω到地的终端阻抗,然后在接口上生成HS Idle状态。若是处于FS模式,该信号会在D+信号上启动1.5KΩ的拉高电阻,然后在接口上生成FS Idle状态。依据规格指定,FS Idle状态与HS Idle状态是不同的。

◆ “SuspendM”是暂停输入信号。USB接口上只要3ms没有任何活动,就进入暂停(Suspend)模式。既然能够暂停,当然也必须能回到重启(Resume)才能维持正常的运作。

◆ 时钟信号相互同步,这样既可以减少SIE不必要的转换,同时可以确保时序与数据输出一致(表1)。请注意SE1状态在USB 2.0规格中是不合法的接口状态。但是在UTM中可作为调试用途。

◆“OpMode[0]”与“OpMode[1]”输入信号,表现为操作模式“Operational Mode”(表2)。

第二部分就是USB接口信号,即是DP与DM信号,分别对应于D+与D-信号。

第三部分是“Vendor Control Signals”,这些信号是针对错误、状态与控制提供信息,且必须维持与“CLK”信号同步,并与数据信号线维持同样的时序关系。对于收发器来说,这些信号是选项,但是对于SIE而言却是必要的。系统软件才能够访问这些寄存器,并进行细节上的诊断与错误分析(图4)。

寄存器基本上是两个,一个是8位的“Vendor Status”寄存器,是Macrocell的输出信号,可以用来告知SIE收发器内部的信息,典型的例子如“CLK Usable”、“Squelch”与错误码等。另一个是4位的“Vendor Control”寄存器,是Macrocell的输入信号。

第四部分是数据的接口信号,可以有8位接口(图5)与16位接口(图6)之分。16位接口适合用于使用电池或撷取Bus-powered的装置以及FPGA的应用发展。对于要求集成电路引脚数目少的场合与ASIC应用发展,就可以使用8位接口。至于接口采用双向与否,则提供了另一种设计上的弹性(图7、图8)。因此,数据接口要区分发送与接收。比如说,“TXReady”输出信号意味着“Transmit Data Ready”,UTM就有责任将SIE送来的DataIn总线上的数据填充“TX Holding Register”。

“RXActive”输出信号意味着“Receive Active”,表示接收的状态机已经检测到SYNC位。同时,SIE就是利用“RXActive”来度量打包与打包之间的间隙。因此,正确地反映USB接口上的状态是极为重要的考虑要素。

这样就可以用几张图将前面所述做个摘要。首先,UTMI的信号可以归纳成四类:

◆ Reset/Clock信号

◆ 数据信号:RxValid/RxData/TxValid/TxData/TxReady

◆ 控制信号:TermSel/Suspend/XcvrSel/OpMode

◆ 状态信号:LineState/RxActive/RxError

其次,一些细节上的问题还是要多加注意。“LineState”可以作为Timer用(图9)。“RxActive”(图10)只有在接收的情况下才启动。同时,在发送时,一定要禁止“RxValid”(图11)的启动。当操作模式处于没有位填充的情况下,“TxReady”(图12)最好维持在逻辑高电平的状态。

分析UTM功能块

其次,针对UTM块图(图13)中的各个部分做简要说明。

“Clock Multiplier”区块

该模块的主要职责是产生UTM的内部时钟以及“CLK”输出信号。所有的数据传送信号都必须与“CLK”输出信号同步。

第一种情况针对HS/FS激活的场合。对于HS模式来说,一个“CLK”的周期就等于一个字节的时间。当UTMI切换HS模式到FS模式时,“CLK”信号本身并没有改变,即在FS模式之下,每一个位时间是5个“CLK”周期,FS模式字节就需要40个“CLK”周期。但是,如果有一个位填充的情况发生,就会延展到45个“CLK”周期(图14、图15)。“XcvrSelect”信号即是用来决定数据与控制信号的时序是HS模式还是FS模式。

第二种情况是仅支持FS模式的场合,“CLK”信号可以是48MHz。在该模式下,UTM会提供每一个字节32个“CLK”周期。

第三种情况仅支持LS模式,“CLK”信号可以是6MHz,因此在该模式下UTM也会提供每一个字节32个“CLK”周期。

HS DLL(High Speed Delay Line PLL)区块

DLL主要工作是在USB 2.0接口上所接收到的信息中取出时钟与数据,然后送往解串器(Receive De-serializer),而DLL的输出数据必须与局部使用的时钟信号同步。

弹性缓冲器(Elasticity Buffer)区块

任何高速串行总线发送端与接收端要达成两端完全相同的时钟是不可能的任务。因此,必须存在某一种手段或机制来补偿两者之间的容许误差,弹性缓冲器的用途就在于此。

USB接口规格允许±500ppm的时钟误差,即时钟容许误差的计算可以累积到±12位。因此,一个具有24位深度的弹性缓冲器的设计就可以了。如果弹性缓冲器发生溢出(Overflow)或下溢(Underflow)的状况,就可以利用“RXError”信号告知。

多任务(MUX)区块

指HS/FS模式多任务的选择,由“XcvrSelect”输入信号来决定。

NRZI Decoder

NRZI是USB接口上的编码**,接收端有解码的职责。该模块可以操作在HS或FS模式下。

Bit Unstuff Logic区块

该逻辑区块是一个状态机,目的是要将填充位移除掉。如果发现填充位错误,在FS模式下就会生成“RXError”信号。而HS模式却是故意违反位填充法则来生成EOP打包,因此不会生成“RXError”信号。

由于USB接口的位速率是固定的,又有填充位的课题,UTMI与SIE之间的速率可以降低。通常在每接收8个位后会在“DataOut”接口上呈现一个字节,然而,当从数据串中移除8个填充位后,“DataOut”接口上相当于跳过一个字节的时间,为了不使该跳跃字节在“DataOut”接口上发生问题,就必须依靠“RXValid”来完成 (图16)。

Rx Shift/Hold Register区块

该模块包含8个位的移位寄存器与保存寄存器。前者是串行变成并行的转换,后者提供一个字节的缓冲(图17)。

对接收状态机区块,图18是接收状态的详细迁移图。这里提出几个重要的概念:

◆ “RXActive”与“RXValid”信号是在CLK信号的上沿采样的。

◆ 当Macrocell检测到SYNC位后会启动“RXActive”信号。

◆ 当Macrocell检测到EOP打包后会关掉“RXActive”信号。

◆ 当启动“RXActive”信号后,保存寄存器满了时会启动“RXValid”信号。

◆ “RXActive”与“RXValid”两信号都有效的情况下,代表数据有效的状态,SIE就必须准备消化该字节。

总之,对于接收状态图的掌握,要理清(DP/DM)、RXValid、RXActive、RXError与DataOut等众多信号的时序关系,这也是重点所在。

1756

1756

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?