锁相环simulink仿真,1:单同步坐标系锁相环(ssrf-pll),2:对称分量法锁相环(ssrfpll上面加个正序分量提取),3:双dq锁相环(ddsrf-pll),4:双二阶广义积分锁相环(sogi-pll),5:sogi-fll锁相环,6:剔除直流分量的sogi锁相环的simulink仿真

可提供仿真数据和自己搭建模型时的参考文献,仿真数据仅供参考

ID:8715676276247901

Mooncha

锁相环(Phase-Locked Loop,PLL)是一种用于时钟和信号同步的电路或者算法。它在无线通信系统、数据转换以及数字信号处理中得到广泛应用。本文将围绕锁相环的几种常见实现方式进行技术分析,并使用Simulink进行仿真验证。

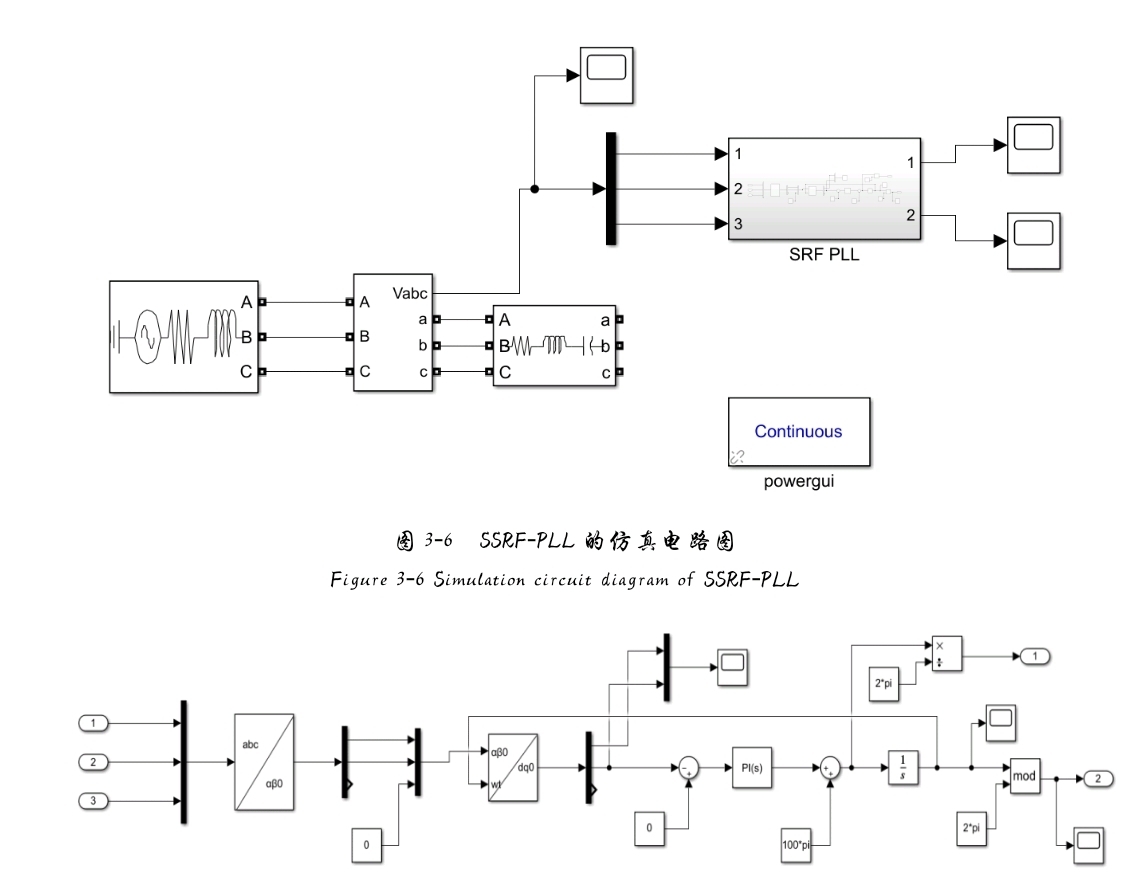

首先,我们介绍单同步坐标系锁相环(SSRF-PLL)。这种锁相环的特点是在单同步坐标系下运行,以实现对输入信号的同步追踪。在SSRF-PLL中,通过比较输入信号与参考信号的相位差,通过环路滤波器和数字控制器的调节,最终实现信号同步。我们可以使用Simulink搭建SSRF-PLL的仿真模型,验证其性能和稳定性。

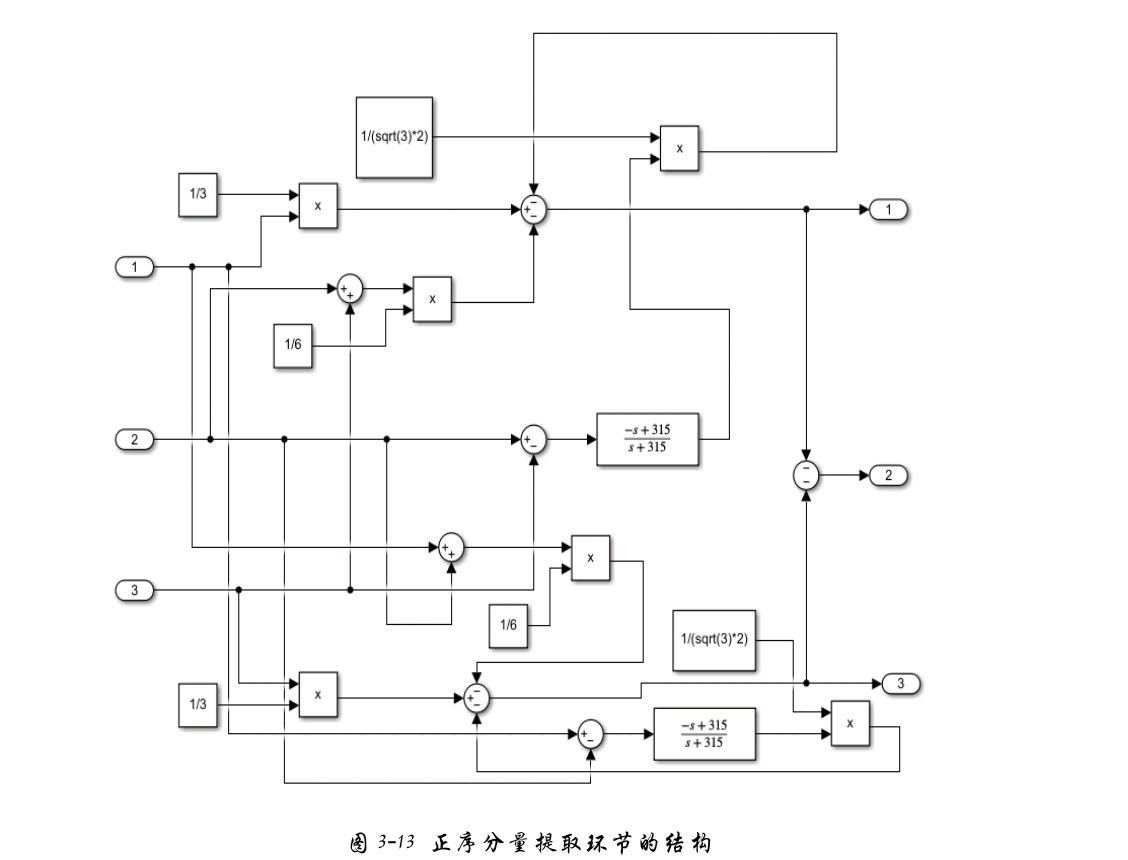

其次,我们研究对称分量法锁相环(SSRF-PLL上面加个正序分量提取)。该锁相环通过提取信号的对称分量来实现信号同步,从而减小非线性失真。在对称分量法锁相环中,通过正序分量提取器提取信号的对称分量,然后通过环路滤波器和数字控制器进行相位调节,以实现信号同步。我们可以通过Simulink搭建仿真模型,并模拟正序分量提取的过程,验证其对信号同步性能的改善。

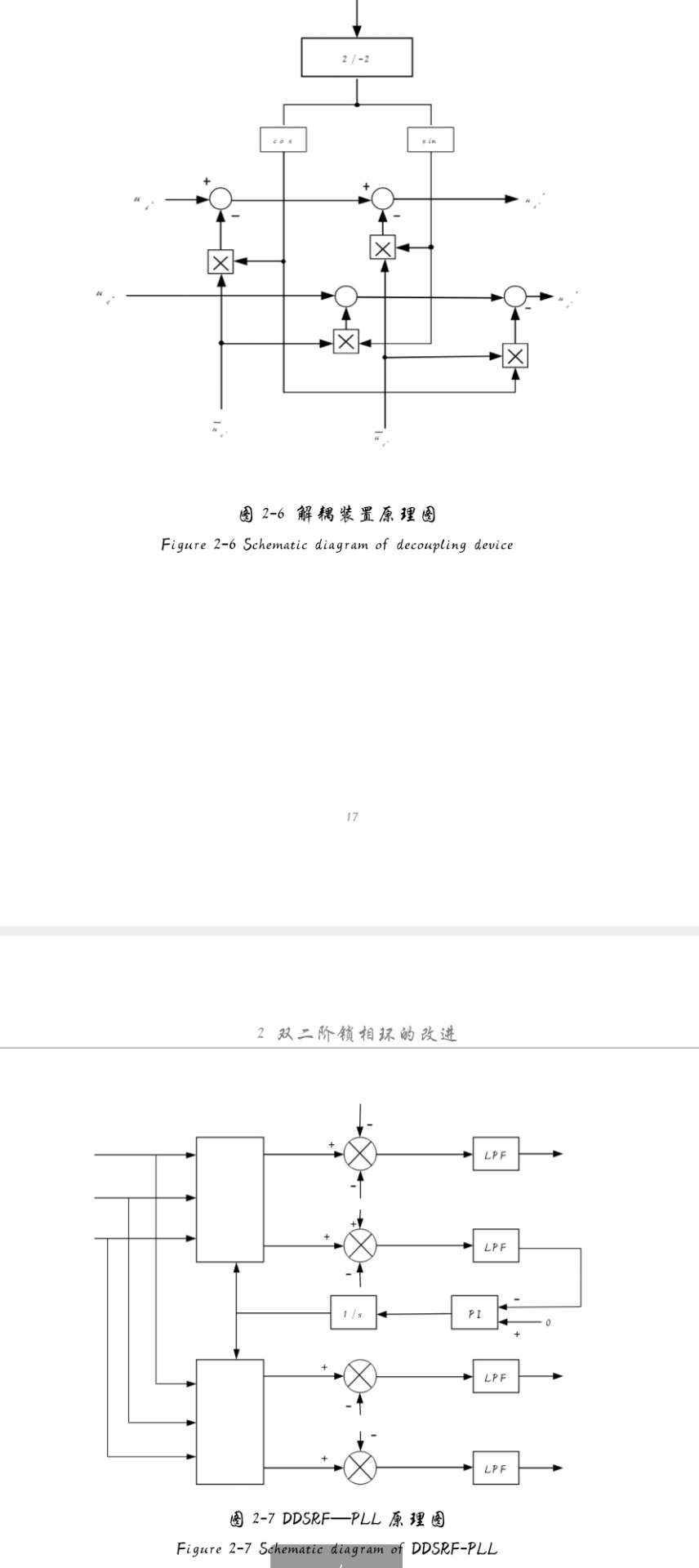

接下来,我们研究双dq锁相环(DDSRF-PLL)。双dq锁相环基于dq坐标系,可以更好地适应非正弦信号的同步需求。在双dq锁相环中,通过dq转换和环路滤波器对信号进行处理,并通过数字控制器进行相位调节,实现信号同步。我们可以使用Simulink搭建双dq锁相环的仿真模型,验证其对非正弦信号的同步性能。

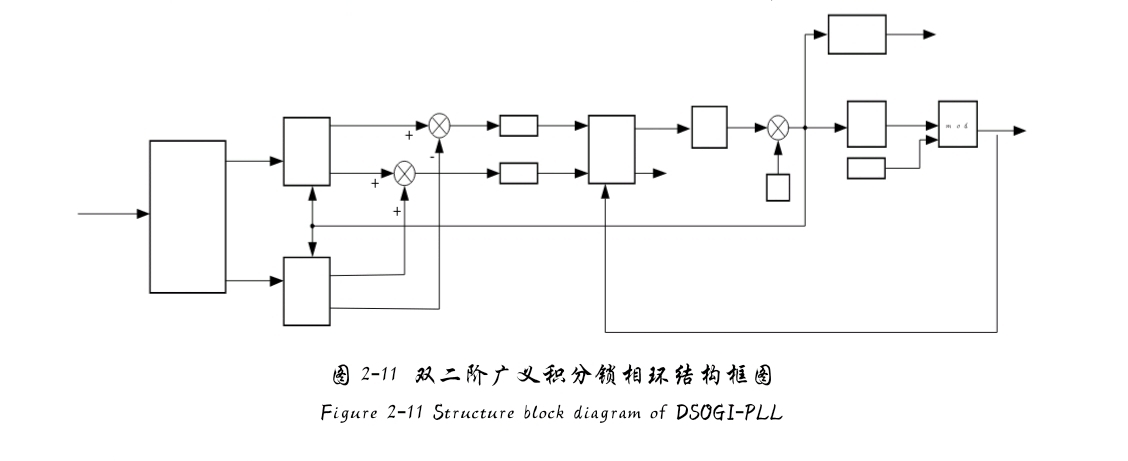

此外,我们也研究双二阶广义积分锁相环(SOGI-PLL)。SOGI-PLL通过引入二阶积分环节,可以更好地抑制输入信号中的交流成分,提高同步精度。在SOGI-PLL中,通过SOGI滤波器和数字控制器对信号进行处理,并通过相位调节实现信号同步。我们可以使用Simulink搭建SOGI-PLL的仿真模型,并验证其对交流成分抑制的效果。

此外,我们还研究了剔除直流分量的SOGI锁相环的Simulink仿真。在该锁相环中,通过引入直流分量的剔除环节,可以更好地适应信号中的直流偏移,提高同步的准确性。我们可以使用Simulink搭建剔除直流分量的SOGI锁相环的仿真模型,并验证其对直流偏移的剔除效果。

综上所述,本文围绕锁相环的几种常见实现方式展开技术分析,并使用Simulink进行仿真验证。通过对所提及锁相环的理论分析和仿真验证,我们可以更深入地理解锁相环的原理和性能,为相关领域的实际应用提供指导。本文所提供的仿真数据和自己搭建模型时的参考文献仅供参考,读者可以结合实际情况进行进一步研究和探索。希望本文对读者在锁相环方面的学习和应用有所帮助。

以上相关代码,程序地址:http://wekup.cn/676276247901.html

5155

5155

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?