1、打开vivado界面,

2、添加并编写 fpga_led.v文件和linux_fpga5.xdc文件.

(测试的开发板为PL侧有四个LED,实验fpga点2个,arm点2个,同时打开PL侧的key输入中断给arm,另一个key给fpga)

fpga_led.v文件为fpga闪烁led的程序,linux_fpga5.xdc为约束文件

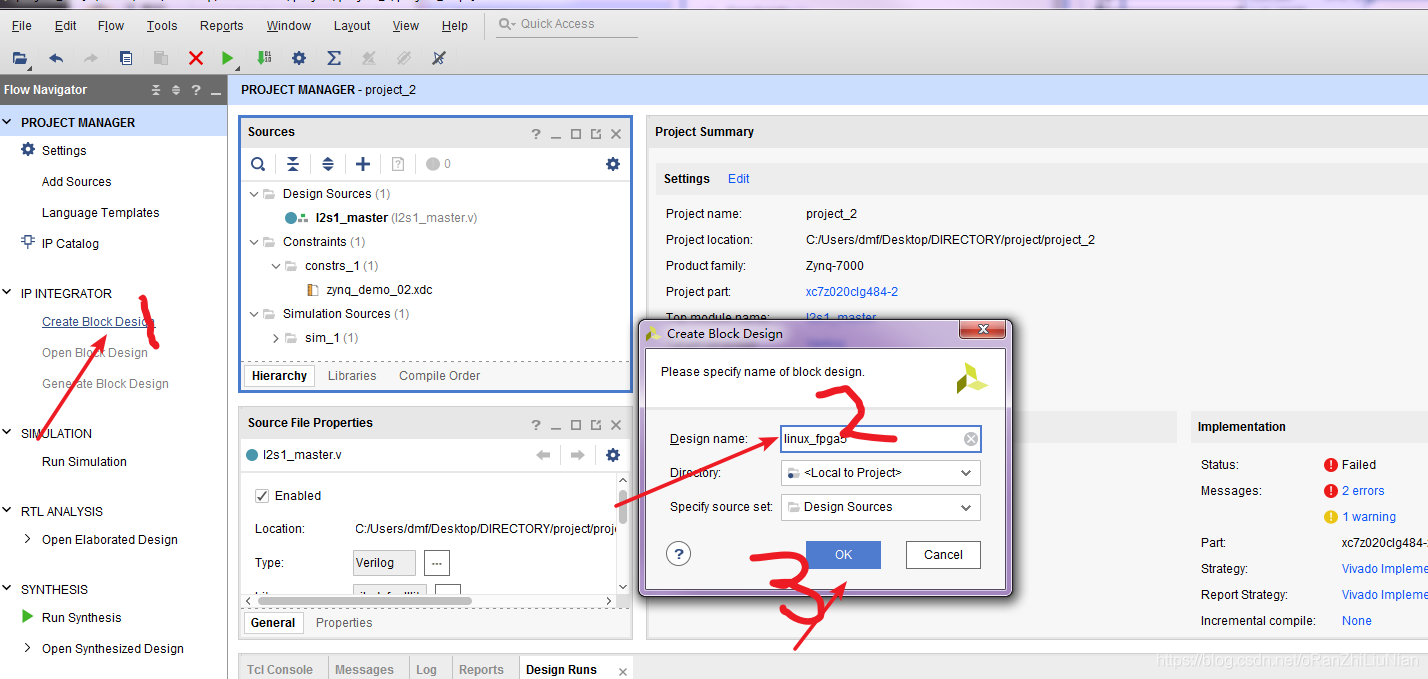

3、点击Create Block Design,

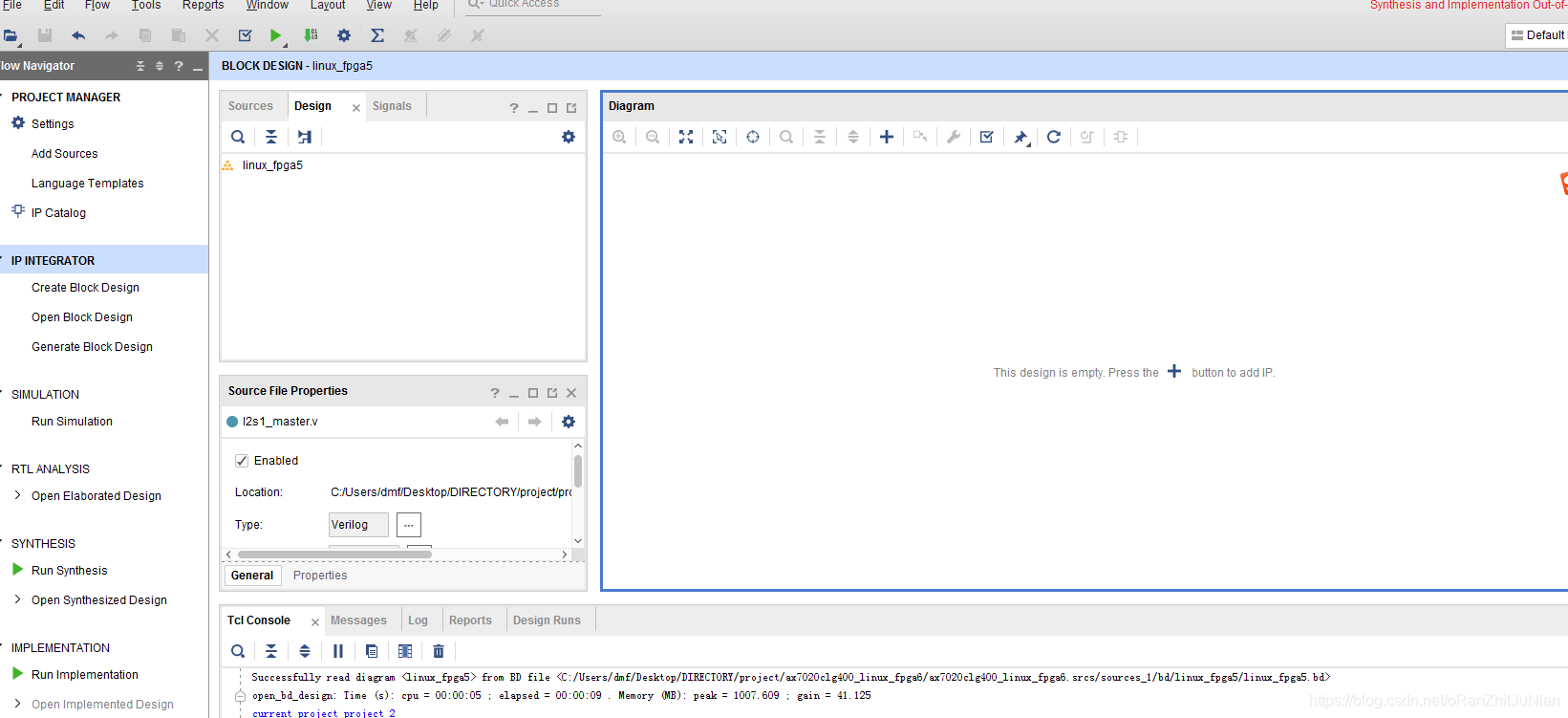

添加block后的界面

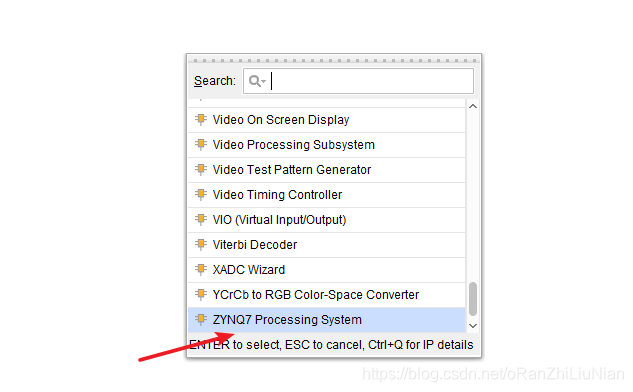

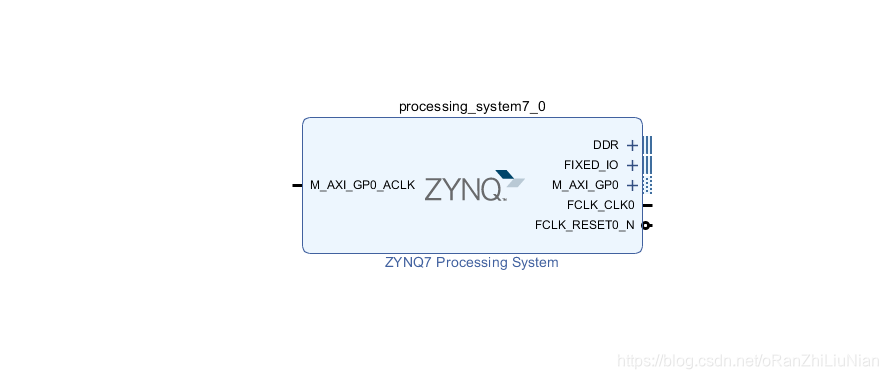

4、新打开的Diagram中空白区域 右键, 点击“”+“”来add IP(或者右键>/添加Ip),选择ZYNQ7 Processing System

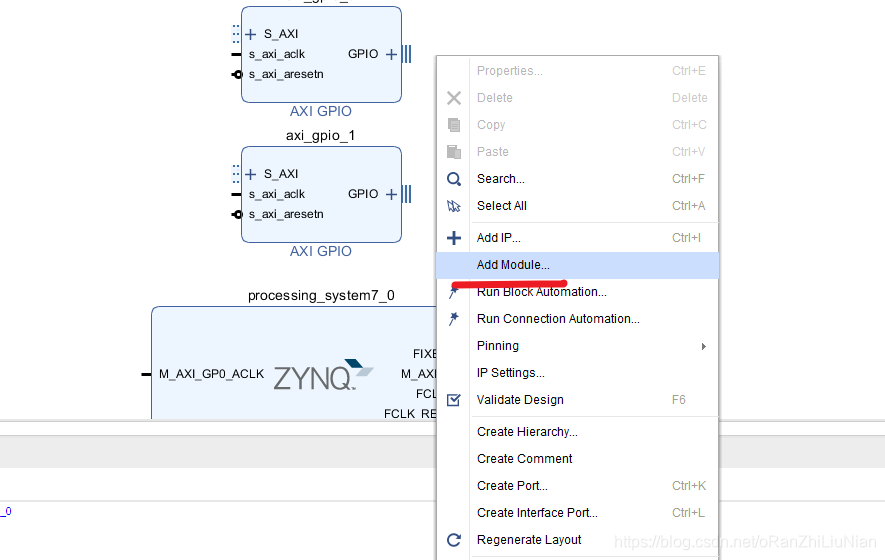

继续右键>/ add ip添加两个AXI GPIO模块

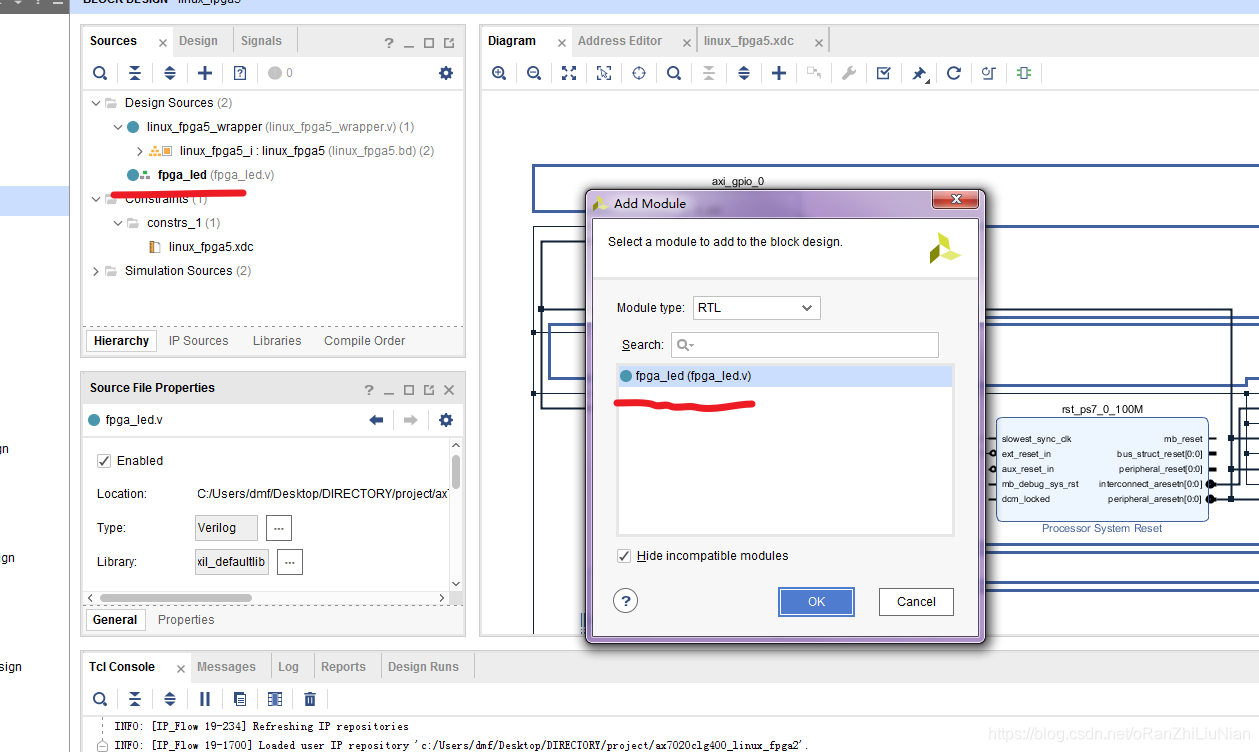

继续右键>/add module,弹出界面可以看到前面写好的fpga_led.v 模块,直接点击OK添加

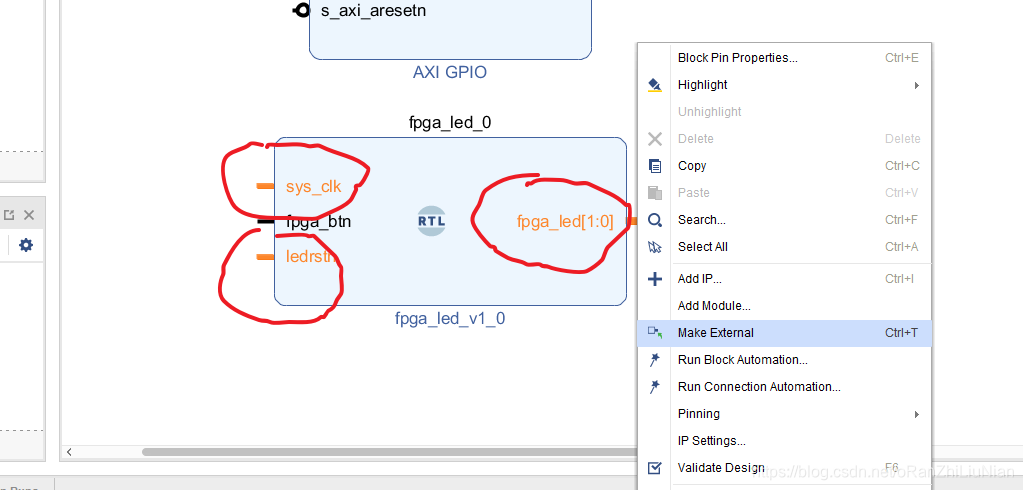

因为FPGA的引脚外界的,这里需要选中相应的pin,右键选择Make External

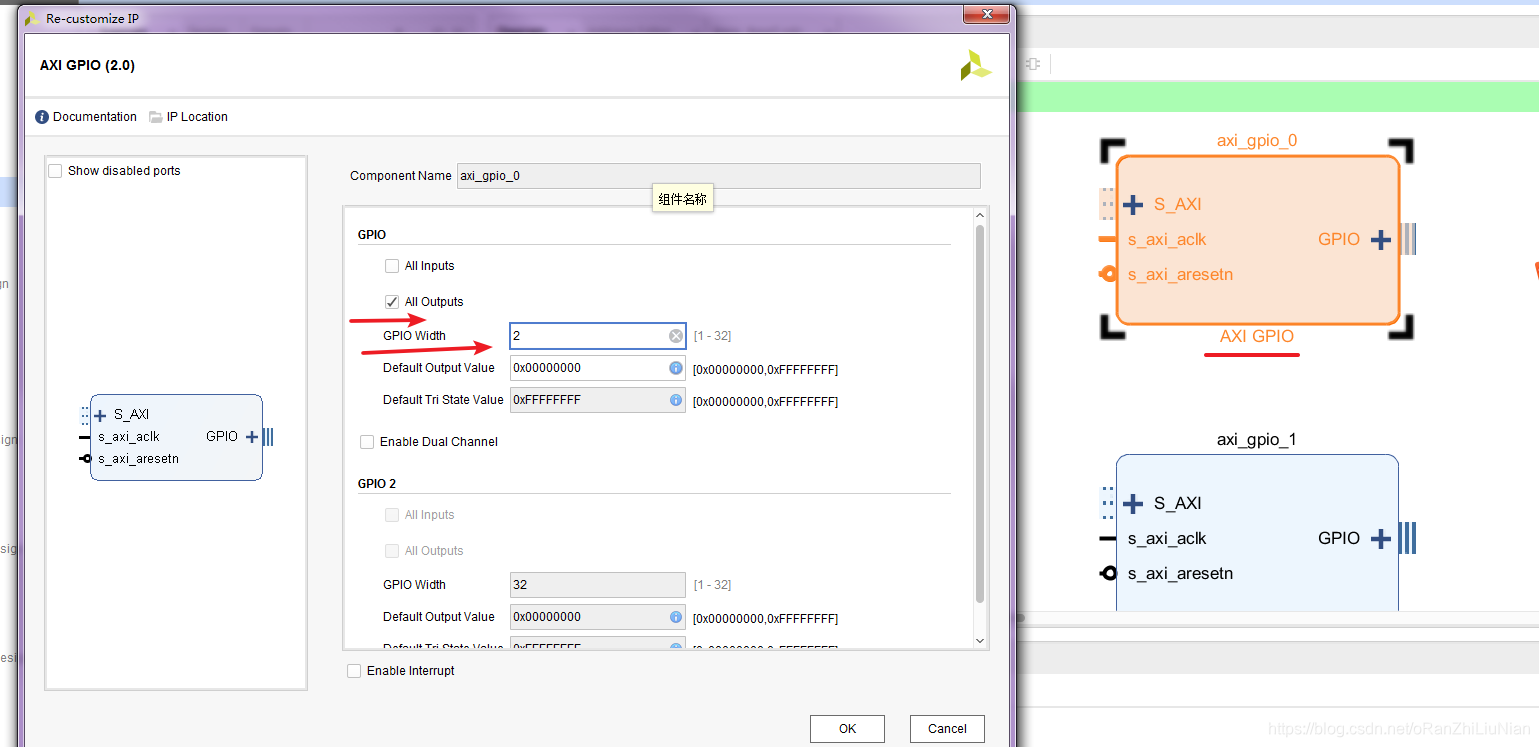

设置axi_gpio_0,双击axi_gpio_0,用于arm控制pl侧的两个led,点OK确认完成

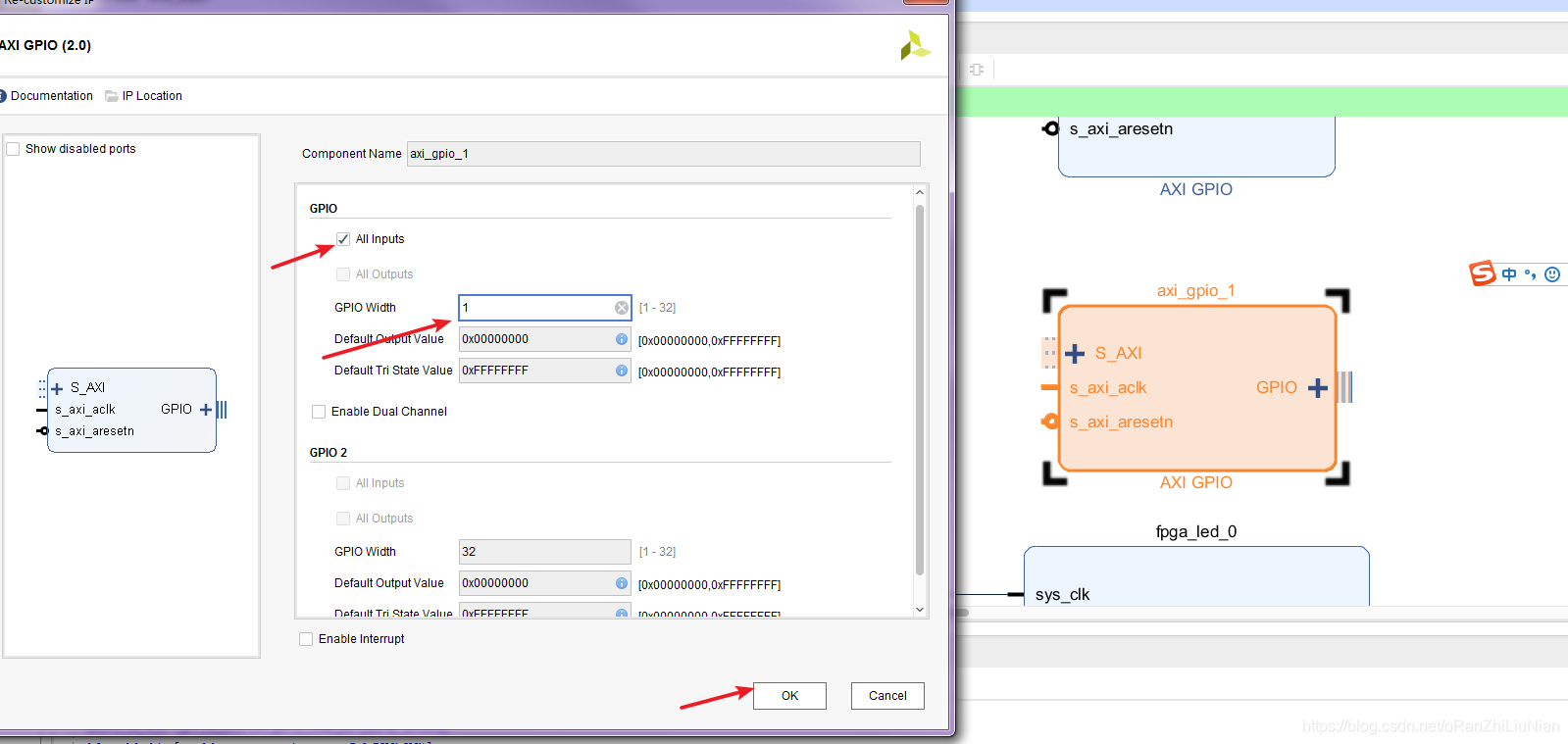

设置axi_gpio_1:双击axi_gpio_1,用于arm接收pl侧的1个key输入,点OK确认完成

双击ZYNQ7 Processing System

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?