1、创建新工程,

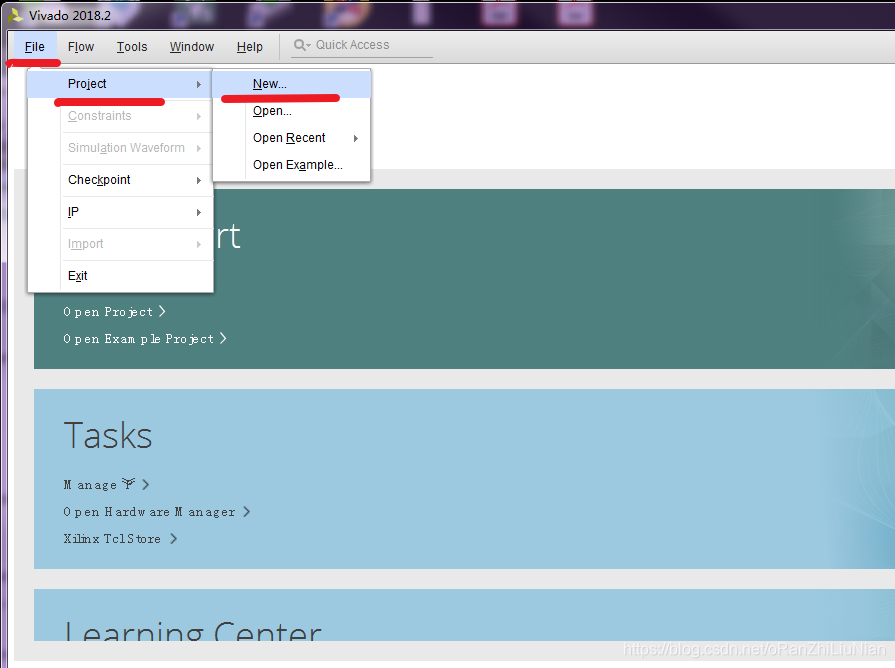

打开vivado,选择 file >> project >>new,

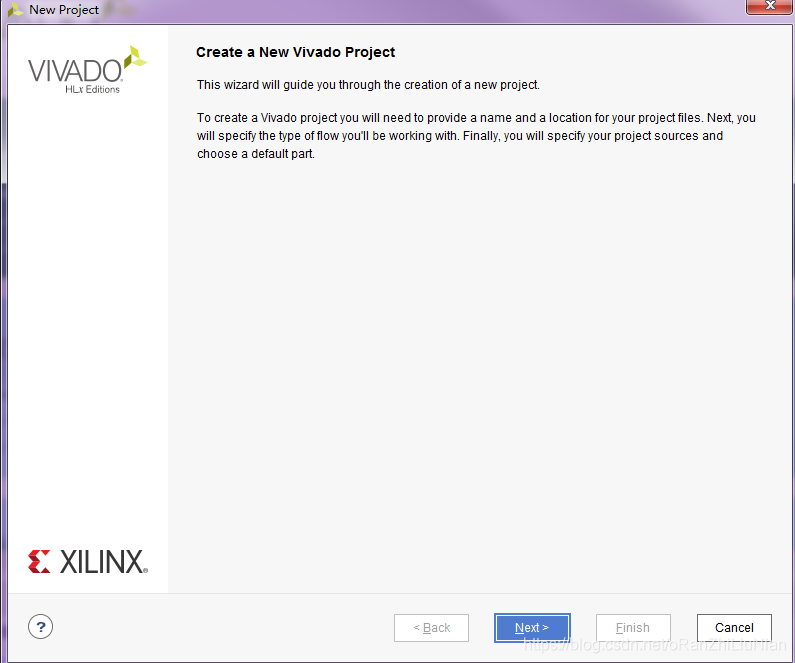

选择next,

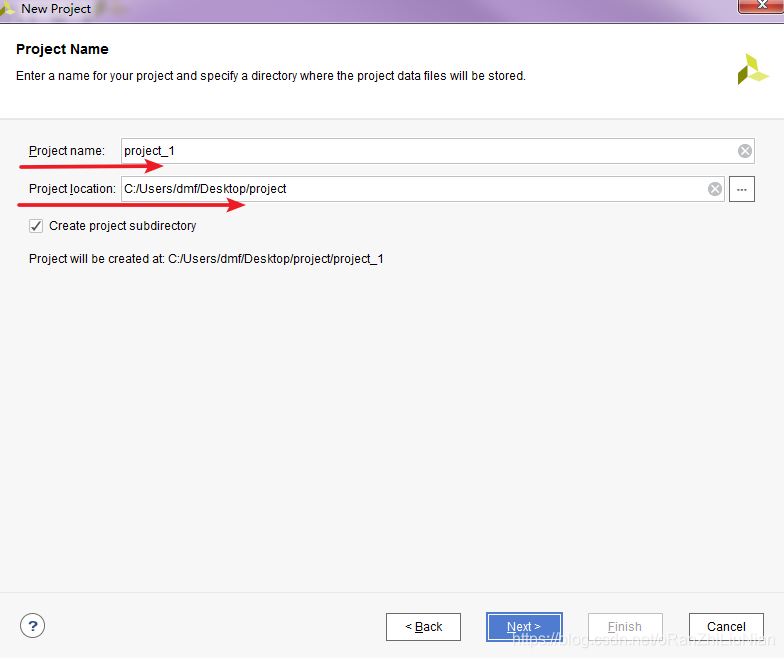

填写工程名字,选择目录

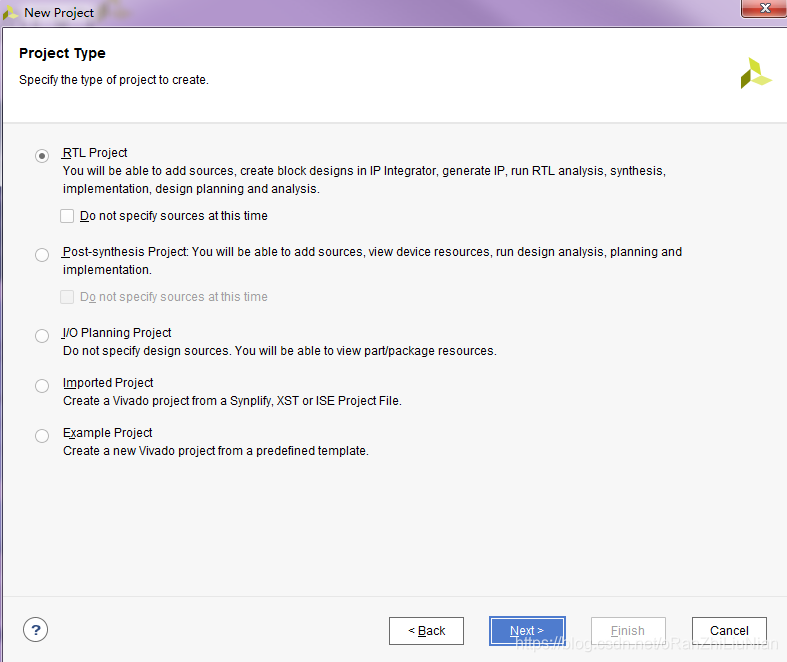

选择RTL Project,然后点击NEXT

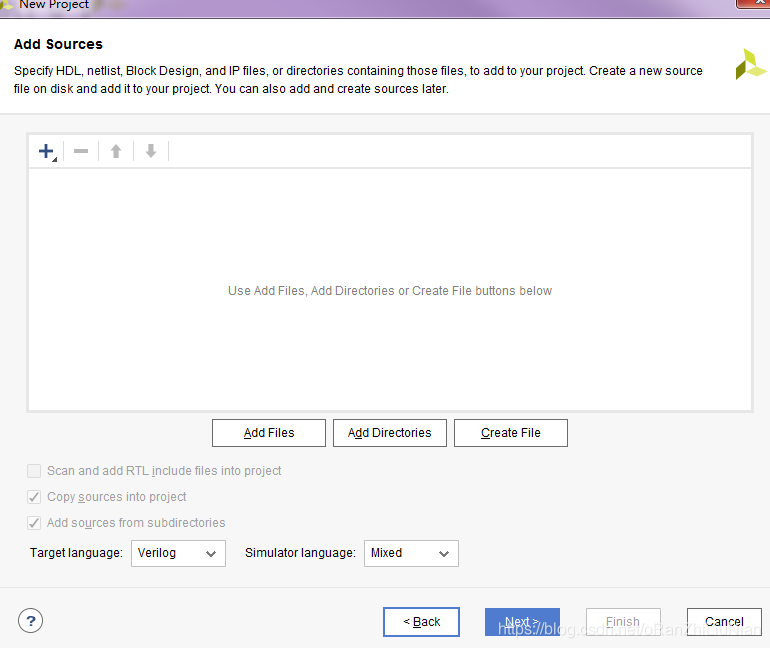

add source界面,有文件可添加(add Files),也可新建,这里直接选择NEXT,后面再新建.

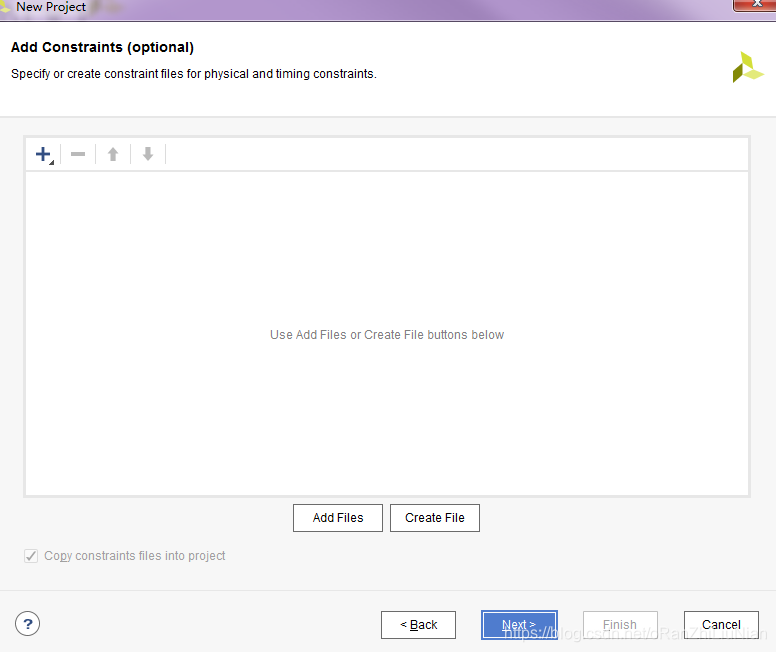

add Constraints界面,有文件可添加(add Files),也可新建,这里直接选择NEXT,后面再新建.

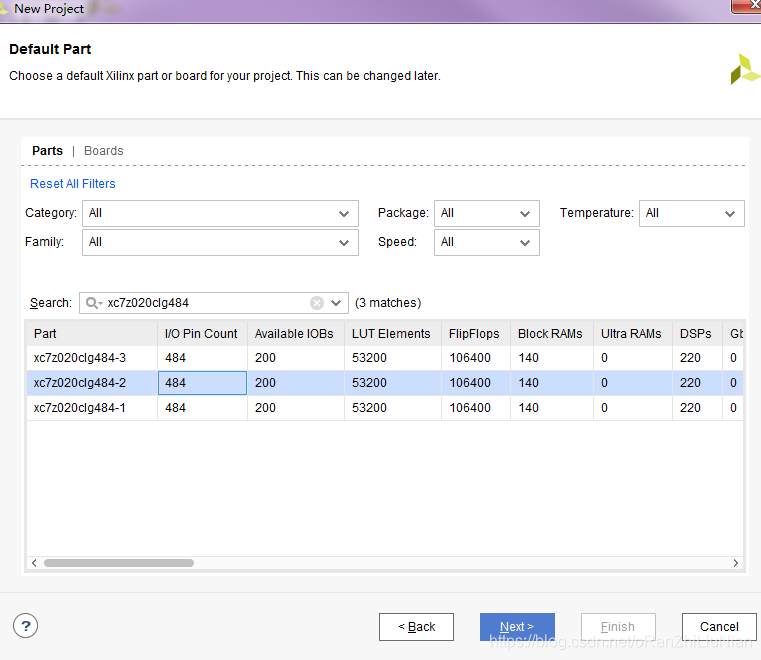

选择开发板上对应的器件,点击NEXT

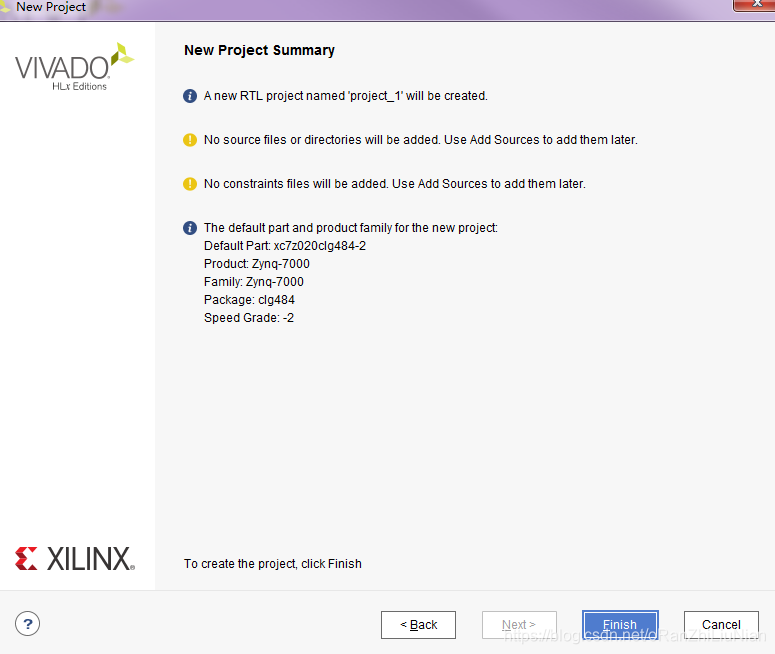

确认工程参数是否正确,然后点击Finish,进入工程界面

2、添加工程内容

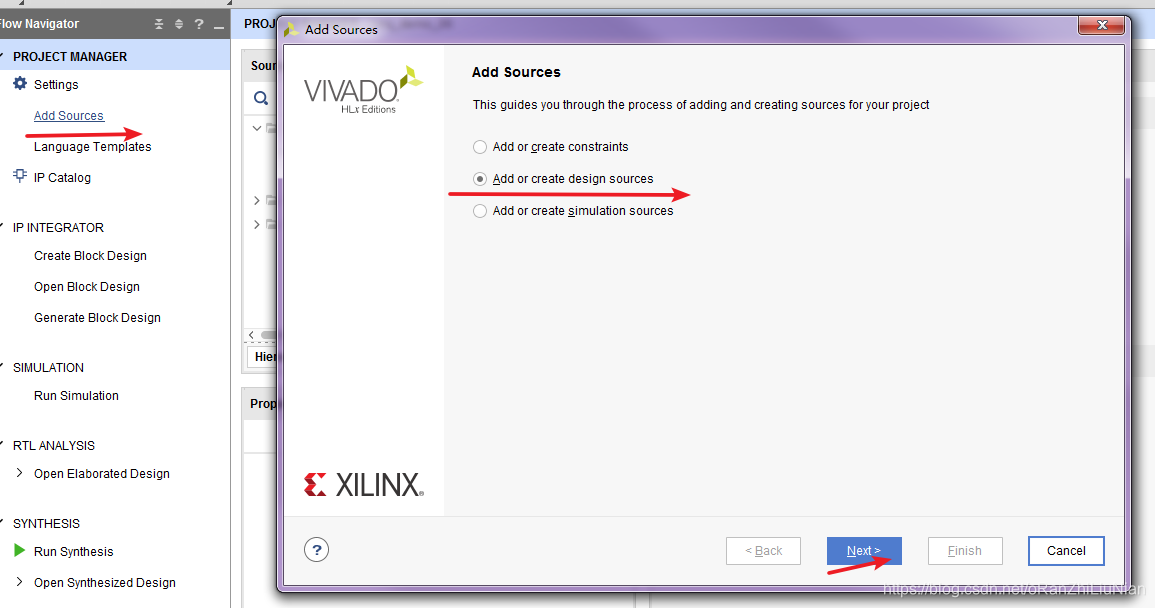

在工程界面添加Verilog文件:选择左侧Add Source,然后选中add or creat design souce,点击next

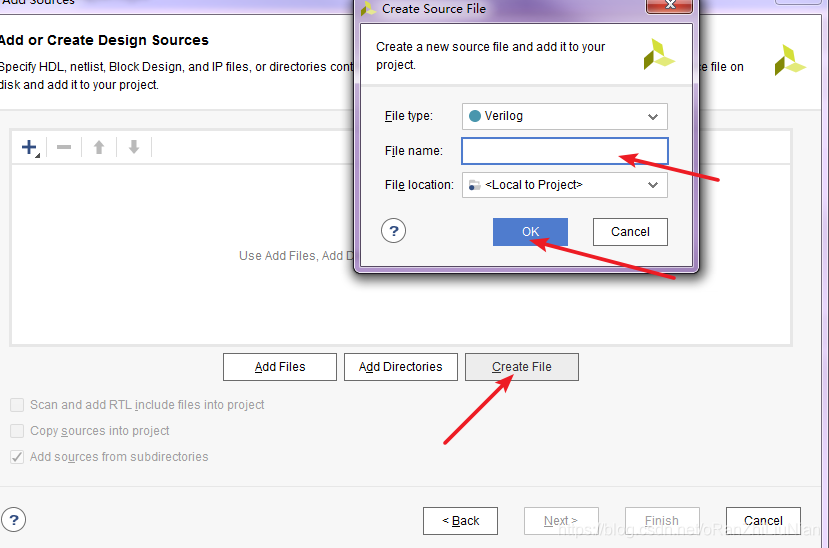

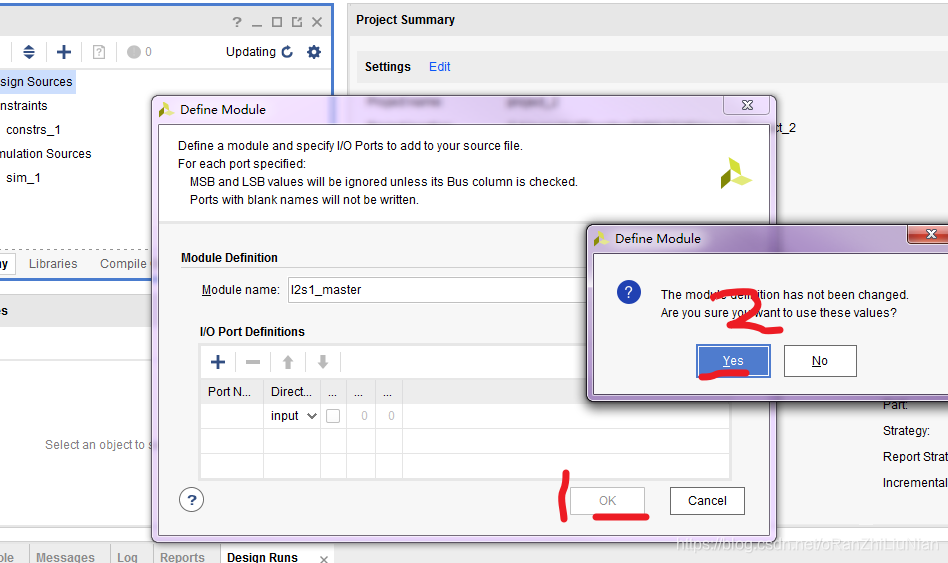

这里如果有写好的文件可以直接选择add files添加,没有的话,需要新建;点击Creat File,弹出对话框中填写文件名字,类型为Verilog(这里填写的名字为I2s1_master),然后选择OK,弹出 Define Module中可以定义 Module名字,这里直接点击OK>/ yes,

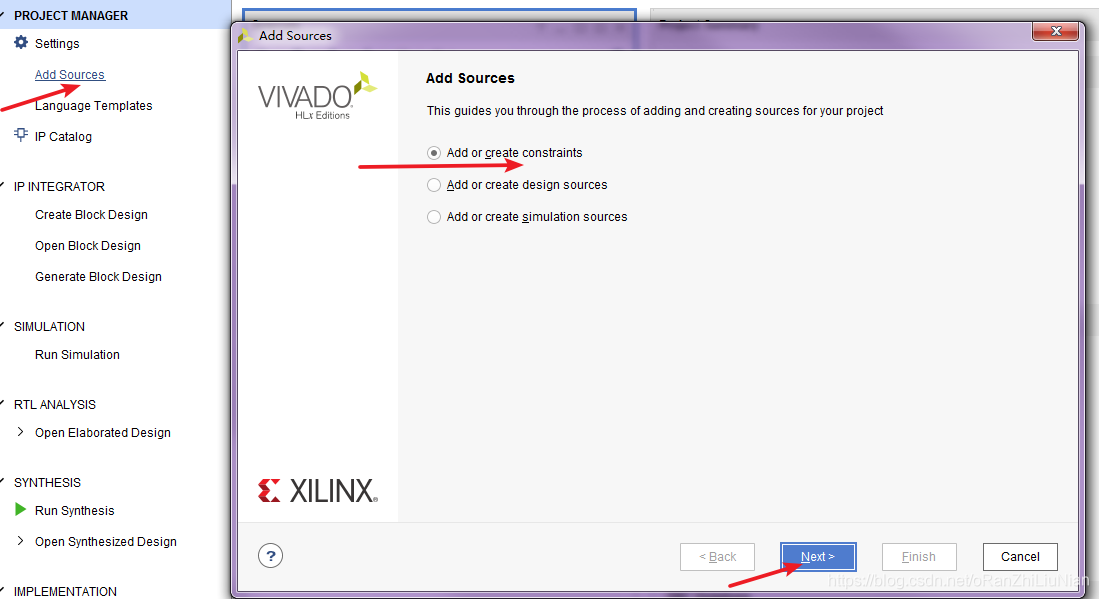

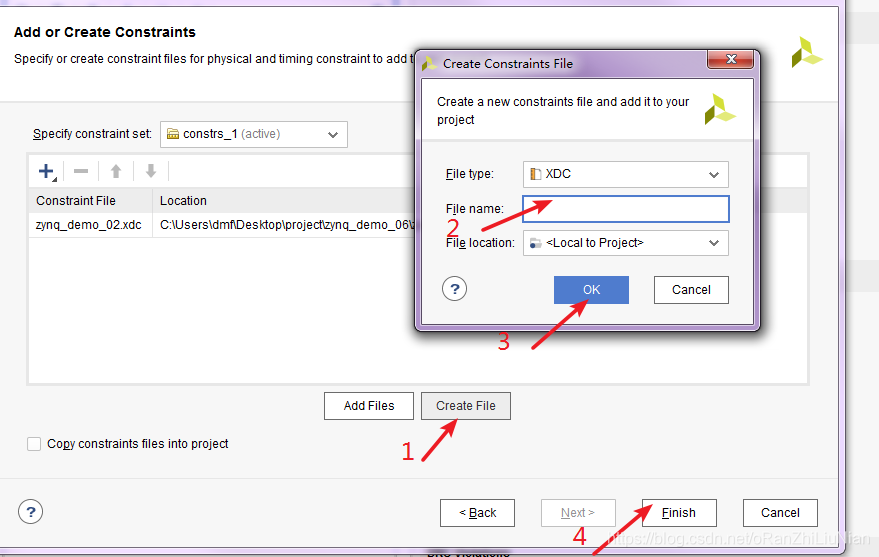

添加约束文件,这里如果有写好的文件可以直接选择add file选项添加,没有的话,需要新建;点击Creat File,弹出对话框中填写文件名字,类型为XDC(这里填写的名字为zynq_demo_02)(XDC为vivado的约束文件类型)

如下图红点标记位置所示,源文件和约束文件添加完成。

可添加相关源文件和约束文件内容

3、编译,下载

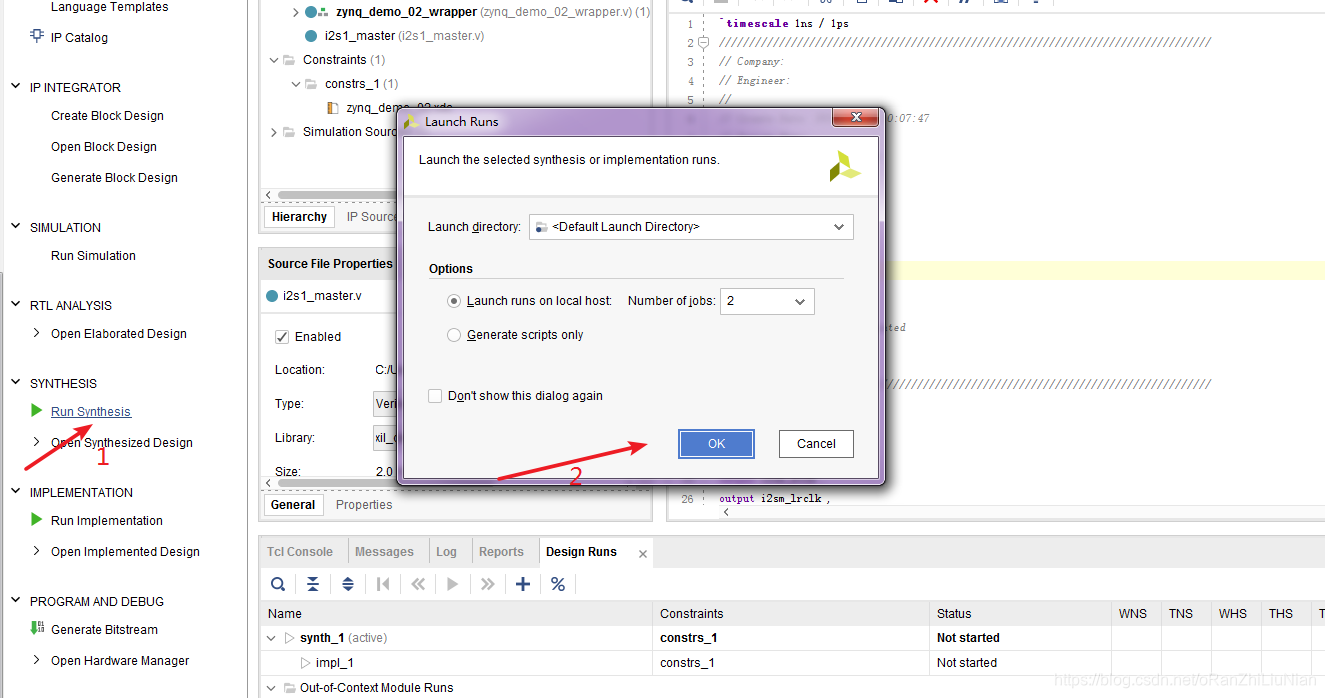

首先运行 Run Synthesis,

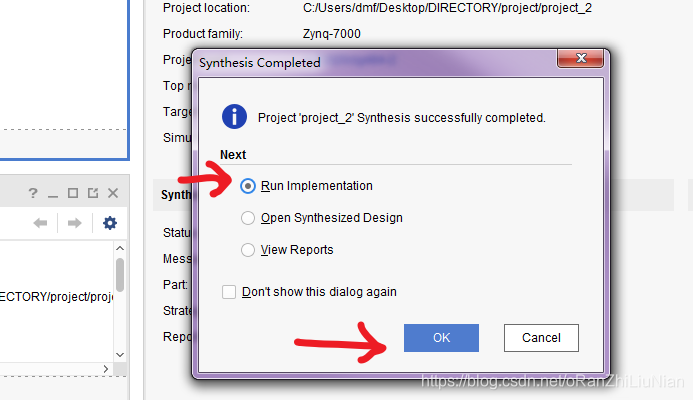

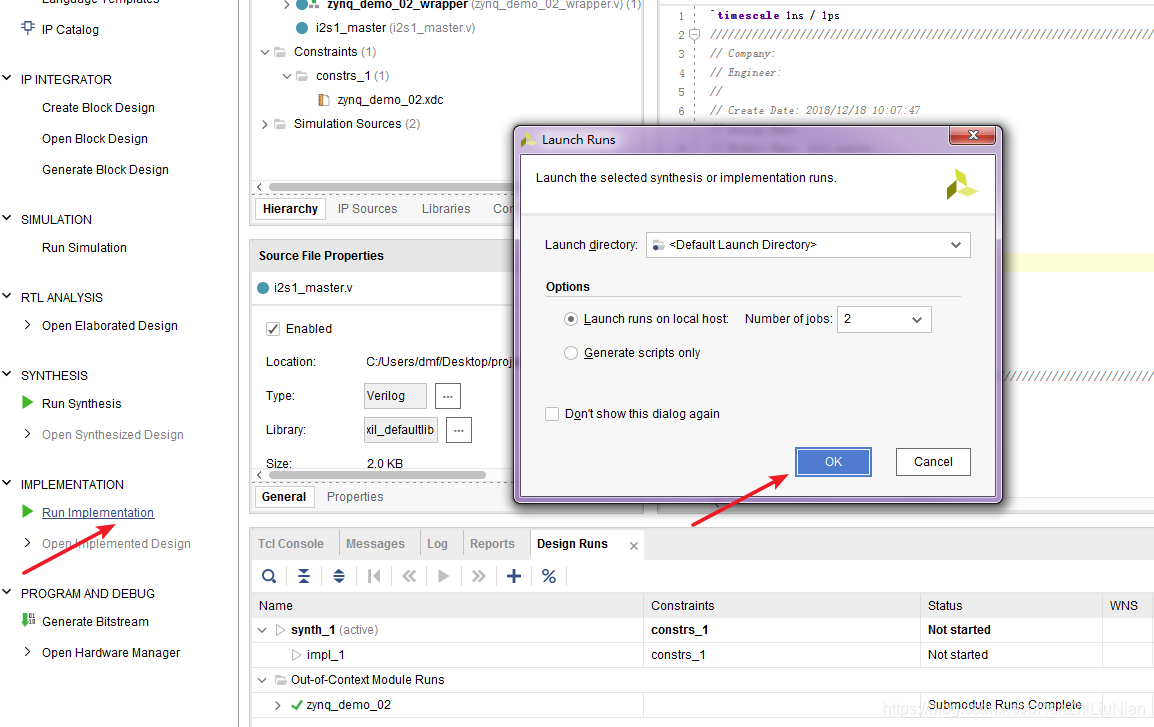

然后运行Run implementation,上一步完成界面直接选择Run implementation,然后点击OK即可

或者直接点击OK关掉后在左侧选择操作

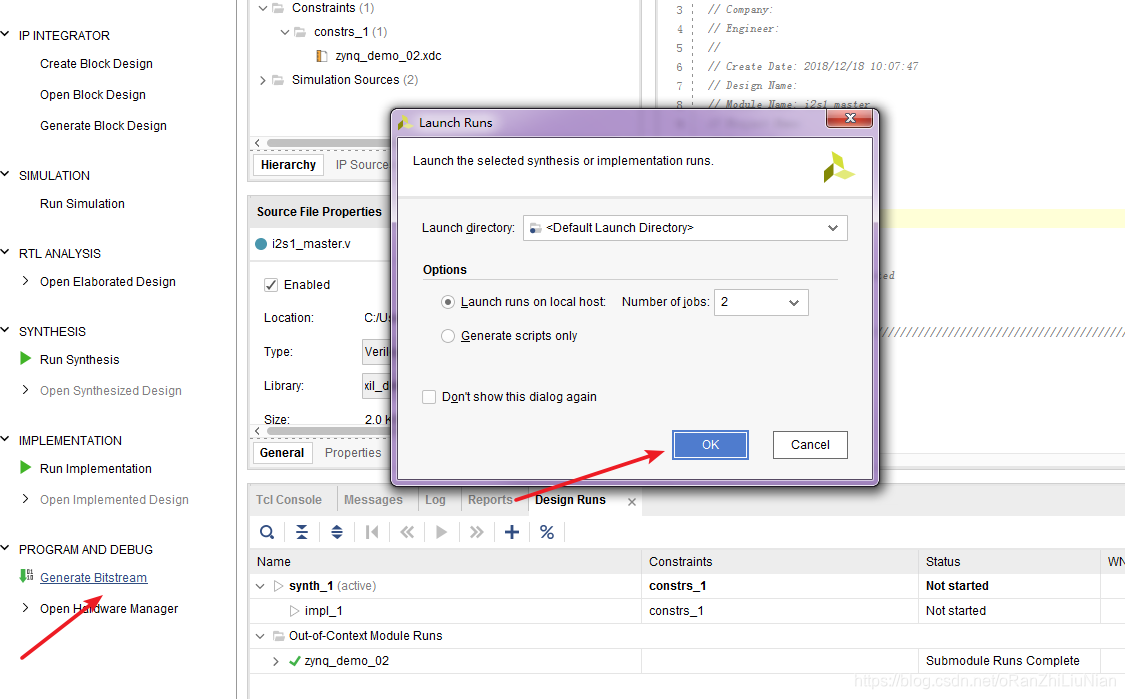

生成bitstream文件,左侧运行Generate bitstream

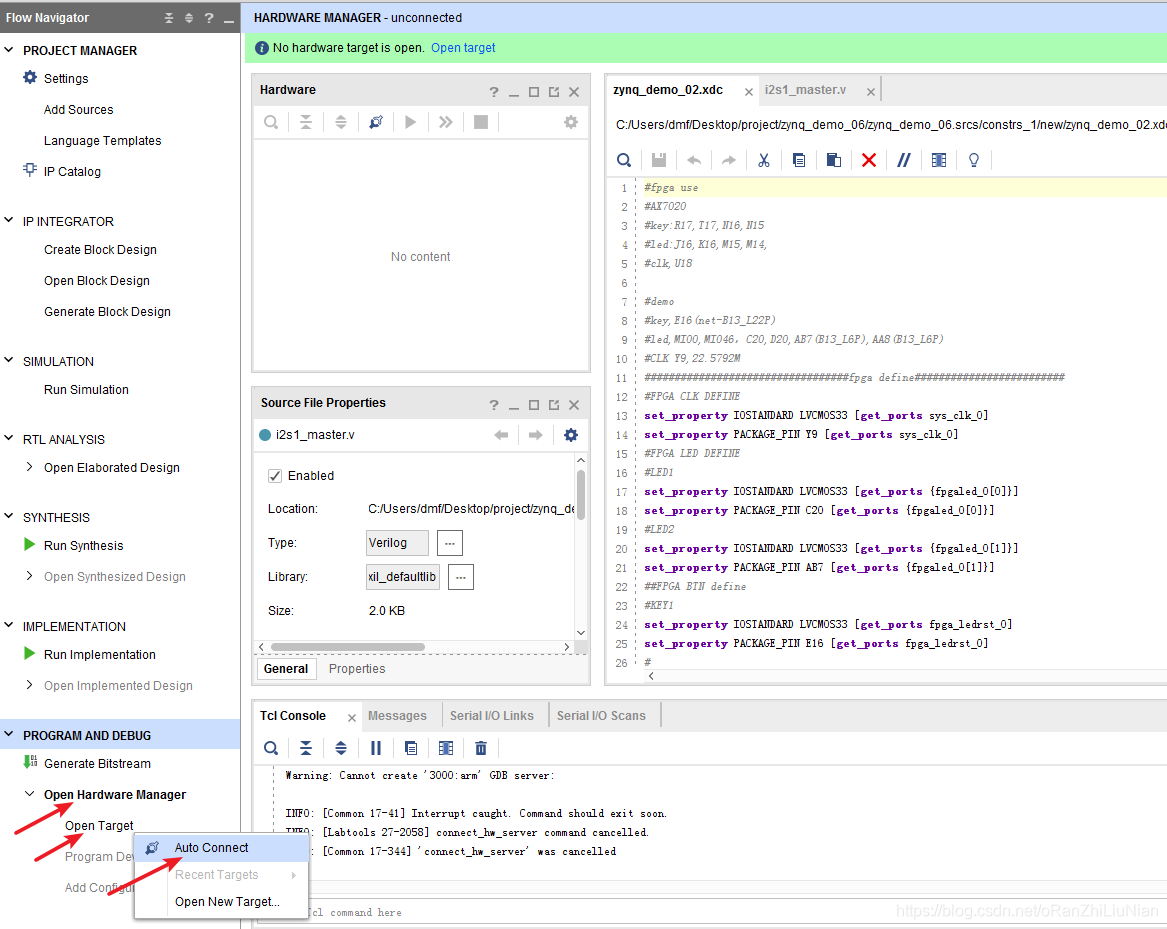

连接硬件设备

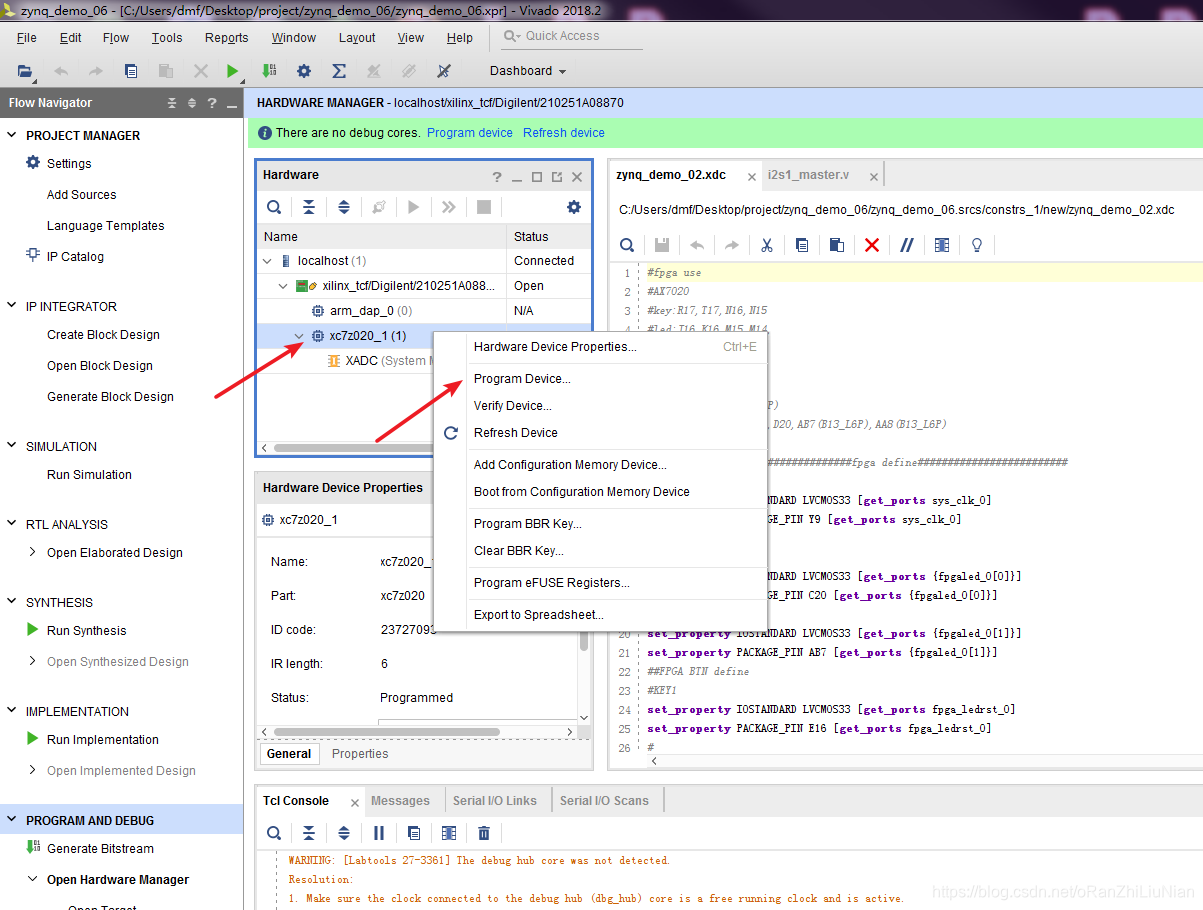

选择xc7z020_1,右键点击Program Device;即可下载仿真fpga程序

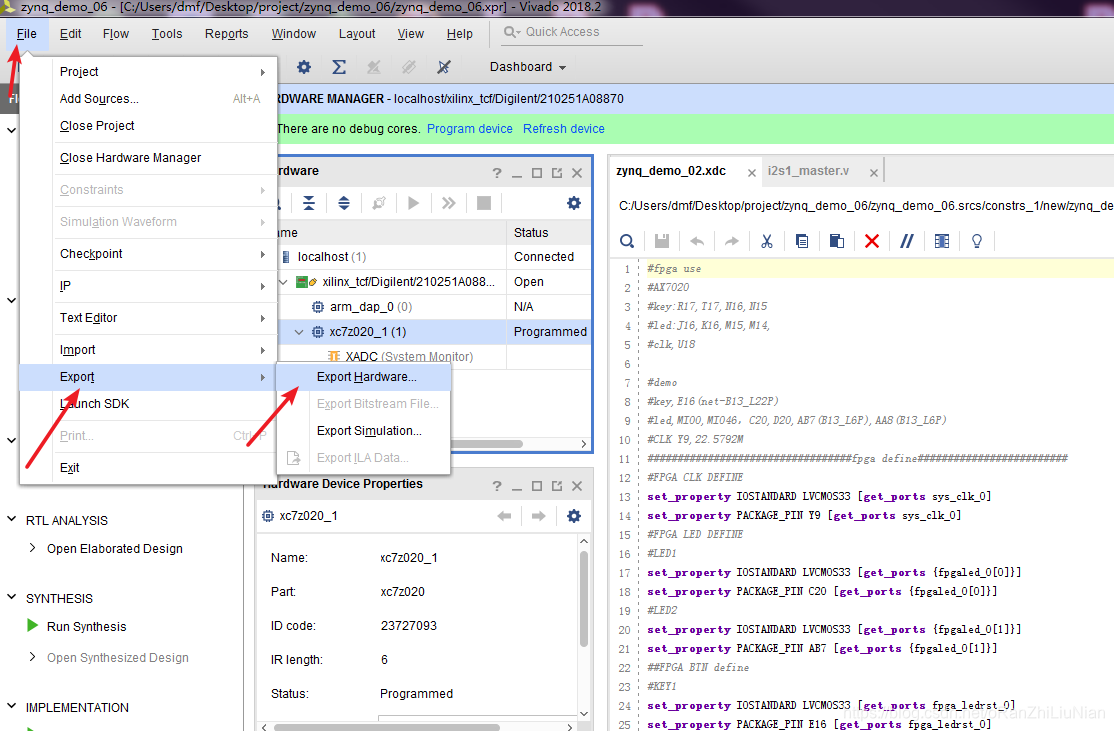

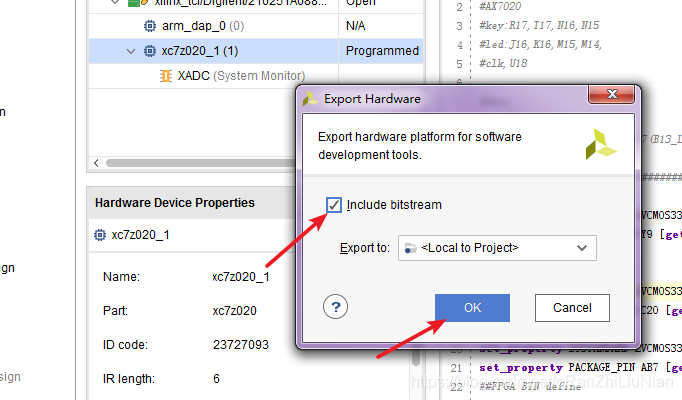

4、导出Hardware

导出文件成功。导出目录在:工程目录\XXX.runs\impl_1\zynq_demo_02_wrapper.bit

1718

1718

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?