Hello-FPGA

info@hello-fpga.cOM

目录

Hello-FPGA Camera link Full Receiver FMC Card User Manual 1

Hello-FPGA Camera link Full Receiver FMC Card User Manual 3

Hello-FPGA Camera link Full Receiver FMC Card User Manual

Camera link 简介

Camera Link是一种为工业相机接口应用而设计的串行通信协议标准。它的设计目的是为了标准化科学和工业视频产品的互联,包括摄像机、电缆和帧捕获器。

Camera Link的接口有三种配置Base、Medium、Full,主要是解决数据传输量的问题。Camera Link已经是一个成熟的接口标准,采用LVDS源同步时序传输视频数据,采用串口传输控制数据,采用4对普通LVDS IO传输其他控制信号,主要是触发信号。

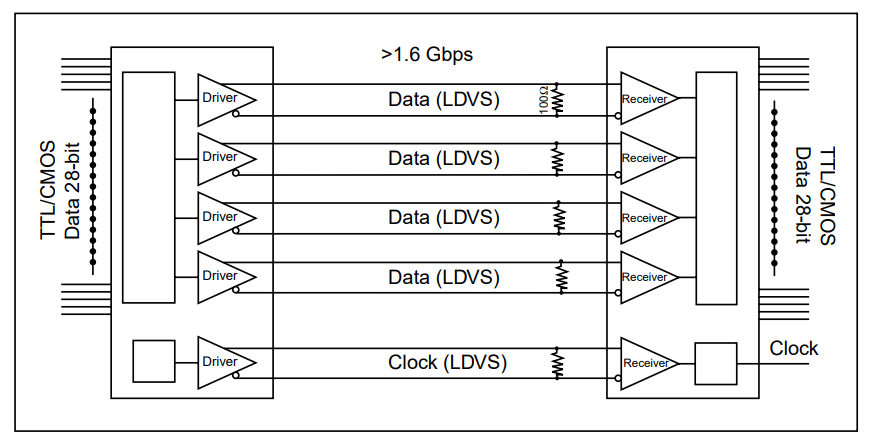

图 1‑1 channel link

Channel link 接口的实施通常使用专用串并转换芯片DS90CR288/7 完成,但是串并转换芯片需要占用较多IO,必须使用HPC FMC才能实施full格式接口,这对部分场景并不友好,而channel link 本质就是串并转换,可以使用FPGA逻辑完成,因此我们设计了1款直接使用FPGA LVDS接口的camera link full 输入接口板,同时扩展了多路FPGA IO ,用于用户拓展接口。

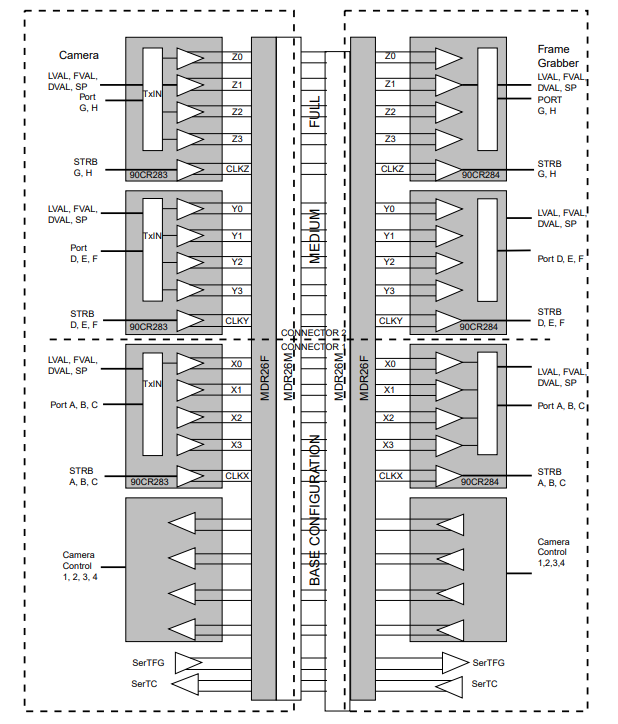

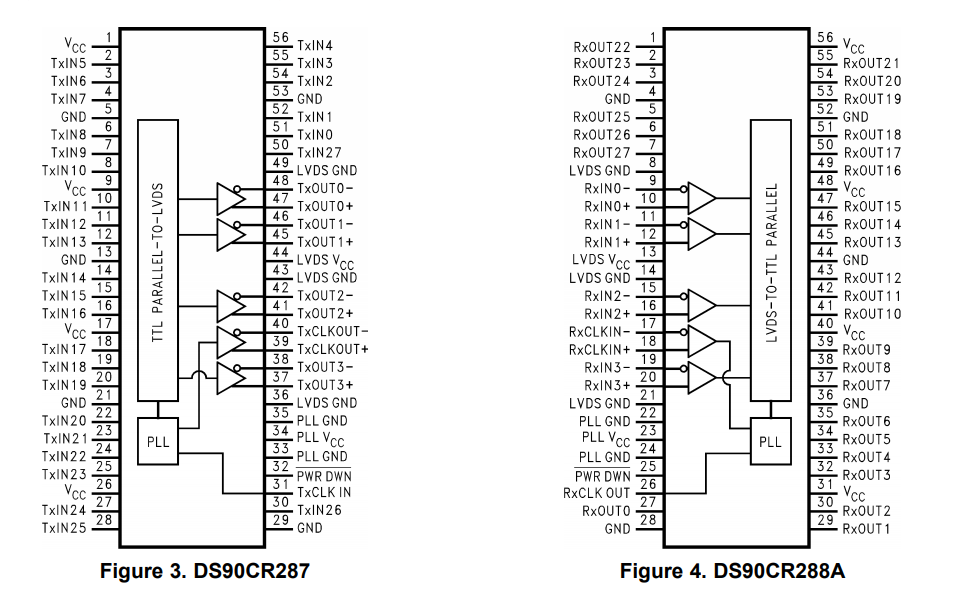

图 1‑3 专用channel link 串并转换芯片

Camera link FPGA FULL FMC

型号Hello-FPGA CL-R-FULL-FPGA-FMC

硬件特性

▪ 支持Base、Medium、Full模式, LVDS FPGA直连,不仅适用于camera link 数据传输,还适用于其他需要LVDS连接的通用场景

▪ 尺寸63mm x 84mm, 单槽LPC FMC连接器

▪ 采用MDR26标准接口、线缆

▪ 支持对外5V、12V供电,方便用户做更多的外部设备拓展

▪ 支持30(15对差分)GPIO,通过2*18双排2.54mm间距连接器提供给客户,用于进一步拓展功能

▪ Hello-FPGA 同样还提供Camera link的接线板,可将MDR26标准接口线缆的信号转换为螺钉式接线端子上,以方便客户的测试使用

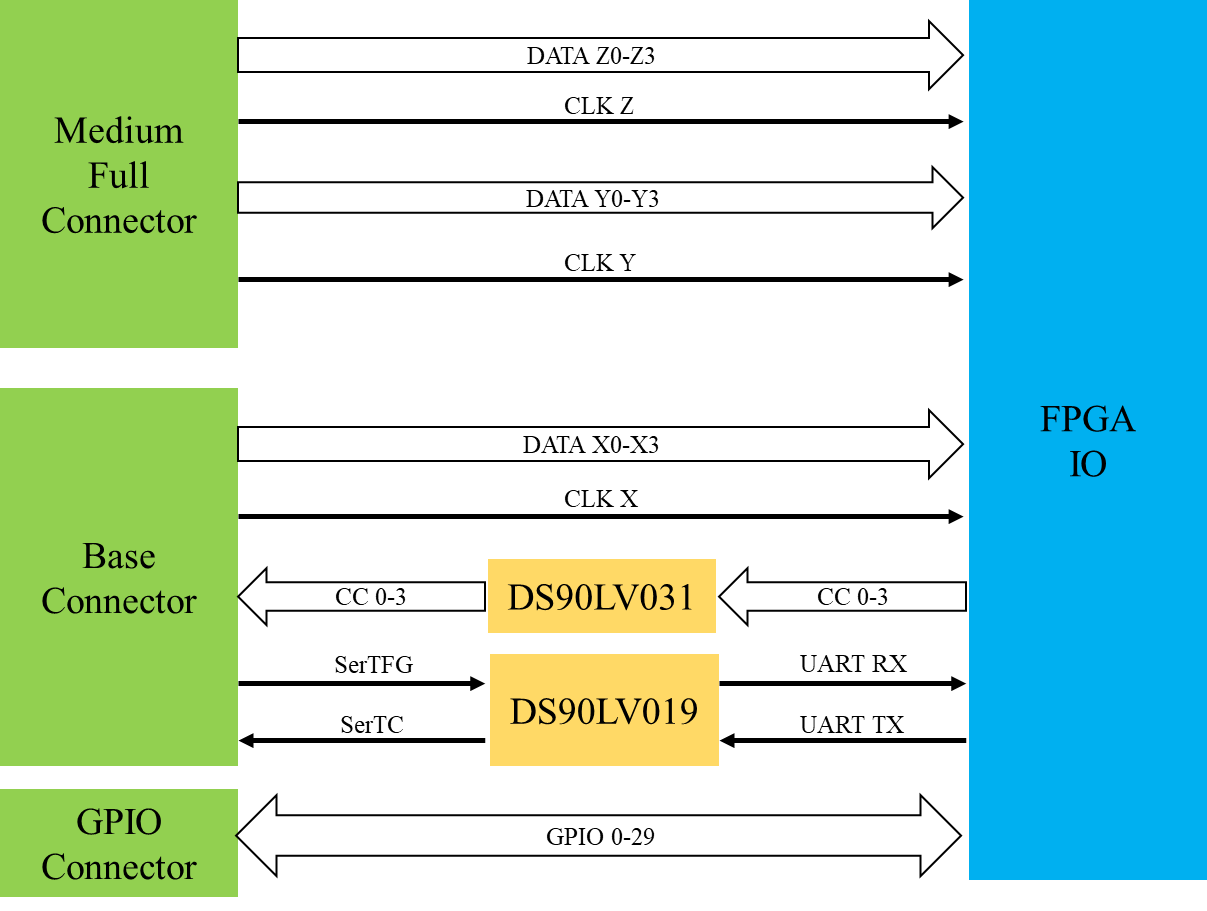

图 2‑1 Hello-FPGA Camera link模块框图

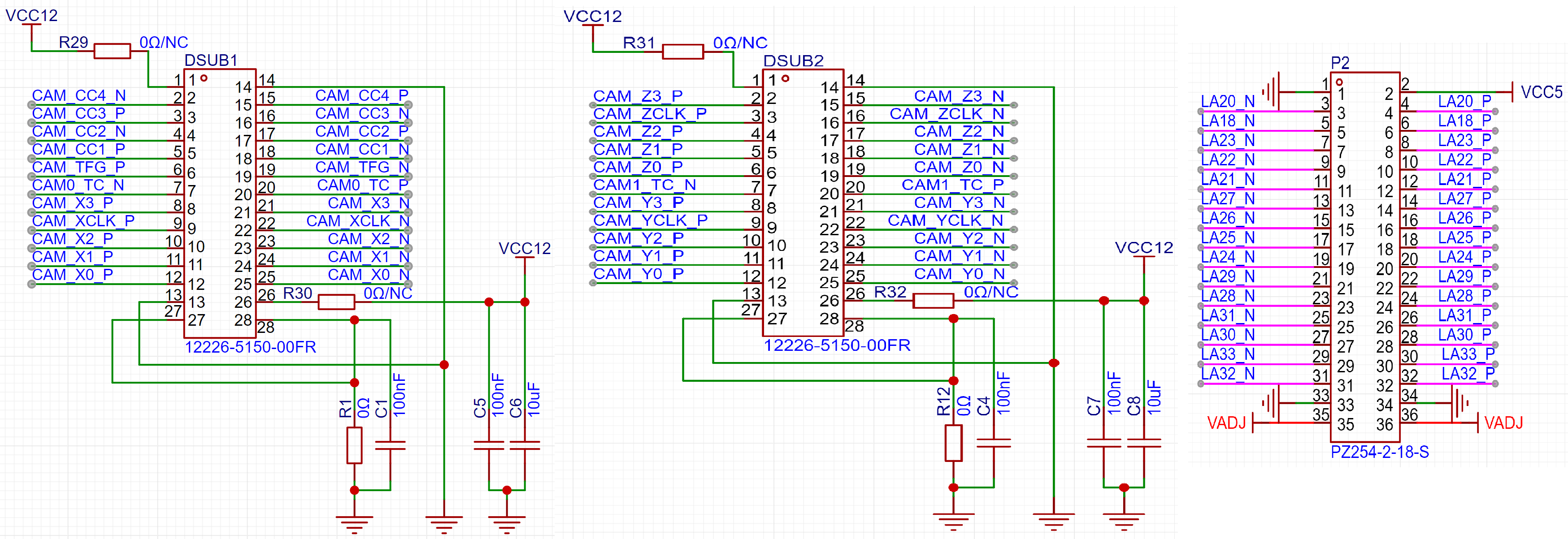

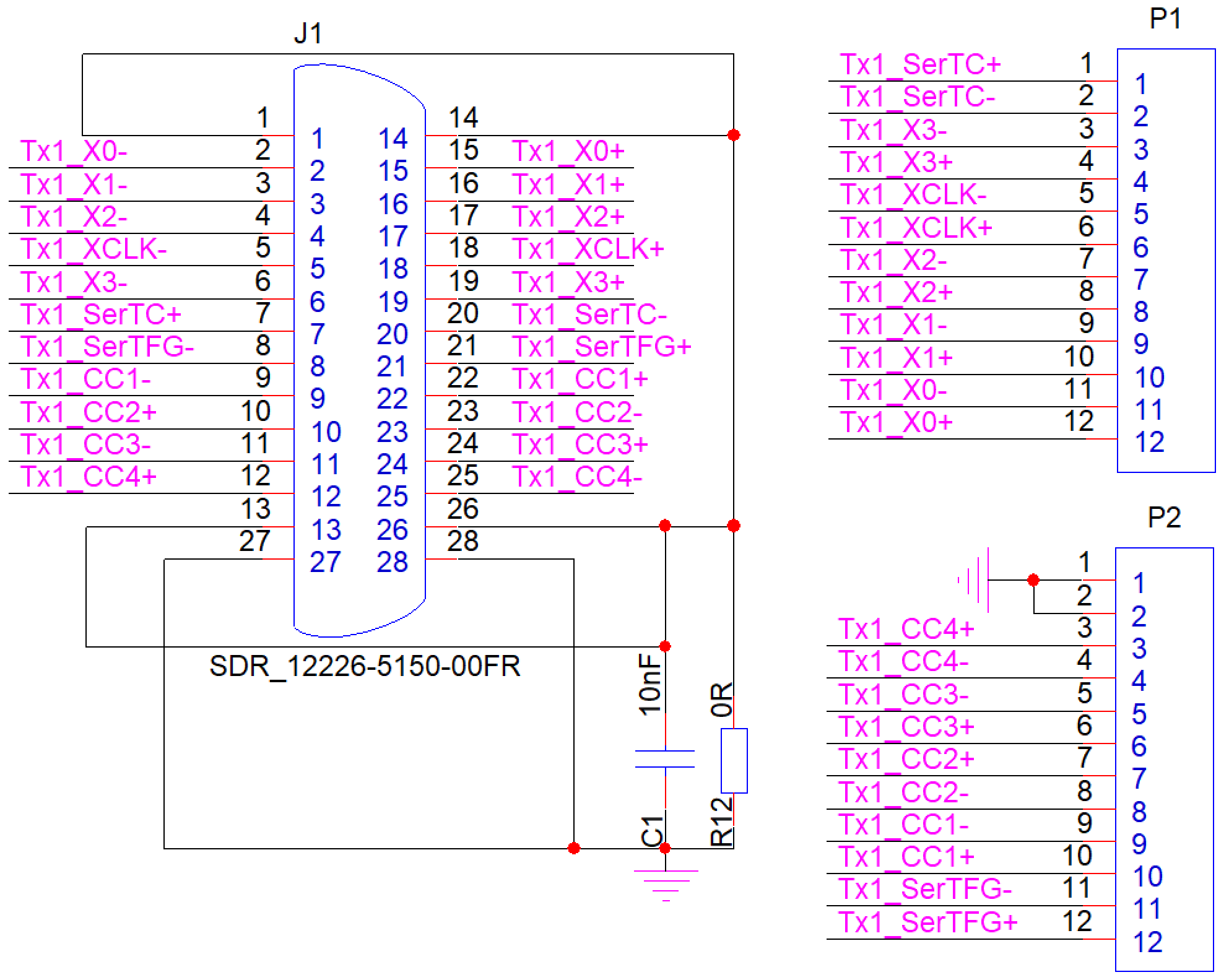

图 2‑2 Hello-FPGA Camera link模块MDR26和36pin排针连接器引脚定义

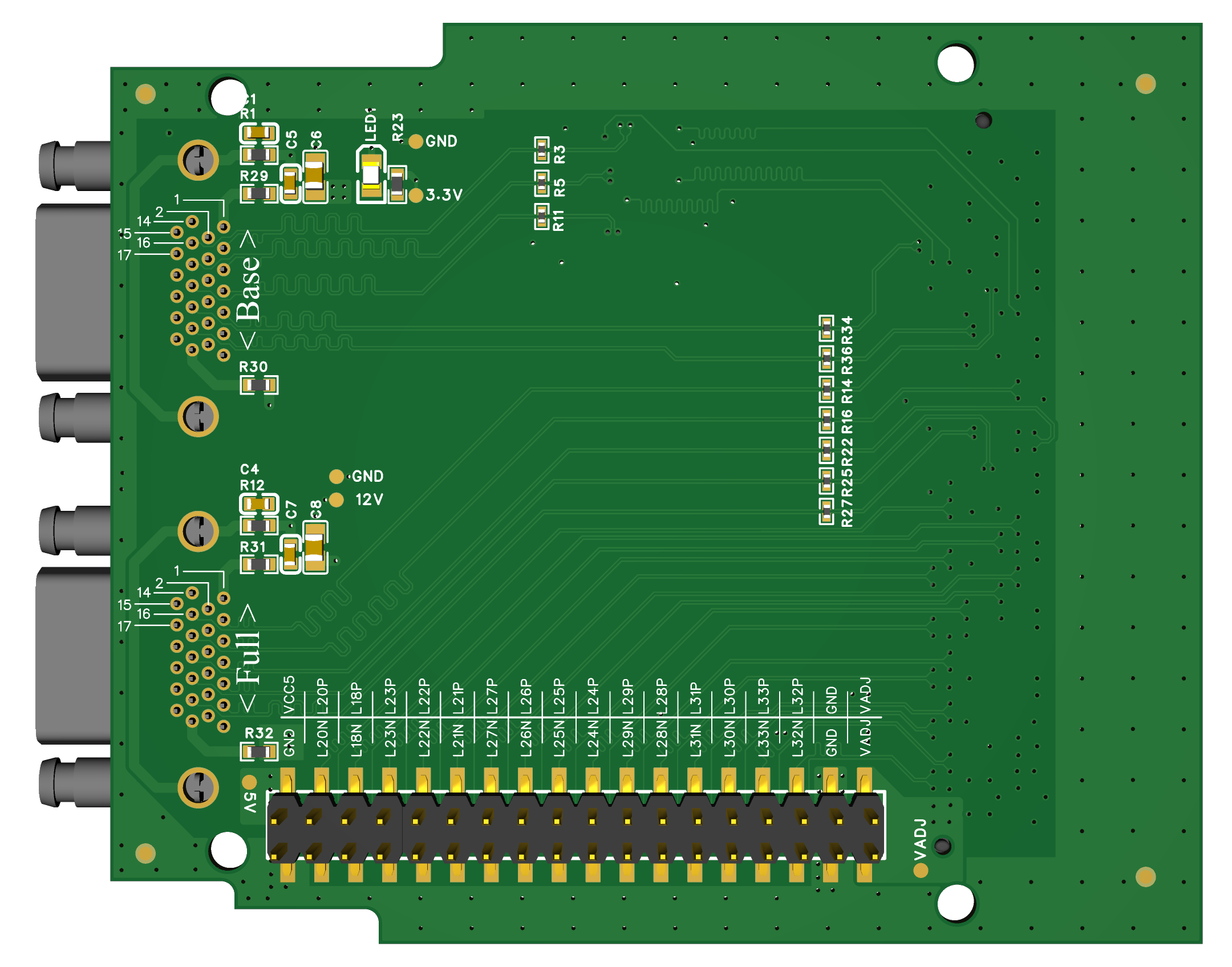

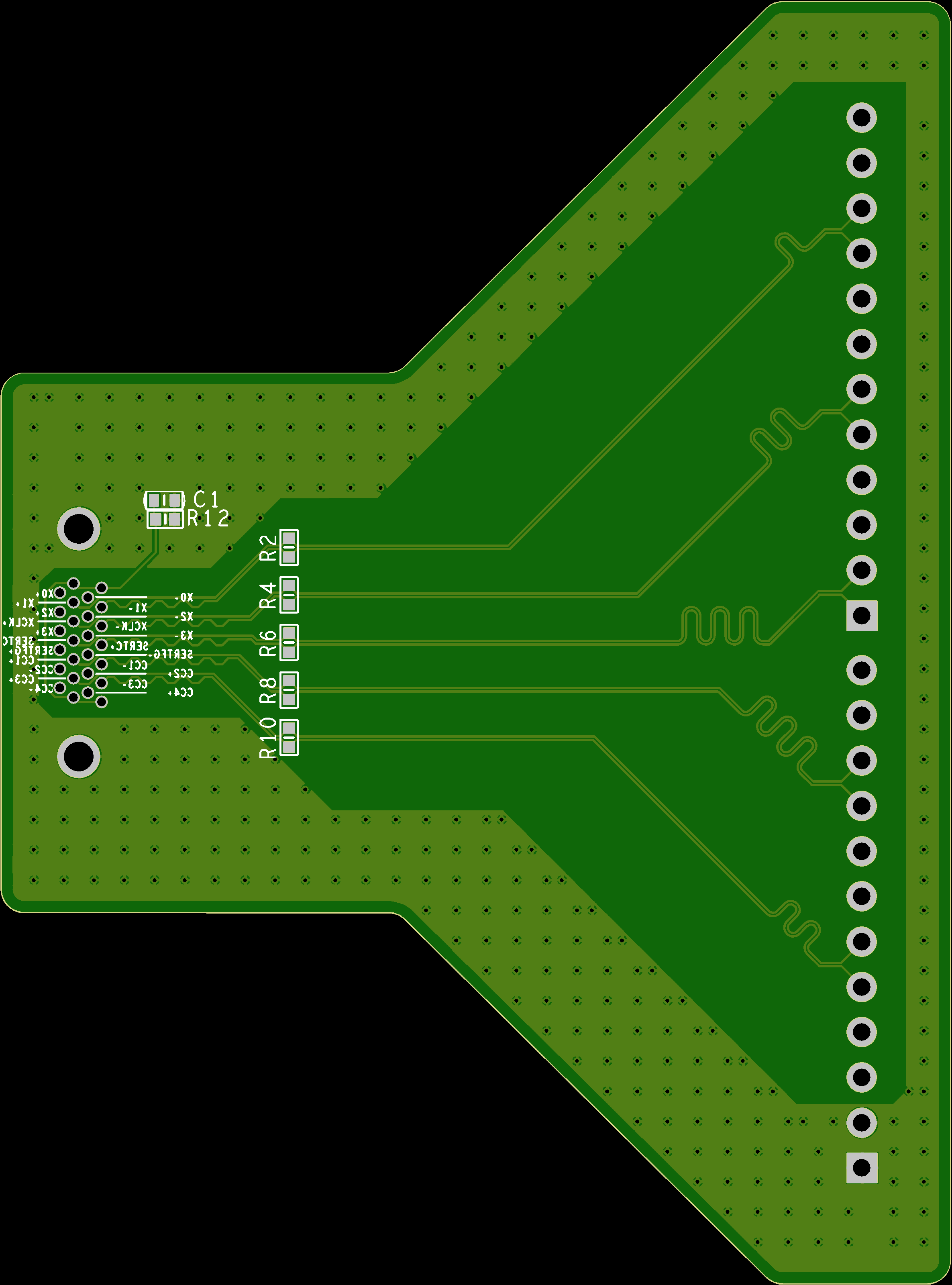

图 2‑3 Hello-FPGA Camera link板卡正面

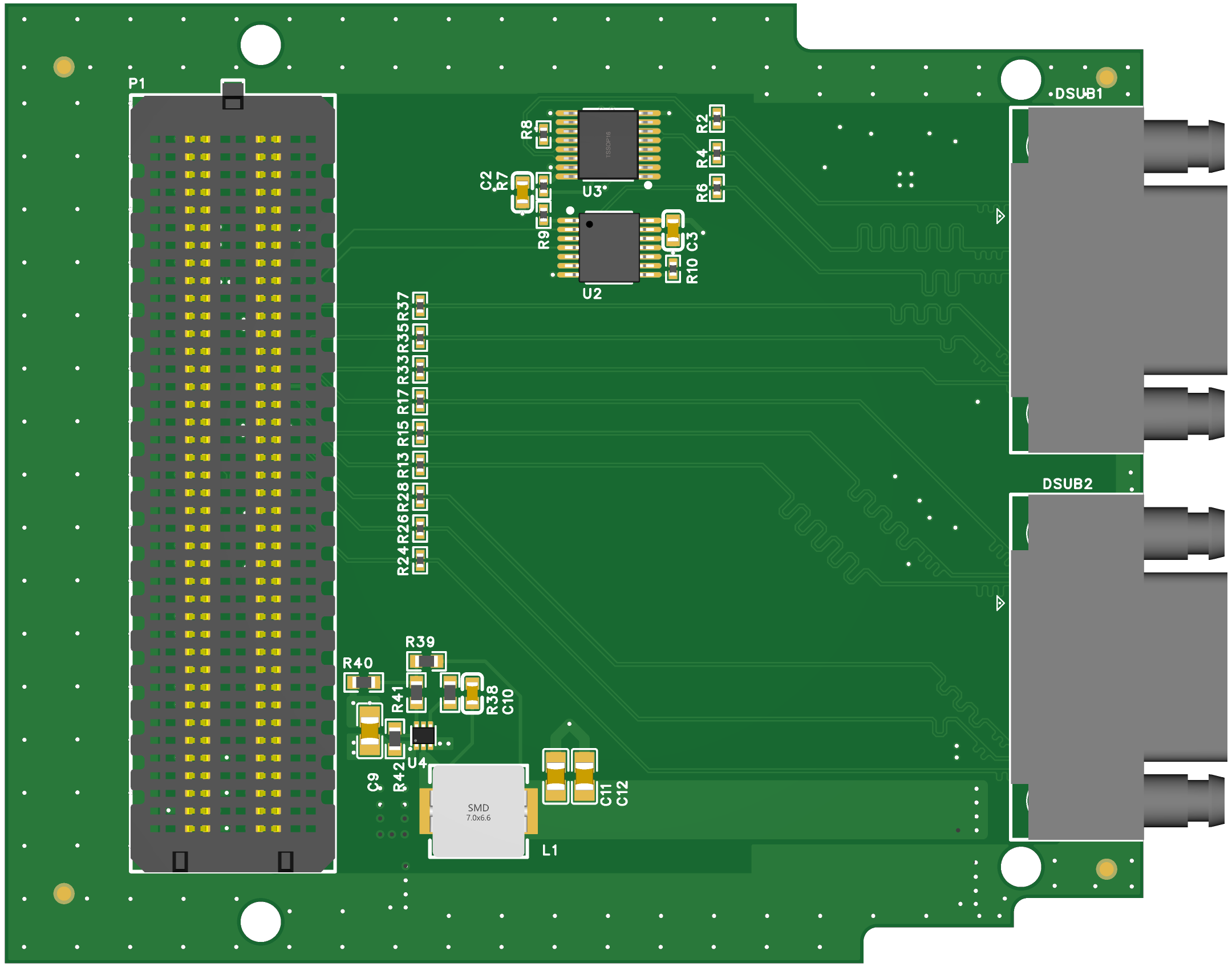

图 2‑4 Hello-FPGA Camera link板卡背面

结构说明

- LPC FMC连接器,使用FMC高密度连接器,符合VITA 57.1标准;

- X/Y/Z相关相机数据由MDR26接口通过LVDS直接接入到FPGA IO, CC1~CC4相机控制信号以及SerTC、SerTCG串行通信信号则通过DS90LV031/ DS90LV019转换成单端信号后接入到FPGA IO;

- 模块提供12V对外电源,其驱动功率与FPGA载板相关;

- 模块提供5V对外电源,其驱动功率最大为5V*2A;

- 模块提供对外电源VADJ,其驱动电压与功率与FPGA载板相关;

FMC PIN定义

LPC FMC连接器的引脚定义如下:

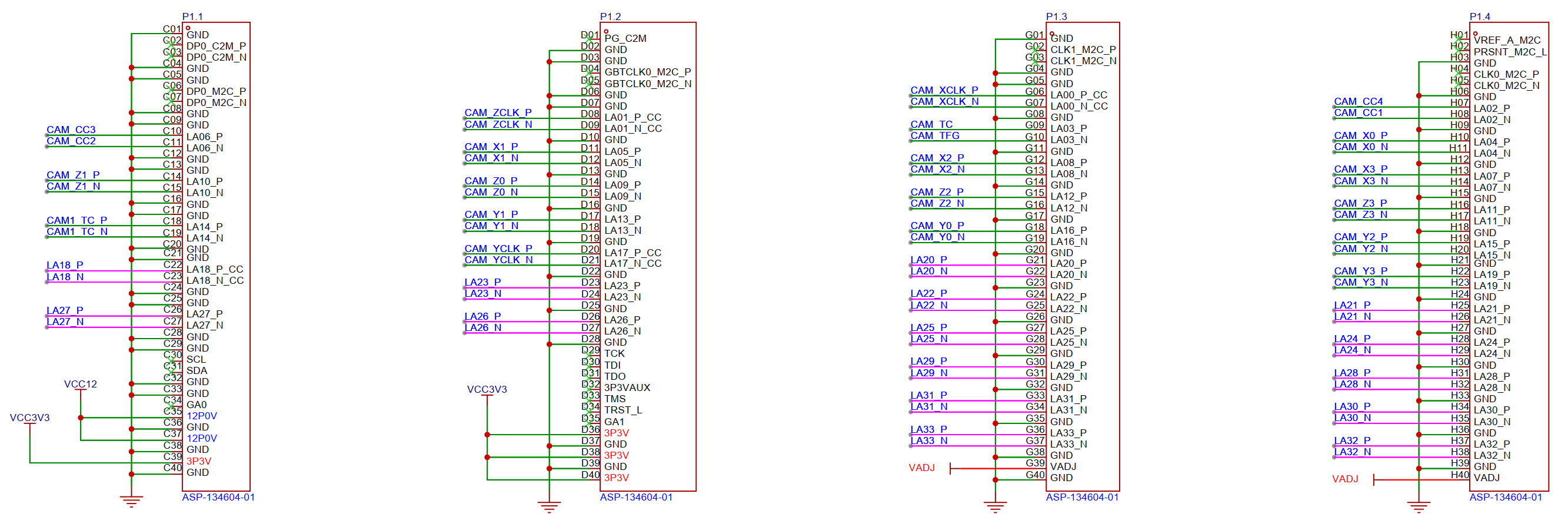

图 4‑1 FMC连接器 pin定义

这里的是FMC LPC连接器,其标准定义如下:

图 4‑2 HPC FMC pins(LPC只包含C/D/G/H)

软件支持

Hello-FPGA暂不提供软件支持,大家可以参考:

https://www.ti.com/lit/ds/symlink/ds90cr287.pdf?ts=1716163913988

https://www.zipcores.com/datasheets/camera_link.pdf

GitHub - yxsyxs/cameralink: cameralink take over and send

Camera link 调试接口板

型号Hello-FPGA CL-PROBE-MDR26

为了方便客户的测试使用,Hello-FPGA 同样还提供Camera link的接线板,可将MDR26标准接口线缆的信号转换为螺钉式接线端子上。

硬件特性

▪ 接线板上包括MDR26标准接口和3.81mm间距的螺钉式接线端子,二者间通过等长的差分线直接连接,丝印接口标注明确,用户可以方便接线,板上可选100欧姆差分匹配电阻,方便用户进行测试。

图 3‑1 Hello-FPGA Camera link 接线板接口引脚定义

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?