学习了一篇白皮书,关于400/800G 112Gb/S的信号完整性测试的重要性及挑战。

目录

LINE, LANE, SYMBOL RATES 和 DATA RATES(名词概念对比解析)

Physical media, lanes and lines

100 Gbps, 106.25 Gbps 和112 Gbps

400Gbps/800Gbps 工作在112Gb/S SerDes上

简介

对越来越大的带宽需求正在推动400Gbps、800Gbps和1.6Tbps以太网连接的发展。目前,400Gbps在数据中心的部署方面增长最为强劲,因其标准已经出台,产品也已投入商业规模使用。关于800Gbps和1.6Tbps的标准化工作还在进行,我们预计在不久的将来也会看到这些速率的产品和标准。

对于以太网来说,目前还没有定义的技术可以支持在单一的电线或光纤上传输400Gbps。因此,400Gbps的连接可以实现为40 x 10Gbps、16 x 25Gbps、8x50Gbps和4x100Gbps,最佳选择取决于每比特的成本、功耗和物理空间要求。

一般来说,较高速度的lane通道在这三个因素上都胜出,这就是为什么大多数400Gbps端口被实现为8 x 50Gbps或4 x 100Gbps。

在如此高的线路速率下,即使在相当短的距离内保持信号完整性也是一个挑战。芯片、连接器、PCB和完整的交换switch的设计者必须进行广泛的仿真,以确保整个信号路径的良好信号完整性,并使用相应的测试设备验证设计不同供应商的Switch模块之间的互操作性的等。因此,仅仅测试Layer23数据包传输是不够的,你的测试设备还必须能够在物理Layer1进行测试。第1层也被称为PHYsical层(PHY),并被细分为三个子层,即物理编码子层(PCS)、物理介质附件(PMA)子层和物理介质依赖(PMD)子层。这些子层内的各种功能被整合为 串行器/解串器(SerDes),因此,SerDes这个词经常被用来描述PHY。

在本白皮书中,我们首先描述了line, lane, symbol和data rates的基本知识,以及 400Gbps以太网传输的调制格式。然后描述了用于100Gbps以太网的典型基于ADC的SerDes实现的关键要素,接着简要介绍了信号完整性,重点是与100Gbps有关的挑战。

接下来,详细描述了为验证信号完整性而需要测试的参数,以及400Gbps的一些实际使用案例。以及一些用于400Gbps连接的实际使用案例。请注意,虽然本白皮书的重点是400Gbps,但大部分内容与800Gbps和1.6Tbps的测试也是相关的。

LINE, LANE, SYMBOL RATES 和 DATA RATES(名词概念对比解析)

人们很容易被以太网传输速率的许多术语所迷惑。在我们讨论实施的具体细节和信号完整性问题之前,让我们先来看看各种定义

Physical media, lanes and lines

最底层是物理介质/传输介质,可以是电的,也可以是光的,如图1所示

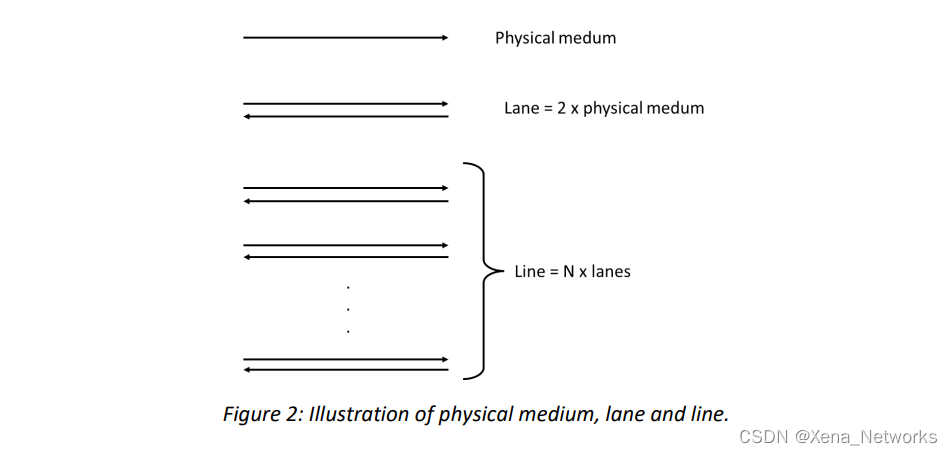

由于通信大多是双向的,一个完整的会话链路会是2个通道/通路Line。一条Line可以是一个单Lane,但在10Gbps以上,每条Line通常使用多个Lane。物理介质、通道和链路的定义的简单概述见图2。

一个lane有时会被称为SerDes,尽管SerDes实际上是收发器设备内部的一个部分。

Symbol 和DataRate

数字编码信息的传输方式是通过symbol符号。最常见的类型是 二进制符号(比特),其中的符号值可以是 "1 "或 "0",甚至是比特的组合 如 "00"、"01"、"10 "和 "11"。符号率是指每秒钟发送的符号数,以波特为单位。符号率是指每秒钟发送的符号数,以波特为单位。

数据率是每秒钟发送的数据量。在简单的情况下,每个符号周期 只包含一个比特,数据率等于符号率。包含两个比特,数据率是符号率的两倍。数据率的单位是比特/秒 (bps)。

100 Gbps, 106.25 Gbps 和112 Gbps

以太网的数据速率是100Gbps,但是,为了在单通道上传输如此高的数据速率,需要在IEEE 802.3ck标准化工作中定义的纯以太网数据中加入一些额外的信息(开销)。这种开销相当于6.25%,因此每条通道的100Gbps以太网的实际数据速率是106.25Gbps。

然而,用于100Gbps以太网的标准SerDes被定义为112Gbps,因此被称为112Gbps SerDes。原因是用于直接传输106.25Gbps以太网的标准SerDes也被用于ITU-T建议G.709中描述的光传输网络(OTN)。OTN是一个传输协议,在其有效载荷的基础上增加了额外的开销位,因此,OTN的线路速率被定义为112 Gbps速率。

400Gbps/800Gbps 工作在112Gb/S SerDes上

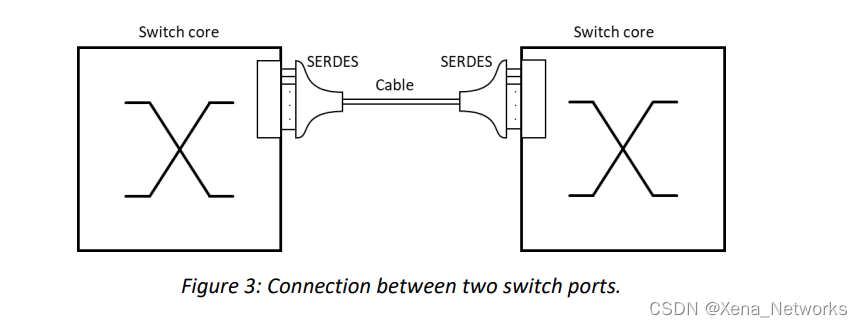

图3展示了一个需要高速以太网连接的应用实例。这个例子是一个简单的连接,从一个交换机端口,通过一个物理外部电缆到另一个 交换机端口。在交换机内部,高速连接是通过多个并行通道实现的,以便将每个通道的速度降低到可控范围内。以便将每个通道的速度降低到电子装置可管理的速度。在 然而,在传输电缆上,最好是尽可能少地传输通道,以减少电缆和连接器的复杂性。以减少电缆和连接器的复杂性。图3中的串行器/解串器(SerDes)的功能是,正如其名称所言,它是用来传输数据的。图3中的串行器/解串器(SerDes)的功能,正如其名,是在发射器处将许多低速通道合并成较少的高速通道,并将高速通道分割成若干个通道。发送器上的许多低速通道合并成较少的高速通道,并在接收器上将高速通道分成多个平行的低速通道。在讨论高速以太网连接时,我们将重点讨论SerDes的功能。

电缆上的通道数Lanes number on Cables

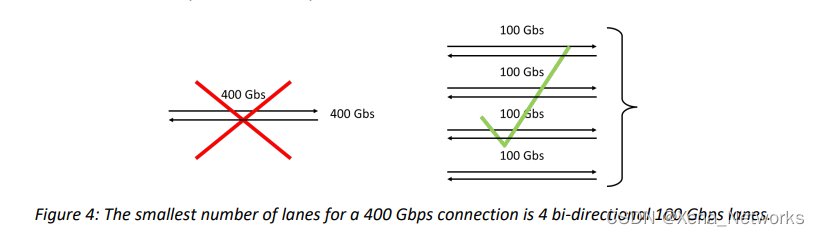

尽管很理想,但目前没有任何以太网技术可以作为单通道传输400Gbps,400Gbps目前都是使用较低速度的多个平行通道来实现的。目前,最高可行的单通道速率是112 Gbps,尽管关于224Gbps的工作一直正在研究进行中,这意味着我们需要4条通道来实现400Gbps的以太网。

正如介绍中提到的,也可以将400Gbps实现为8条50Gbps的通道。

图4表明,所有的通道都是双向的。

调制格式

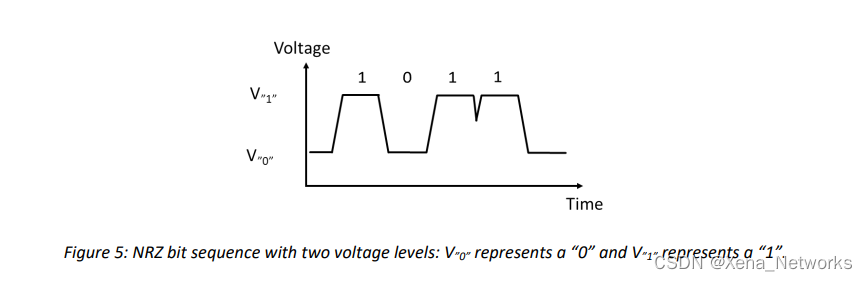

以太网常用的调制格式是不归零(NRZ),每个符号周期都携带一个比特的信息,即 "1 "或 "0",如图5所示。今天,以太网定义的最快的单通道NRZ符号率是25.78125 GBaud,因此,对于每个100Gbps的连接,我们需要4个25.7825 GBaud的平行通道(400Gbps为16个),达到一个 802.3bj中定义的103.125Gbps的数据速率。

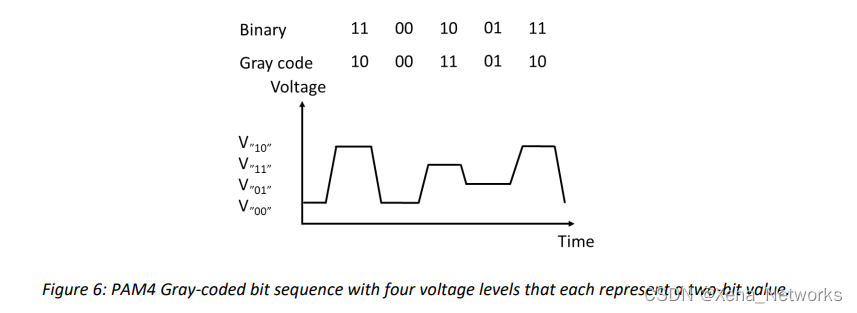

然而,最近在802.3ck中定义了一种新的调制格式,使用4级脉冲振幅调制(PAM4),符号率为53.125GBaud,导致单通道的数据速率为106.25Gbps。PAM4编码方案如图6所示,使用四个电压等级,每个等级代表一个二位数。通过这种方式,与NRZ调制相比,每秒传输的比特数增加了一倍。

从图6中可以看出,最高的电压水平代表的是 "10 "的数值,而不是人们直觉所想的 "11"。这种形式的编码被称为Gray灰度编码,用于减少比特错误。灰色编码确保两个相邻的电压水平之间的移动只导致符号中的两个比特的变化。这意味着,这种电压水平的移动永远不会导致超过一个比特的错误。

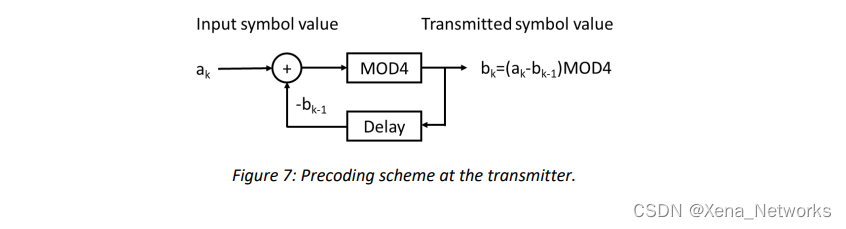

为了减少出现连续错误的可能性,还实施了一个预编码方案,在发射器对PAM4符号进行编码,在接收器对其进行解码。解码方案根据当前的符号周期和过去的符号周期的符号,使用类似于图7所示的算法,计算出一个要传输的新值。在接收端,一个类似的方案被用来再次删除预编码。

Block code分块编码和前向纠错(FEC)

当100Gbps的信号被传输时,它们会被扭曲,最终导致接收器的比特错误。在100Gbps的通道速率和10-12的误码率(BER)下,每10秒就会发生一个误码。由于这个原因,在IEEE802.3ck标准工作中,100Gbps的误码率要求被提高到10-14。

为了获得这些低水平的误码率,需要进行块编码和前向纠错。从本质上讲,这两种编码方案的工作原理是在信号中增加额外的比特,提供额外的信息,接收器可以用来纠正错误。

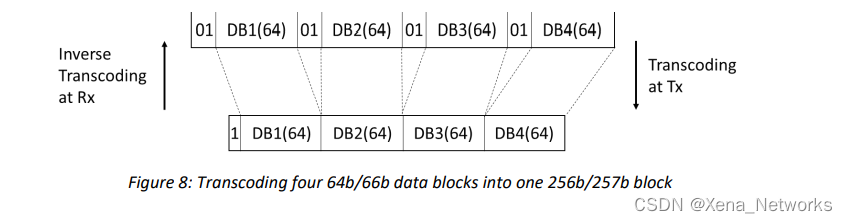

对于802.3ck中描述的100Gbps以太网,在添加里德-所罗门前向纠错(RS-FEC)之前,64b/66b编码被转码为256b/257b块。这样做是为了减少块编码所使用的开销,以便为更强大的PAM4 FEC留下更多的开销。256b/256b转码将四个64b/66b块组合在一起,去掉两个比特的头,在整个256比特块上添加一个单比特头。

前向纠错是一种编码技术,通过在发射器处增加冗余位和纠错码来检测和纠正比特流中的错误。在接收端,FEC解码器使用这些额外的位来检测错误的位并纠正它们。

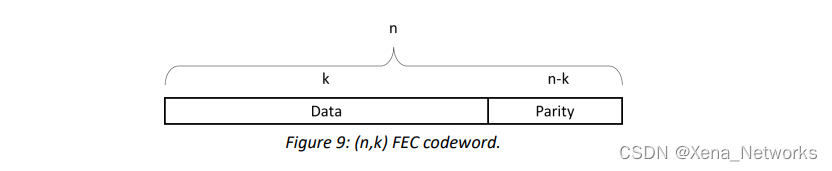

一个FEC块由n个FEC符号组成,其中k个FEC符号是实际数据,其余(n-k)个FEC符号是代码和冗余位--也被称为奇偶校验位。因此,一个FEC的特点是有序的一对(n,k)。

一个给定的FEC可以纠正的错误数量取决于实际的实现。对于802.3ck 100Gbps以太网,使用了Reed-Solomon(RS)(544,514,t=15)FEC,FEC符号为10比特宽。这意味着,每块514个数据FEC符号要增加30个奇偶校验FEC符号。t=15指的是这个FEC可以纠正多达15个FEC符号的错误,每个符号包含多达10位的错误。

802.3ck 100 Gbps以太网的总开销是6.125%,意味着实际通道速率是106.125 Gbps。

信号完整性基础知识

当一个信号从一个交换机端口传输到另一个端口时,如图3所示,信号会因几个因素而衰减。由于电线的固有电阻,信号电平会降低,当信号从发射器移动到接收器时,信号会逐渐丢失。带宽的限制会导致符号间干扰(ISI),电气通道之间的电感耦合以及连接器会导致交叉通话。阻抗不匹配导致反射(回波损耗)。在发射器和接收器都会发生抖动,最后信号会因热噪声而降低。

NRZ眼图

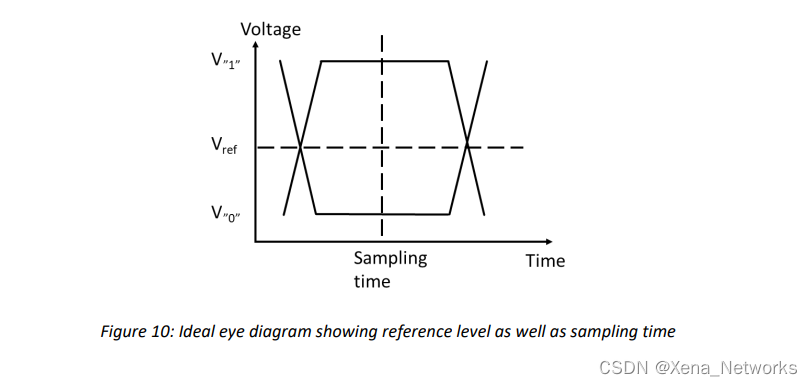

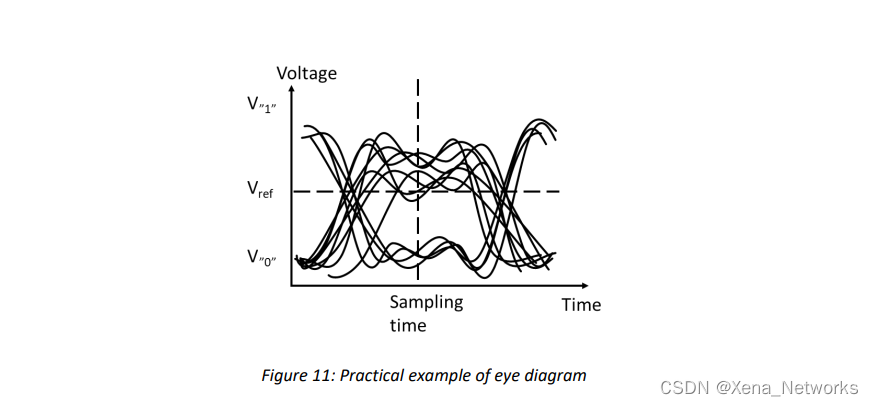

信号完整性是对传输信号质量的一种衡量。它通常使用所谓的眼图进行分析,眼图是通过重叠比特序列中的脉冲来构建的,如图10所示为NRZ调制信号。信号在脉冲中心被采样,如果电压水平高于Vref,则被解释为 "1",如果低于Vref则为 "0"。

在传输过程中没有失真的情况下,眼睛是漂亮而睁开的,如图10所示。然而,在一个真实的系统中,眼睛看起来更像图11所示,其中一些 "1 "会被误认为 "0",从而导致比特错误。

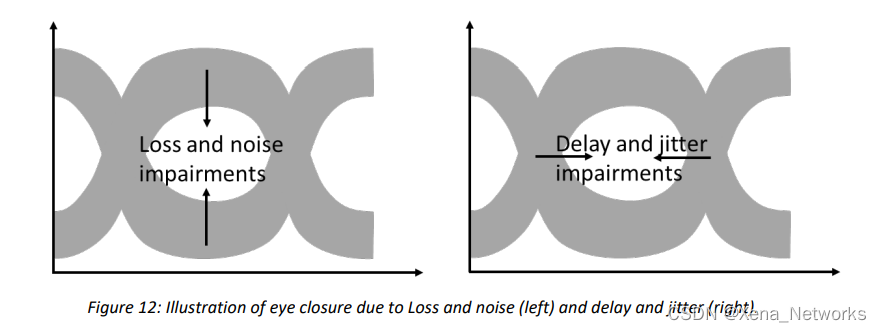

一般来说,信号电平的损伤,如损耗和噪声,会导致眼睛在垂直方向上 "关闭",而延迟和抖动的损伤会导致眼睛在水平方向上 "关闭"(见图12)。

使用PAM4的112Gbps调制的信号完整性

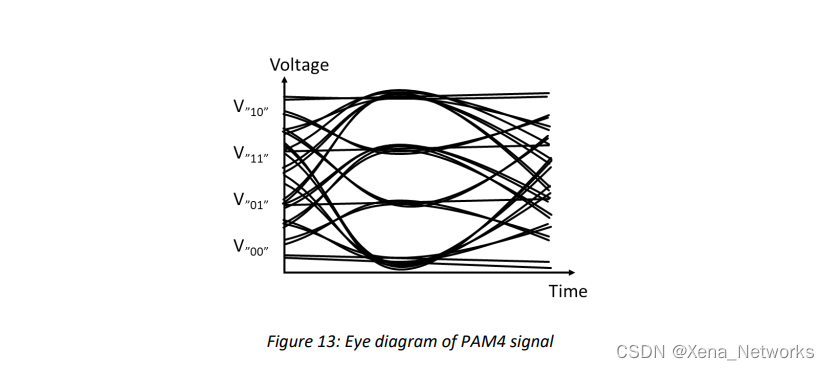

在上一节中,讨论了NRZ调制的信号完整性的基本知识。然而,对于112Gbps的PAM4调制信号,情况就有点复杂了。由于PAM4有四个级别,眼图由三个眼而不是一个眼组成,如图13所示。显然,PAM4的眼图比NRZ的眼图窄得多,这意味着PAM4比NRZ对失真容忍度低。

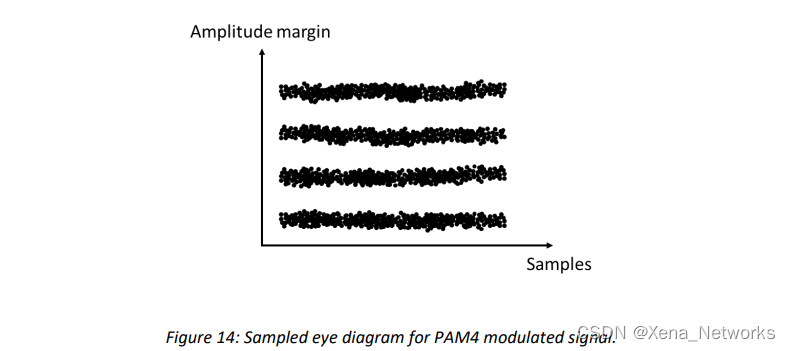

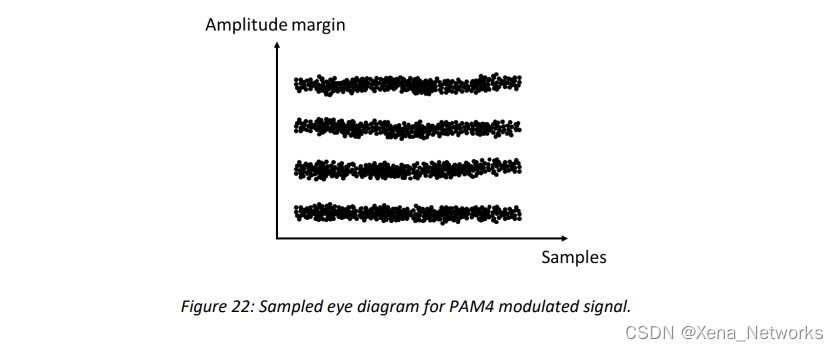

对于非常高的速度,如112Gbps,前FEC眼图可能几乎是封闭的,难以用于分析信号完整性。取而代之的是使用垂直切片机眼图。如图14所示,垂直切片眼图是通过绘制大量采样、恢复的信号电平来构建的。

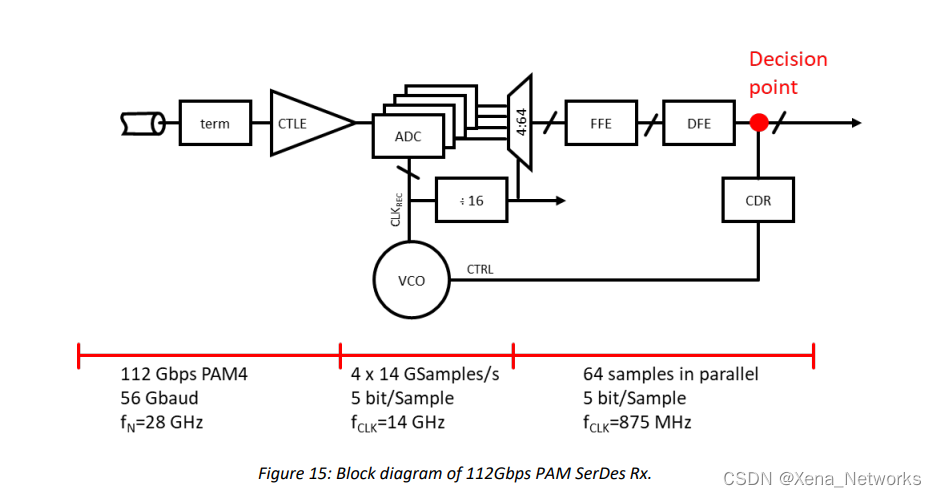

为了了解高速信号是如何恢复的,我们将使用图15的框图来描述接收器的PCS/PMA子层内的各种功能。基本上,单一的模拟112Gbps通道被反序列化为64个平行的数字875Mbps通道。然而,高速SerDes还包括各种类型的均衡,以及在数据和时钟恢复之前的模拟到数字转换。

连续时间线性均衡器(CTLE)

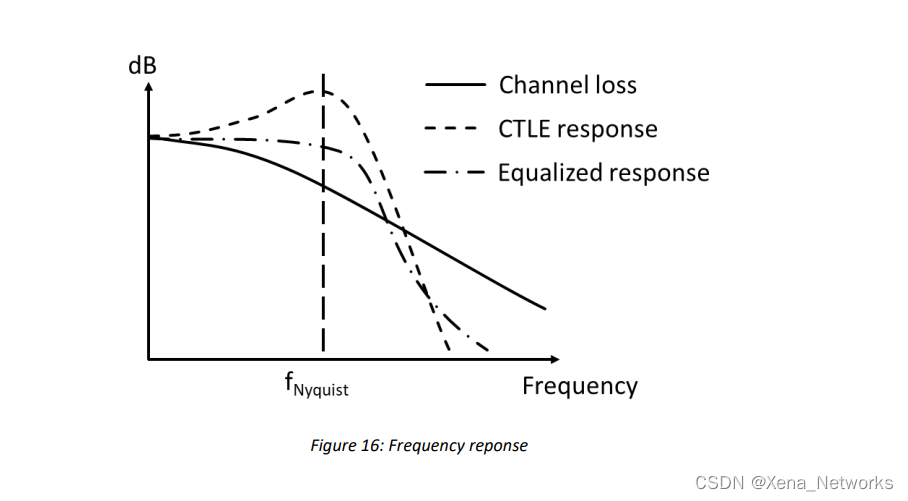

在高数据率下,接收到的数据流会严重失真,需要在采样前进行重建(均衡)。一般来说,较高的频率会比较低的频率衰减得更多,均衡器的功能是扭转这种频率响应。只有低于奈奎斯特采样频率(56GBaud的28GHz)的频率才需要均衡。

发射和接收电路中使用的一种常见均衡器方法是连续时间线性均衡器(CTLE)。如图16所示,CTLE衰减低频信号成分,放大奈奎斯特频率附近的成分。其结果是,对于低于奈奎斯特频率的频率响应变得几乎平坦。

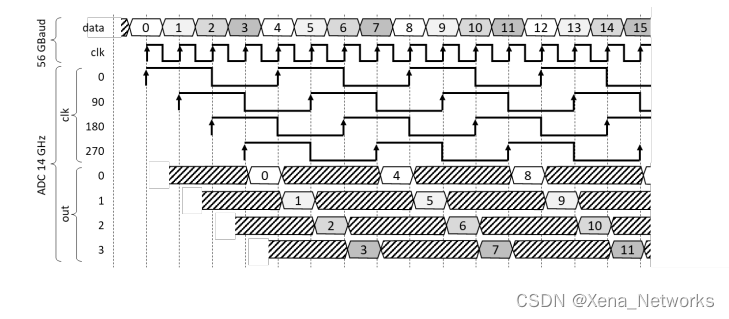

时间交错的ADC

均衡的PAM4信号的模拟电压电平使用模拟数字转换器(ADC)进行数字化,该转换器在脉冲持续时间的中间对脉冲进行采样。为了降低ADC的速度要求,通常会使用时间交错的ADC。在图15所示的情况下,四个ADC以56GBaud速率的四分之一采样,即每秒14GSamples。采样时间由一个压控振荡器(VCO)控制,该振荡器使用来自时钟和数据恢复电路(CDR)的时钟速率。

ADC的采样时间分别以0、1、2和3个全速时钟周期(56Gbaud为0.18纳秒)进行相移。实际上,这意味着ADC1对位0、4、8、...进行采样,ADC2对位1、5、9、...进行采样,ADC3对位2、6、10、...进行采样,ADC4对位3、7、11、...进行采样,见图17的时序图。

四个ADC的数字输出被解复用为64个平行的875 Mbps通道

FFE和DFE均衡

除了CTLE是在模拟信号的全线速率下进行的,另一个层次的均衡是在降低速率的64并行数字信号上进行的。这些均衡器通常是前馈均衡器(FFE)和决策反馈均衡器(DFE)。这些均衡器在均衡过程中考虑到较长的比特序列,因此可以减少符号间干扰(ISI)。

时钟和数据恢复(CDR)

时钟和数据恢复(CDR)从信号中提取时钟频率和实际数据(比特序列)。

如何测试112Gbps的信号完整性?

测试高速以太网连接和端口的性能,首先是测试信号完整性。如前所述,信号完整性不能在模拟高速水平上直接测量,而必须从恢复的数据中提取。由于这个原因,完成这项任务的正确工具是带有112Gbps PAM4端口模块和基于ADC的SerDes的以太网流量生成和分析(TGA)测试仪。

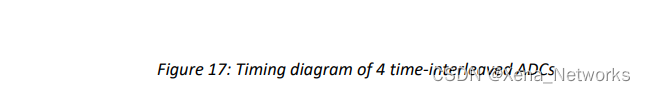

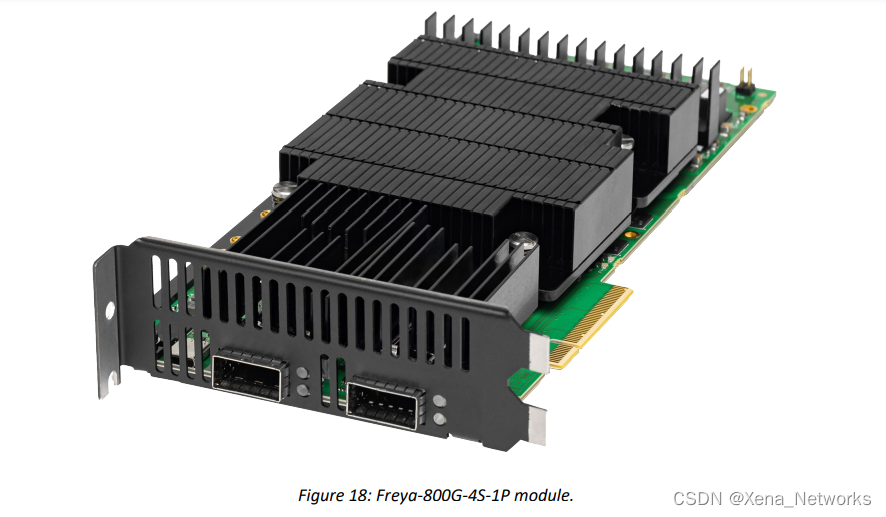

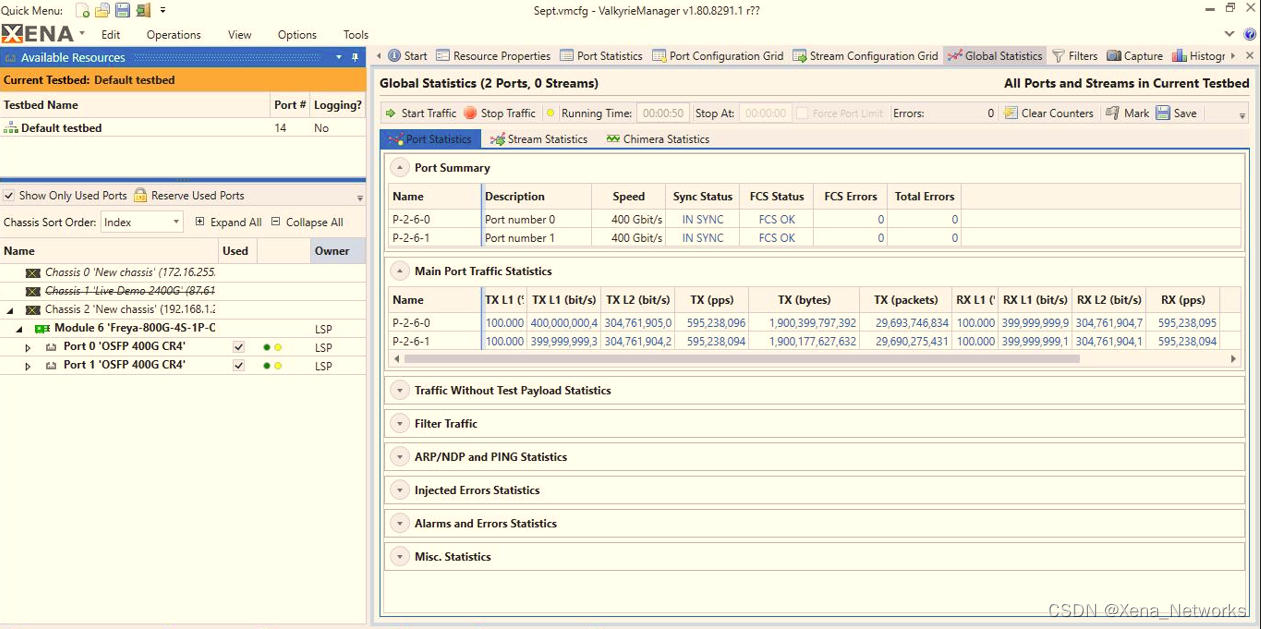

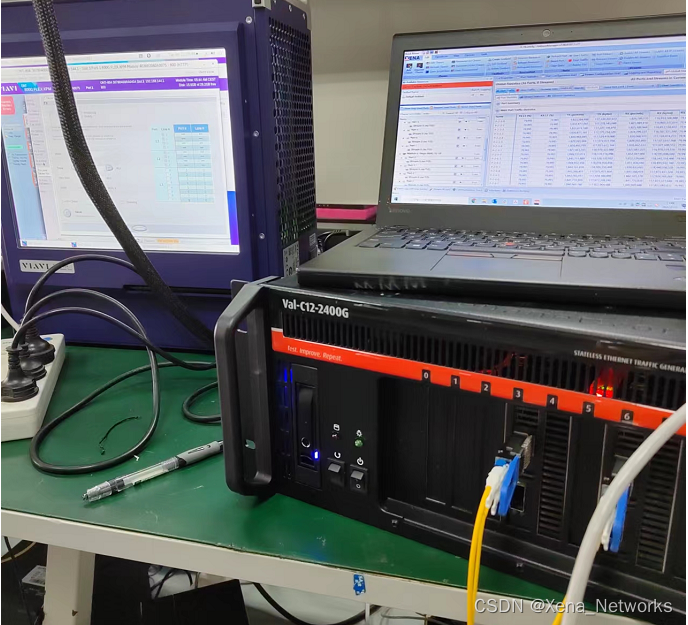

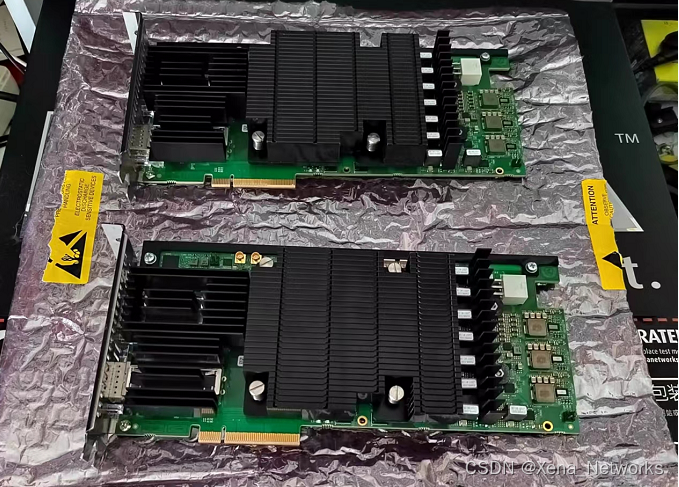

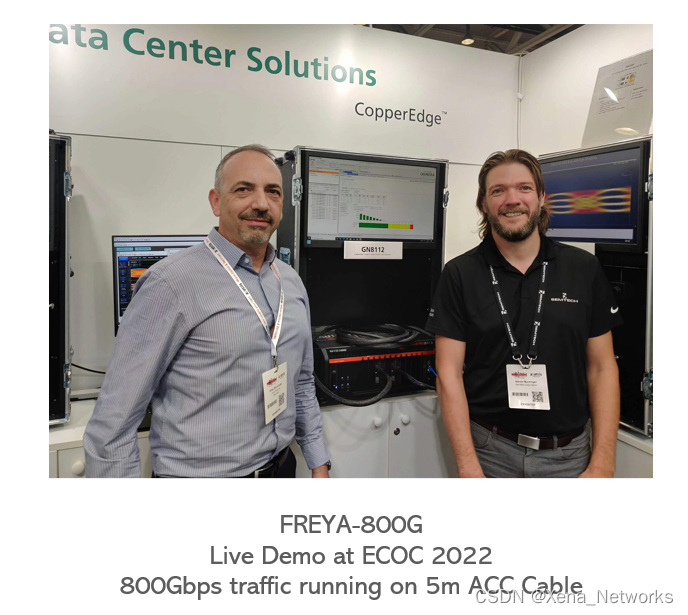

信雅纳(Xena)的Freya测试模块(图18)支持测试基于112Gbps SerDes PAM4的以太网,数据速率为100G/200G/400G/800G。

数据速率为100G/200G/400G/800G。Freya是为交换机、收发器和PHY设计验证和质量保证而设计的。该模块的主要特点是。

- 4种速度。800G、400G、200G和100G

- 双介质和双接口类型。QSFP-DD800和OSFP800

- 支持112G SerDes (PAM4 112G)

- 用光学元件和DAC进行测试

- 丰富的L1功能

o 自动协商和链路训练(AN/LT)

o 高级信号完整性视图

o RS-FEC (544,514, t=15)

o FEC纠错图

o PRBS31Q

o 均衡控制

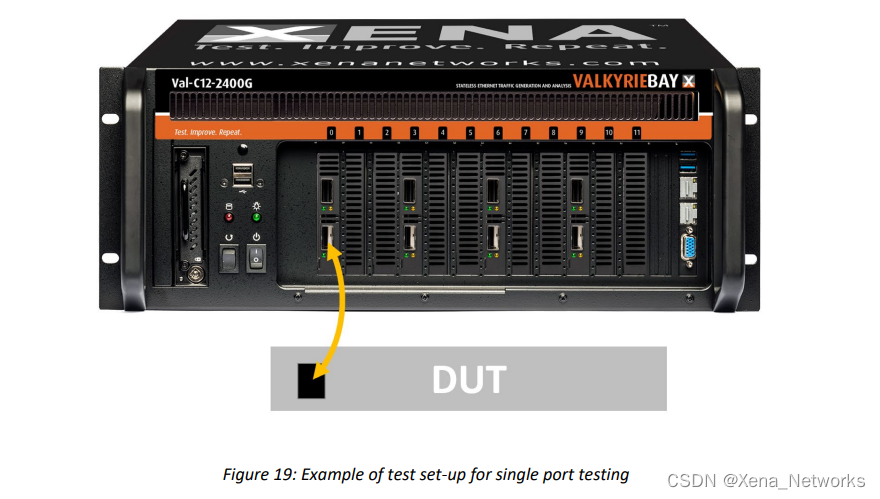

测试设置

图19显示了一个简单的例子,被测设备(DUT)是一个交换机端口,通过将其连接到配备有Freya-800G-4S-1P测试模块的ValkyrieBay机箱进行测试。

自动协商和链路训练

自动协商(AN)是以太网的一个关键特征,两个终端通过链路共享信息,从而确定终端能力中的最高共同点。

链路训练(LT)是另一个过程,当一个设备通过铜缆或背板连接到高速以太网端口时,就会发生这种情况。在这种情况下,重要的是对传输信号的特性进行调整,使其在铜缆上得到最佳的传输。

你的测试的一个好的起点是测试DUT的端口,测试仪是启用AN,测试AN是否可以完成一个满意的结果。

如果你在直接连接电缆(DAC)上进行测试,那么使用LT来调整传输信号的参数以获得最佳性能是非常有益的。

高级PHY配置

在测试期间,可能需要在发射器和接收器处控制和监测SerDes的均衡器设置。这可用于不支持自动TX调谐自动协商的情况,或测试收发器使用各种TX均衡器设置的性能。

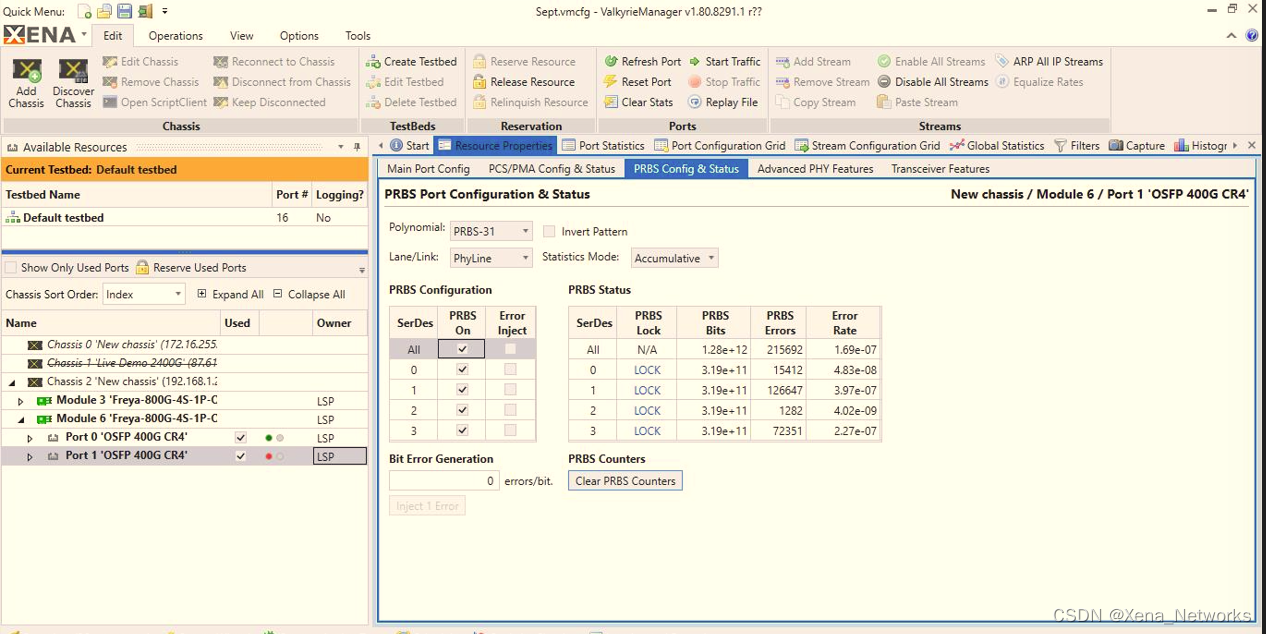

PRBS测试

可以使用伪随机二进制序列(PRBS)而不是完整的以太网数据包流来测试电缆和连接器。对于NRZ调制,使用PRBS31(231-1位的序列),但对于PAM4,每个符号周期有两个位,这意味着我们需要序列中的偶数位。出于这个原因,PAM4使用一个PRBS31Q序列(其中Q代表四级),由两个连续的PRBS31序列组成。PRBS31Q可以用来检查每个物理通道的误码率,并在发射器处插入比特错误。

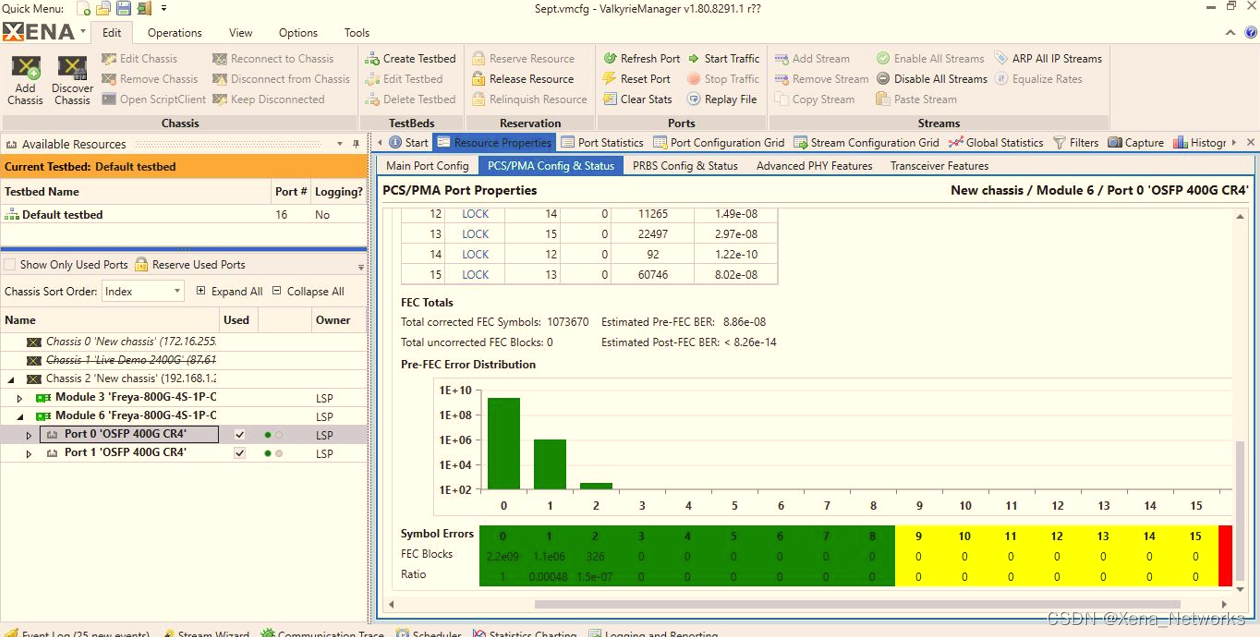

前FEC误差分布图

如图21所示,预FEC错误分布图绘制了纠错前FEC块的0、1、2、3等符号错误的数量。另外,你可以看到,在FEC之前,误码率为1.28 10-8。在FEC之后,没有比特错误,这由后FEC的<1.02 10-13表示。

如前所述,RS(544,514, t=15) FEC能纠正的最大错误量是15个符号错误。

信号完整性视图

如前所述,对于基于ADC的SerDes,传统的眼图是没有用的,而是使用图22所示的信号完整性视图。从这样的图中,你可以看到四个PAM4电平是否可以清楚地分辨出来。

第2层和第3层测试

对于高速以太网来说,在做任何其他测试之前,检查第1层的信号完整性是至关重要的,如本白皮书中所述。一旦建立了良好的信号完整性,当然还是要进行数据格式化/编码功能(第2层)和网络路径/路由性能测试。

总结

使用112Gbps SerDes测试400Gbps和800Gbps需要关注物理层(第1层),因为即使在相当小的传输长度之后,信号也会严重退化。另外,所使用的高级调制方案(PAM4)和基于ADC的SerDes功能,要求你的以太网测试设备从PCS/PMA内部的块中提取信号完整性措施,并考虑到几种类型的均衡和纠错编码。

Xena新的Freya系列测试模块支持所有你需要的功能,以测试第一层、第二层和第三层的设备和链路。对于第1层,测试基于112Gbps SerDes的系统的相关信号完整性参数包括自动协商、链路训练(用于电缆)、高级PHY均衡器调整、PRBS测试、预FEC错误分布和信号完整性视图。

有关Xena的Freya测试模块的信息

更多信息可以访问以下链接#

Freya - Ethernet Testing 112Gbps SerDes PAM4 100G 200G 400G 800G

样机资源

我们在本地有样机资源,感兴趣的朋友可以联系我们获得本地技术支持

https://xenanetworks.com/wp-content/uploads/xenadocuments/whitepaper/Testing-400G-using-112Gbps-SerDes.pdf?_cldee=Uk7cfOU5XXrffiBXkr1zzS99JLyYsKMW82B0-W4sNzqejgPbr5km4RBRB5iu_vpT&recipientid=contact-b5c0cc7629e5e711812970106fa5dd11-df935da421db4698b966aa8c4a934997&utm_source=ClickDimensions&utm_medium=email&utm_campaign=Website%20-%20White%20Paper&esid=1fcedb94-d4cb-4921-9841-5b704c1298ce

https://xenanetworks.com/wp-content/uploads/xenadocuments/whitepaper/Testing-400G-using-112Gbps-SerDes.pdf?_cldee=Uk7cfOU5XXrffiBXkr1zzS99JLyYsKMW82B0-W4sNzqejgPbr5km4RBRB5iu_vpT&recipientid=contact-b5c0cc7629e5e711812970106fa5dd11-df935da421db4698b966aa8c4a934997&utm_source=ClickDimensions&utm_medium=email&utm_campaign=Website%20-%20White%20Paper&esid=1fcedb94-d4cb-4921-9841-5b704c1298ce

963

963

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?