3.4 Variable types

Variables provide temporary storage for simulation.

The temporary storage required by simulation does not necessarily mean that actual silicon will require storage.

always_comb begin

sum = a + b;

endThe always_comb procedure in the preceding code snippet will be implemented as combinational logic in silicon. sum not require any type of storage in hardware.

always_ff @(posedge elk) begin

if (!rstN)

out <= '0;

else

out <= sum;

endOn the other hand, the always_ff procedure will be implemented in silicon as a flip-flop, which is a hardware storage device.

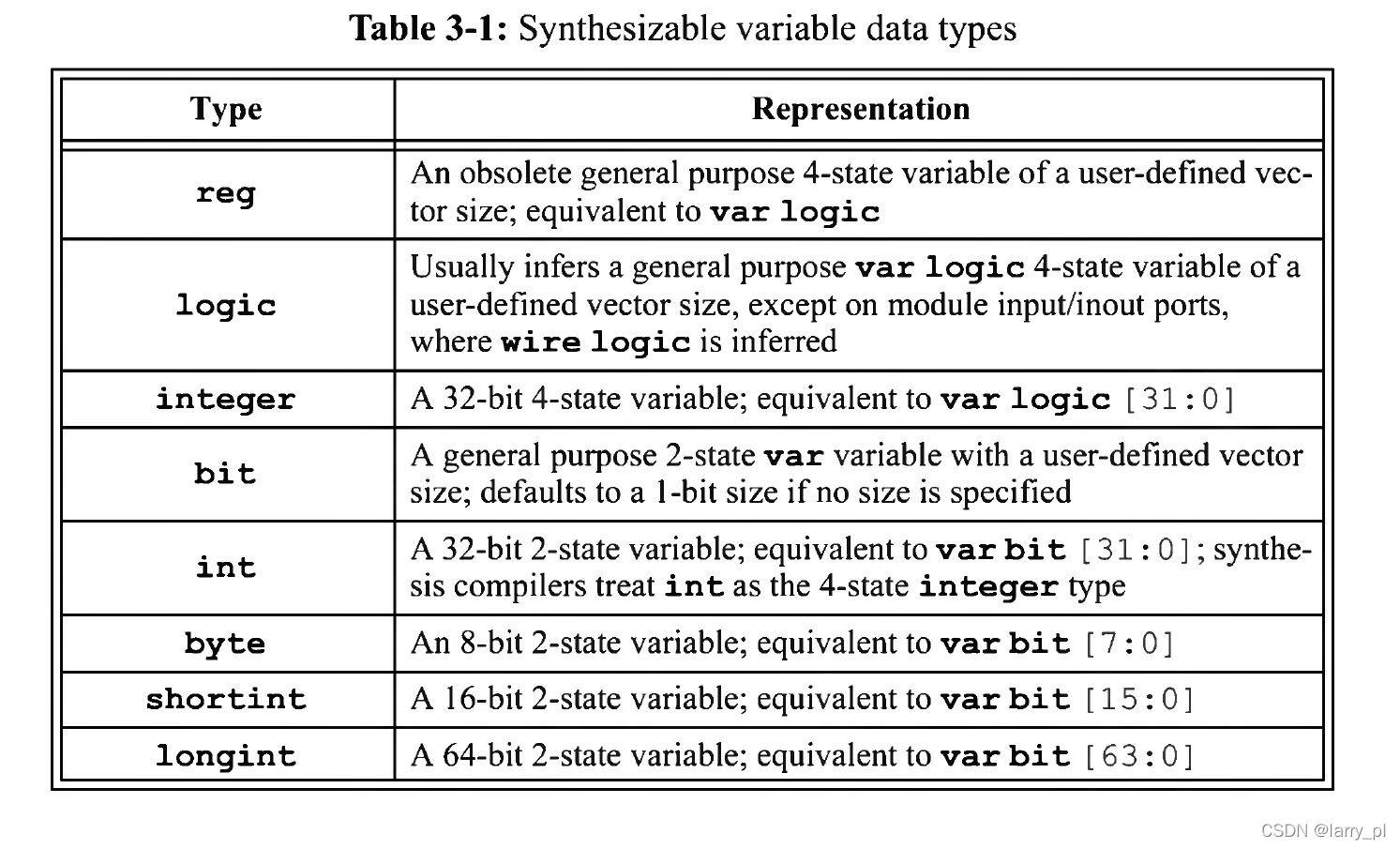

3.4.1 Synthesizable variable data types

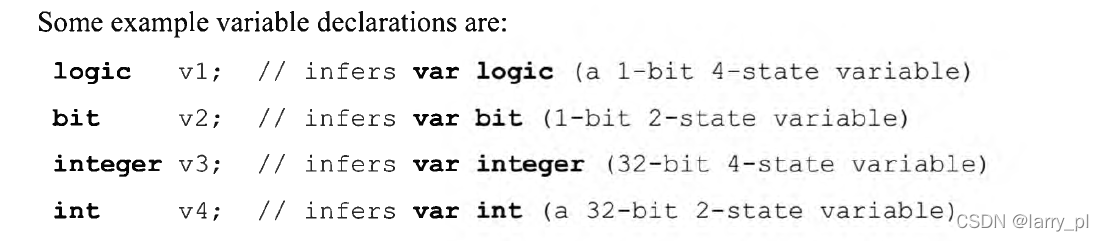

Variables are declared by specifying both a type and a data type. The type is the keyword var, which can be specified explicitly or implicitly inferred.

The var keyword is seldom used in actual SystemVerilog code.

SystemVerilog has keywords for several built-in variable data types. These keywords infer a either var logic (4-state) or var bit (2-state) variable type.

可综合的系统变量数据类型就两种 logic型 和 bit型,其他的如 reg、integer、int等都是在这两种基础上面的延申,具体见下表:

Note:Use the 4-state logic data type to infer variables in RTL models. Do not use 2-state types in RTL models. An exception to this guideline is to use the int type to declare for-loop iterator variables.(for 循环中使用int型,其他RTL models 中使用 4-state logic data type)。

1.The context dependent logic data type.

当作为 4-state 变量类型时,logic 相当于 reg。但 logic并不仅仅表示变量类型,同时logic还表示 a net type with 4-state values。

A net type will be inferred, when logic is used in conjunction with the declaration of a module input or inout port 。

A variable is inferred when the logic keyword is used by itself, or in conjunction with the declaration of a module output port.

2.The obsolete reg data type.

The reg data type is an obsolete data type left over from the original Verilog language. The logic type should be used instead of reg.

Using logic instead of reg can help prevent this misconception that a hardware register will be inferred.

3.Avoid 2-state data types in RTL models.

Since 2- state data types can only have a 0 or 1 value, a design with errors can appear to be functioning correctly during simulation. This is not good!

An appropriate place to use 2-state variables is for randomized stimulus in verification testbenches.

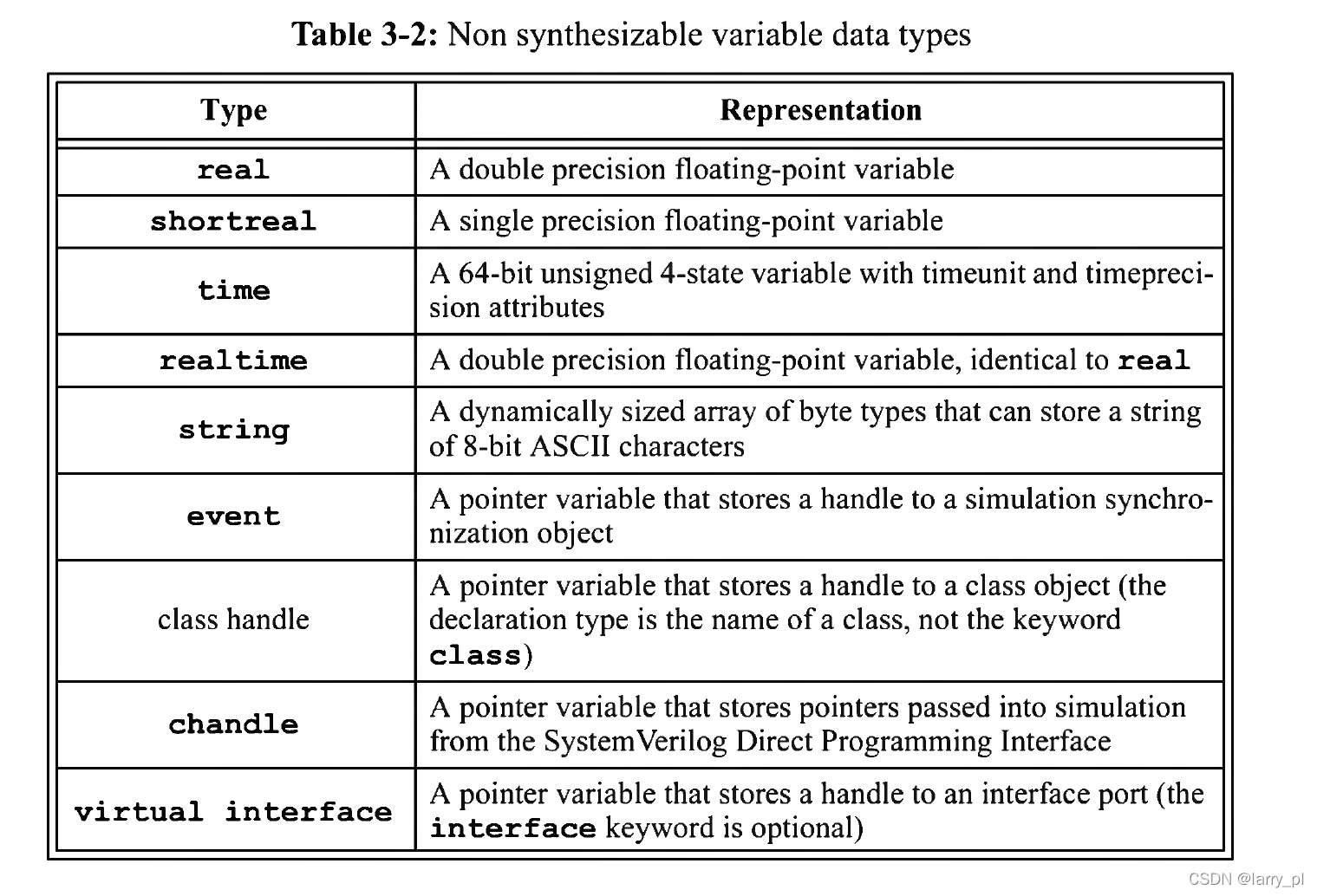

4.Non synthesizable variable types.

SystemVerilog has several variable types that are intended primarily for verification, and are not generally supported by RTL synthesis compilers.

3.4.2 Variable declaration rules (变量声明规则)

变量的声明需要指定一个type 和 data type,但 type 的 关键字 var 在SV中很少使用,所以一般只需要指定其datatype。

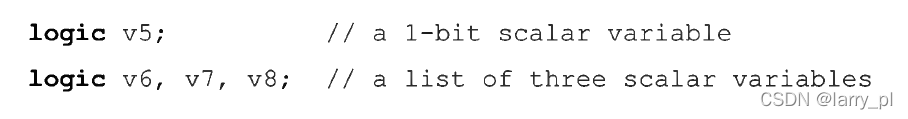

1.Scalar variables(标量的变量)

标量的变量就是只有 1-bit 的变量,reg、logic、bit的默认状态都是 1-bit scalars.

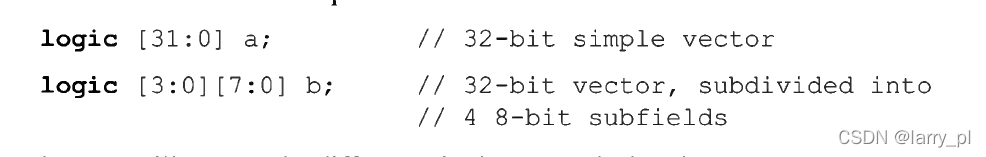

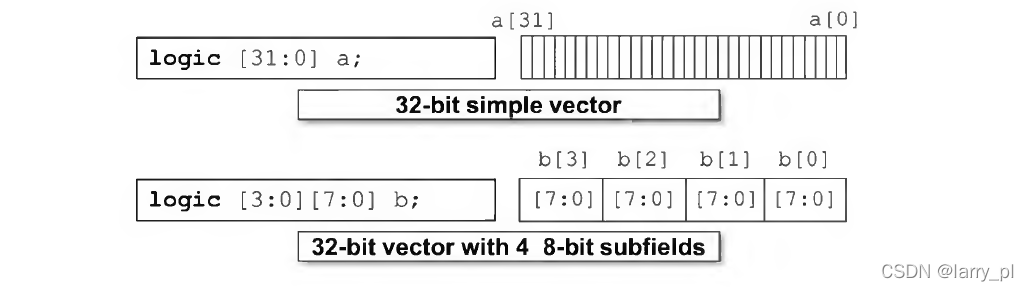

2.Vector variables (packed arrays) (矢量变量)

reg、logic、bit变量类型可以定义任意范围的Vector variables,规则如下:

datatype [MSB :LSB] dataname

such as : logic [31:0] v9 ; / / 32-bit vector, little endian

logic [1:32] v10 ; / / 32-bit vector, big endian

在 RTL model 中 最常用的是 little endian 类型。

byte, shortint, int, longint 和 integer 类型 的范围由默认的范围决定。

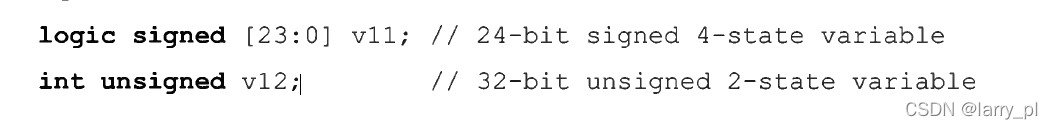

3.Signed and unsigned variables .(符号变量和无符号变量)

A signed variable can store positive and negative values.

An unsigned variable only stores positive values.

By default :reg, logic, bit and time data types are unsigned variables.

byte, shortint, int, integer and longint data types are signed variables.

This default can be changed by explicitly declaring a variable as signed or unsigned.

4.Vectors with subfields.

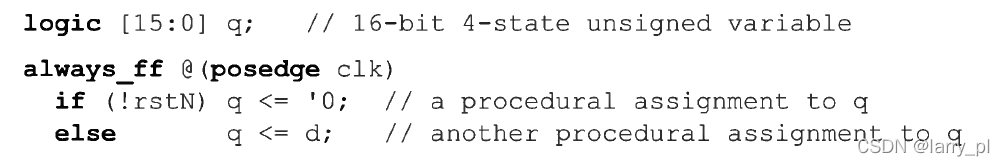

3.4.3 Variable assignment rules (变量赋值的规则)

• Procedural assignment statement 例如always块、initial块。

• Continuous assignment statement 连续语句赋值。

• Note:A variables can only be assigned by a single source。

变量只能由一种方式赋值,一个变量被 assign 赋值之后 就不能在 procedural block 中赋值了,但是同一个变量可以在同一个procedural block中多次赋值。如下所示:

本文详细介绍了SystemVerilog中的变量类型,包括可综合的logic和bit型,以及不再推荐使用的reg型。强调在RTL模型中使用4-state的logic类型,避免2-state类型以防止错误。此外,讨论了变量声明规则,如标量和矢量变量的声明,并提到了变量赋值的限制。最后,指出了变量赋值只能由单一源进行。

本文详细介绍了SystemVerilog中的变量类型,包括可综合的logic和bit型,以及不再推荐使用的reg型。强调在RTL模型中使用4-state的logic类型,避免2-state类型以防止错误。此外,讨论了变量声明规则,如标量和矢量变量的声明,并提到了变量赋值的限制。最后,指出了变量赋值只能由单一源进行。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?