接前一篇文章:WM8978 —— 带扬声器驱动程序的立体声编解码器(6)

十、音频接口

WM8978具有一个标准的音频接口,支持立体声数据在芯片之间的传输。该接口是一个3线标准音频接口,支持多种音频数据格式,包括I2S、DSP/PCM模式(其中发送LRC同步加2个数据打包字的突发模式)、MSB-First、left justified和MSB-First、right justified,并且可以工作在主模式和/或从模式下。

1. 相关引脚

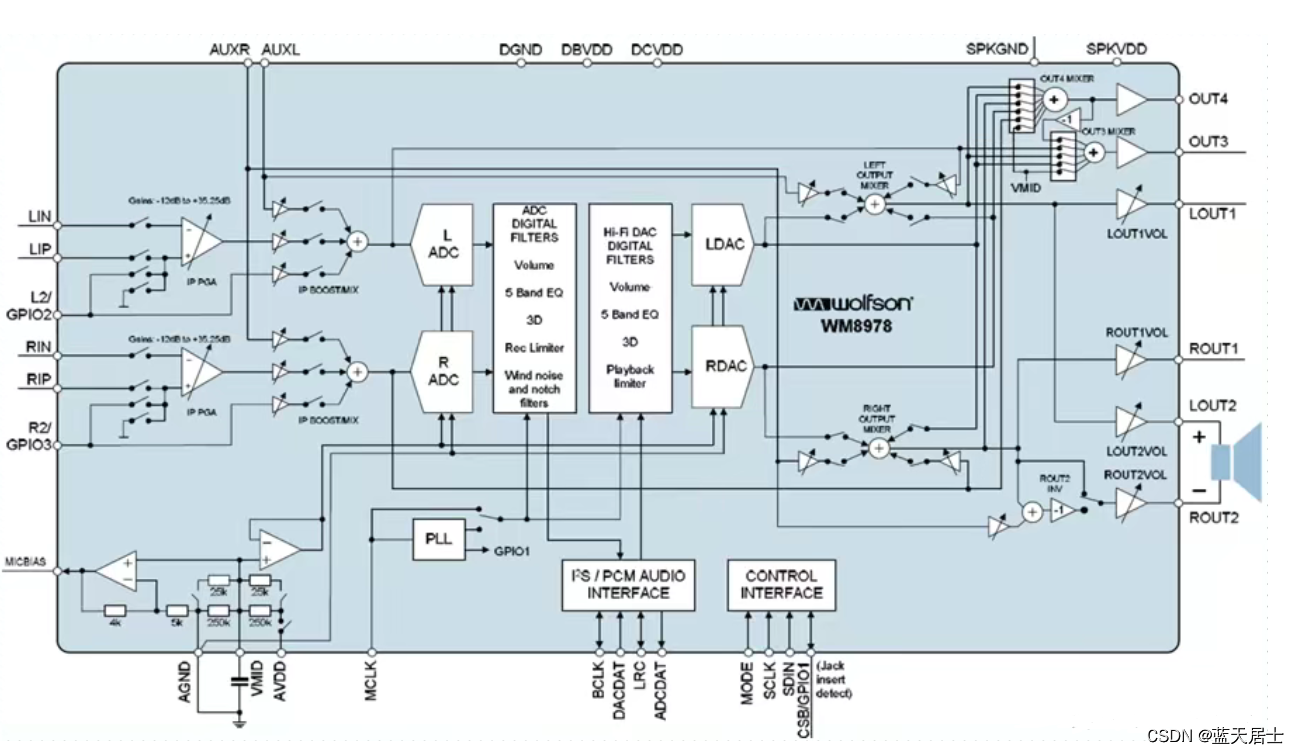

WM8978中与音频接口相关的引脚分为两类:一类是控制接口(CONTROL INTERFACE),另一类是数据接口(I2S / PCM AUDIO INTERFACE)。

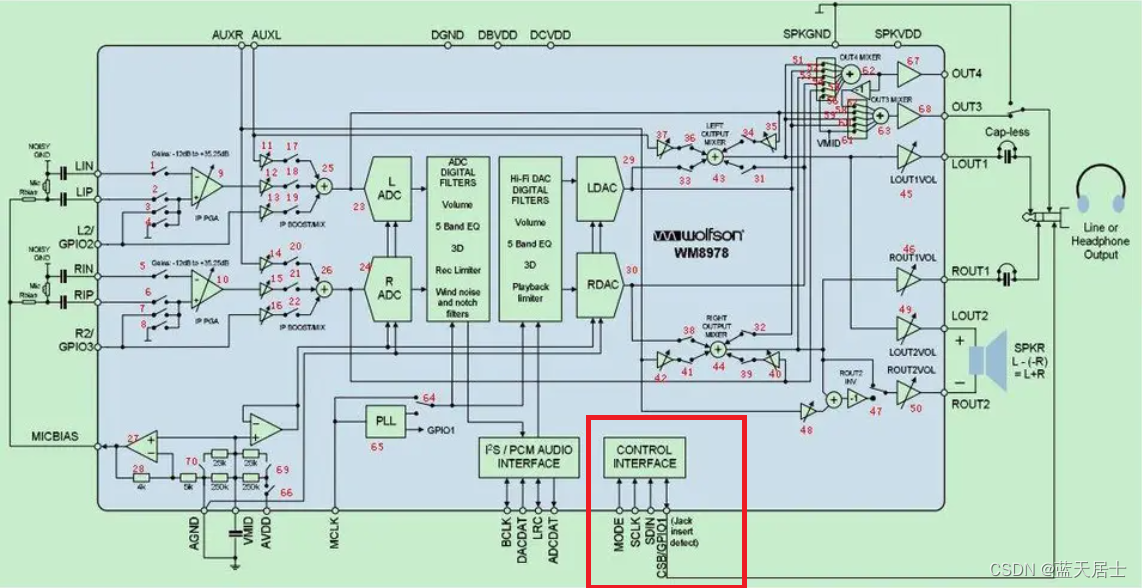

(1)控制接口(CONTROL INTERFACE)

为了实现对所有功能的完全软件控制,WM8978提供了2线或3线控制接口的选择。它是完全兼容的,是各种工业标准微处理器、控制器和DSP的理想合作伙伴。

通过MODE引脚在模式之间进行选择。在2线模式中,设备的地址固定为0011010。

控制接口相关电路结构如下(下图红色框中部分):

相关引脚如下:

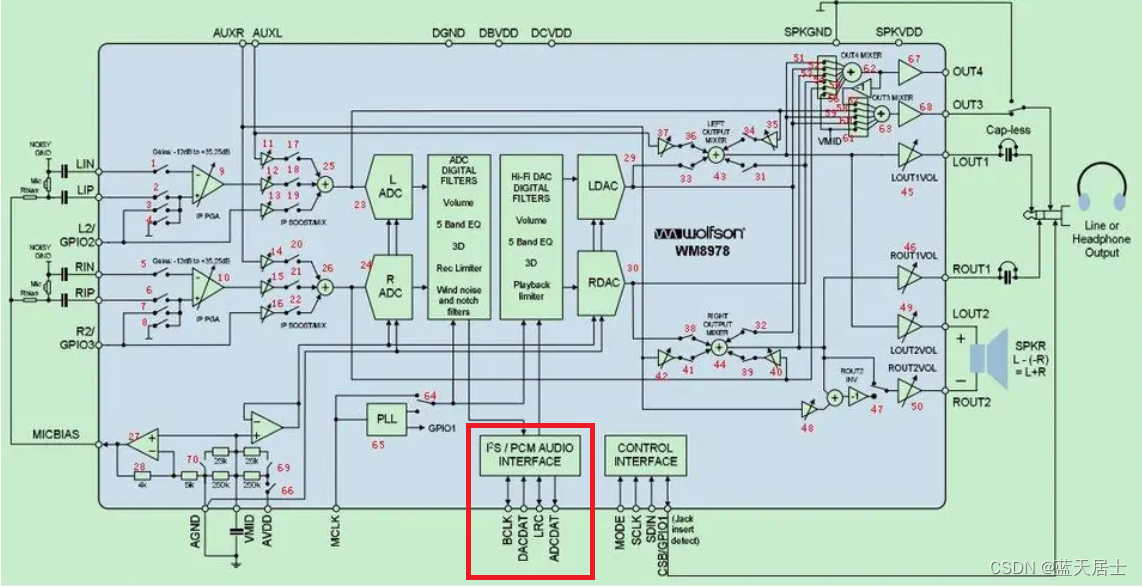

(2)数据接口(I2S / PCM AUDIO INTERFACE)

WM8978有一个标准的音频接口,支持立体声数据在芯片之间的传输。该接口是一个3线标准音频接口,支持多种音频数据格式,包括I2S、DSP/PCM模式(传输LRC同步加2个数据压缩字的突发模式)、左对齐的MSB First和右对齐的MSBFirst,并且可以工作在主模式或从模式下。

数据接口相关电路结构如下(下图红色框中部分):

十一、I2S相关知识补强

以下内容参考:

一文搞懂I2S通信总线_i2s读出来的数据全是一样的-CSDN博客

stm32 VM8978 音乐播放_wm8978-CSDN博客

1. I2S概述

I2C和I2S都是由Philips公司(2006年迁移到NXP)发布的串行总线,I2S可以认为是I2C的一个变种。

IIC的英文全称为Inter-Integrated Circuit,中文译为内置集成电路(总线),也可写作I2C。而IIS的英文全称为Inter-IC Sound,中文译为集成电路内置音频总线,也可写作I2S。

I2S是一种广泛应用于数字音频设备之间的数字音频传输的串行总线接口标准。它最初由飞利浦(Philips)公司开发,用于解决在集成电路之间传输音频数据的问题。I2S采用了独立的导线传输时钟与数据信号的设计,通过将数据和时钟信号分离,避免了因时差诱发的失真,为用户节省了购买抵抗音频抖动的专业设备的费用。

I2S总线的特点如下:

- 支持全双工和半双工模式

- 支持主、从模式设置

- 8位可编程线性预分离器,可实现精确的音频采样频率(8~192KHz)

- 支持16位/24位/32位数据格式

- 数据包帧固定为16位(仅16位数据帧)或32位(可容纳16/24/32位数据帧)

- 可编程时钟极性

- 支持MSB对齐(左对齐)、LSB对齐(右对齐)飞利浦标准和PCM标准等I2S标准

- 支持DMA数据传输(16位宽)

- 数据方向固定为MSB在前

- 支持主时钟输出(固定为256*fs,fs即音频采样率)

以下是正点原子对于I2S的介绍:

I2S也叫IIS,即Inter IC Sound总线,又称集成电路内置音频总线,是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准。该总线专责于音频设备之间的数据传输,广泛应用于各种多媒体系统。它采用了沿独立的导线传输时钟与数据信号的设计,通过将数据和时钟信号分离,避免了因时差诱发的失真,为用户节省了购买抵抗音频抖动的专业设备的费用。

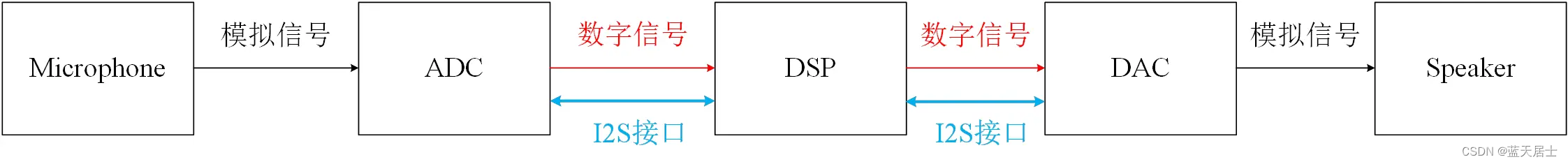

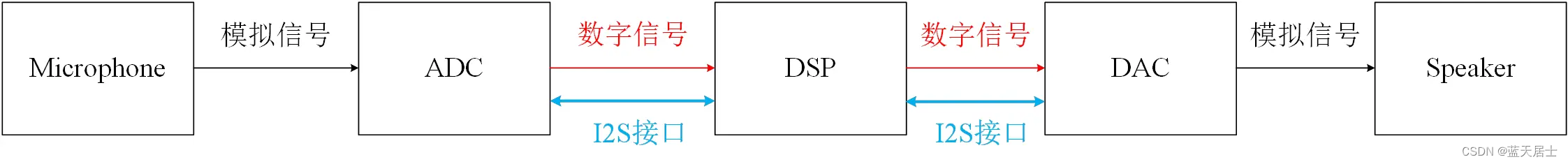

2. I2S应用场景

I2S协议定义了音频数据的传输格式、时序和控制信号。在工作中音频采集和输出,AD和主芯片之间的通信均是通过I2S进行通信的,其应用场景如下:

I2S的应用示意图

- I2S RX方向

麦克风在机械振动下将声音信号转变为电压信号,电压信号经过放大等处理,给到ADC采样,将模拟信号转化为数字信号;音频在ADC与DSP之间的传输协议就是使用的I2S协议。如上图中左半部分所示。

- I2S TX方向

数字信号经过编码、存储、压缩等技术后,发送给解码器-DAC(DSP、专用解码器),将数字信号还原为模拟信号,最后给到喇叭完成声音/音频的播放。音频在DAC与DSP之间的传输就是使用I2S协议。如上图中右半部分所示。

3. I2S协议中常见的参数

- 位宽(Word Length)

位宽指定每个采样数据的位数,通常为16位或32位。较大的位宽可以提供更高的分辨率和动态范围。

- 时钟极性(Clock Polarity)

时钟极性确定了数据位传输的时钟沿。根据具体的I2S设备和系统设置,可以定义在时钟上升沿或下降沿开始数据传输。

- 帧同步极性(Frame Sync Polarity)

帧同步极性确定了帧同步信号的有效电平。帧同步信号指示音频数据的帧起始和结束位置。

- 传输格式(Data Format)

传输格式定义了音频数据的编码方式,传输格式还可以指定数据的顺序,如左声道先传输还是右声道先传输。

4. I2S基本信号

I2S接口通常由三类信号线组成,分别是:

- 时钟线(Continues Serial Clock,SCK)

SCK(也叫SCLK)线提供了同步音频数据传输的时钟信号。确定了数据传输的速度和时序。该时钟也称为Bit Clock(BCLK)。SCK也称为位时钟BCLK,其与数字音频数据一一对应。

SCK的频率=2x采样频率x位宽

在WM8978中,对应的引脚为:

![]()

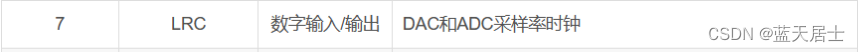

- 左/右声道时钟线(Left-Right Clock,LRCK)

也称为帧时钟(也叫WS)、帧同步信号,用于切换左右声道数据,1为右声道数据,0左声道数据。LRCK线指示了当前传输的是左声道的音频数据还是右声道的音频数据。

LRCK的频率=采样频率

在WM8978中,对应的引脚为:

- 数据线(Serial Data,SD)

SD线也称为SDATA,用于传输实际的音频数据(以二进制补码形式)。TX方向为:Serial Data Out(SDOUT);RX方向为:Serial Data In(SDIN)。数据的位宽可以根据具体应用而变化,通常为16位或32位。

另一种讲法:

- SDATA(SD)

就是用二进制补码表示的音频数据。最高位拥有固定的位置,而最低位的位置则是依赖于数据的有效位数。

在WM8978中,对应的引脚为:

除了以上三类信号线外,I2S总线还有一根系统时钟线。

- 主时钟(Master Clock,MCLK)

MCLK也叫系统时钟(Sys Clock),一般为了使系统间能够更好地同步时增加MCLK信号,MCLK的频率 = 128或者256或者512 * 采样频率;

在WM8978中,对应的引脚为:

5. I2S协议接口时序

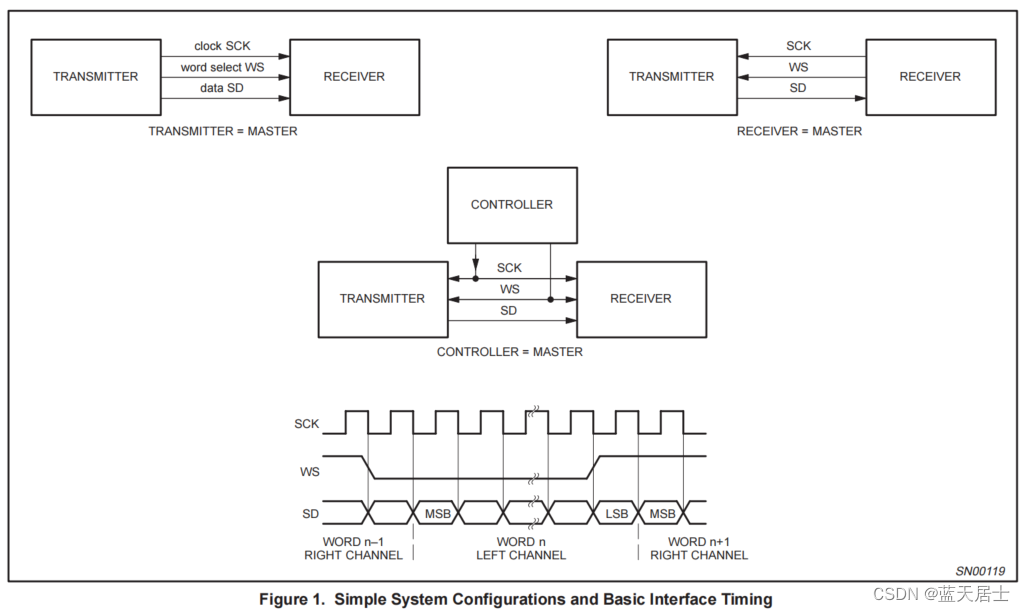

6. I2S工作模式

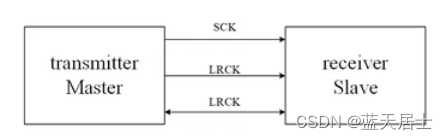

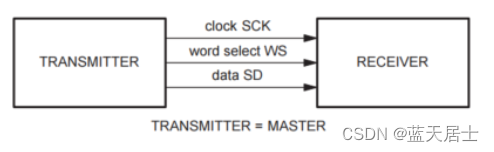

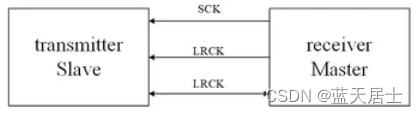

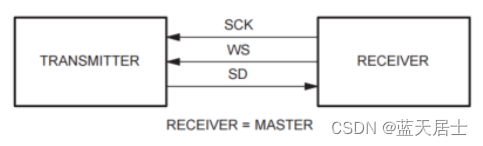

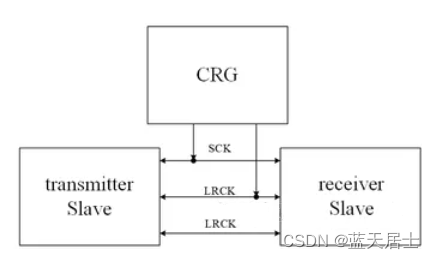

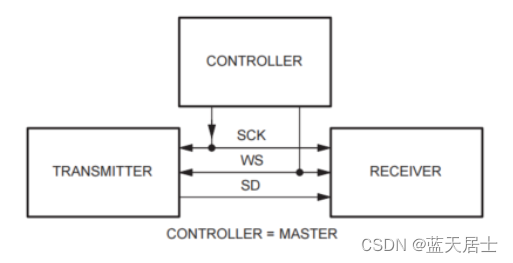

I2S工作模式可以是主模式(Master Mode)或从模式(Slave Mode)。两者唯一的区别是:Master Mode提供时钟信号(SCK)和帧同步信号(LRCK)。如下图所示,一共存在三种工作模式,分别是:

- 发射器(transmitter)为Master,接收器(receiver)为Slave

此时由发射器提供SCK和LRCK。

- 接收器(receiver)为Master,发射器(transmitter)为Slave

此时由接收器提供SCK和LRCK。

- 发射器(transmitter)和接收器(receiver)均为Slave

7. I2S数据传输模式

I2S接口标准中,存在三种数据传输模式,分别是:飞利浦标准模式(I2S mode),左对齐(Left Justified)和右对齐(Right Justified)三种传输模式。

也即,在统一的I2S硬件接口下,出现了多种不同的I2S数据格式,可分为:I2S Philips标准、左对齐(MSB)标准和右对齐(LSB,也叫日本格式、普通格式)标准。

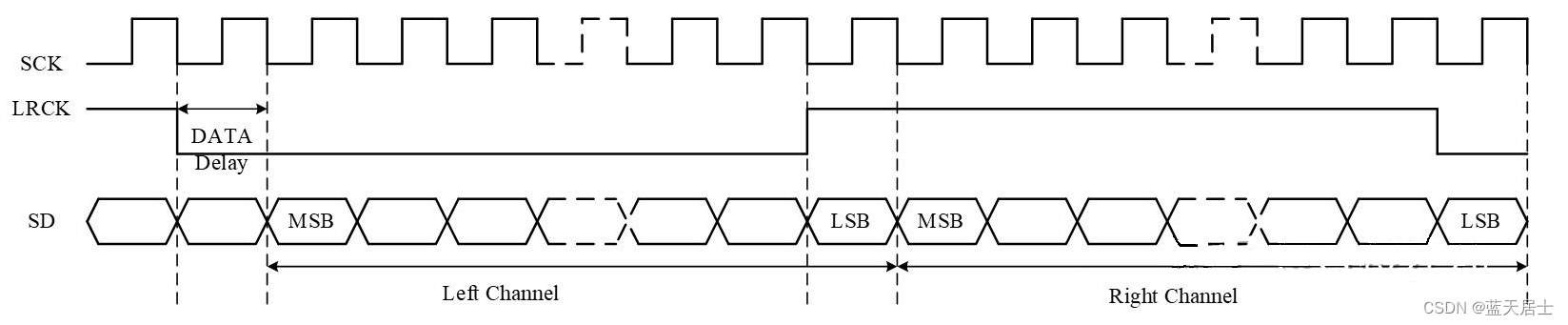

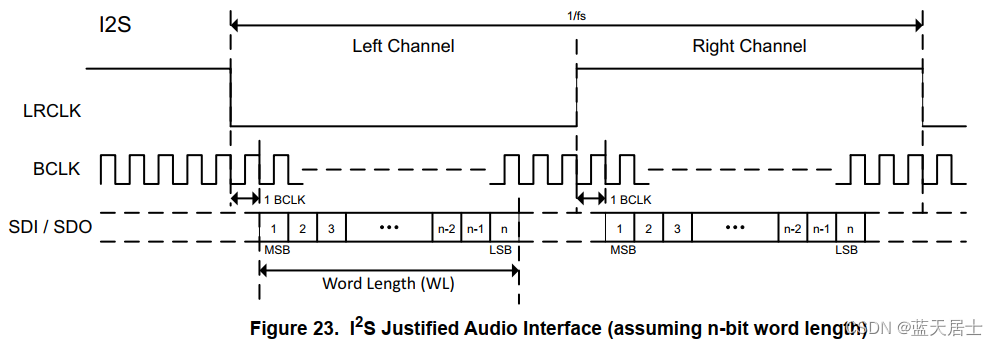

(1)飞利浦标准(I2S)模式

I2S Philips标准时序如下图所示:

其主要特点如下:

- LRCK(左右声道选择信号)

LRCK信号用于指示当前数据帧是左声道数据还是右声道数据。飞利浦格式中,当LRCK为低时,表示当前传输的数据是左声道数据;当LRCK为高时,表示当前传输的数据为右声道数据。

- SCK(位时钟)

数据传输的时钟信号。在SCK下降沿发送数据,在SCK上升沿采样数据。

- Data Delay(数据延迟)

发送的有效数据相对于LRCK的跳变沿(从0到1或从1到0)延迟一个时钟周期。

- MSB(最高位优先)

数据发送从MSB开始,数据MSB与LRCK delay 1个SCK的边沿对齐。

以上特点综述如下:

使用LRCLK信号表示当前正在发送数据所属的声道,LRCLK为“1”表示正在传输的是右声道的数据,为“0”则表示正在传输的是左声道的数据。LRCLK信号从当前声道数据的第一个位(MSB)之前的一个时钟开始有效。

LRCLK信号在BCLK(即SCK)的下降沿变化,发送方在时钟信号BCLK的下降沿改变数据,接收方在时钟信号BCLK的上升沿读取数据。正如上文所说,LRCLK频率等于采样频率Fs,一个LRCLK周期(1/Fs)包括发送左声道和右声道数据。

对于这种标准I2S格式的信号,无论有多少位有效数据,数据的最高位总是出现在LRCLK变化(也就是一帧开始)后的第2个BCLK脉冲处。这就使得接收端与发送端的有效位数可以不同。如果接收端能处理的有效位数少于发送端,可以放弃数据帧中多余的低位数据;如果接收端能处理的有效位数多于发送端,可以自行补足剩余的位。

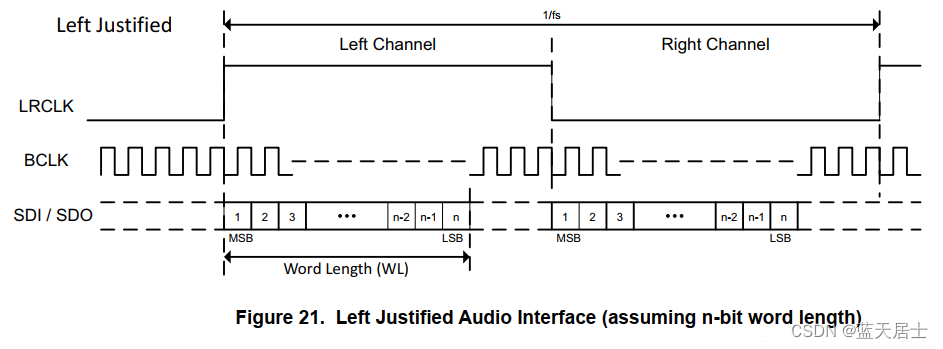

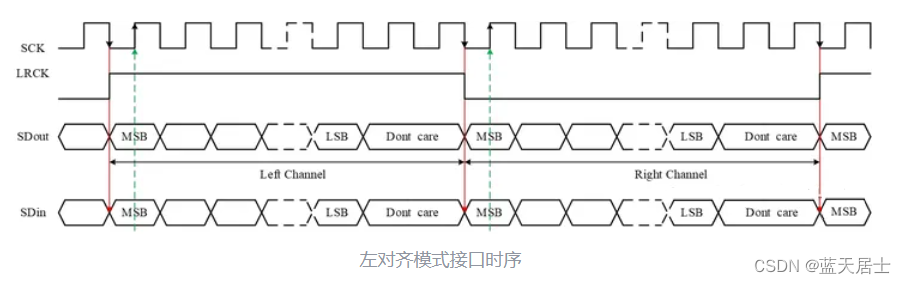

(2)左对齐(Left Justified)模式

左对齐(MSB)标准时序如下图所示:

其主要特点如下:

- LRCK(左右声道选择信号)

LRCK信号用于指示当前数据帧是左声道数据还是右声道数据。左对齐格式中,当LRCK为高时,表示当前传输的数据为左声道数据;当LRCK为低时,表示当前传输的数据为右声道数据。

正好与飞利浦标准模式相反。

- SCK(位时钟)

数据传输的时钟信号。在SCK下降沿发送数据,在SCK上升沿接收数据。

- 无Data Delay(无数据延迟)

发送的有效数据相当于LRCK跳变沿(从0到1或从1到0)不延迟。

- MSB(最高位优先)

数据发送从MSB开始;数据MSB与LRCK跳变沿对齐。

左对齐(MSB)标准较少使用,在LRCLK发生翻转的同时开始传输数据,注意LRCLK为1时,传输的是左声道数据,LRCLK为0时,传输的是右声道数据,这刚好与I2S Philips标准相反。

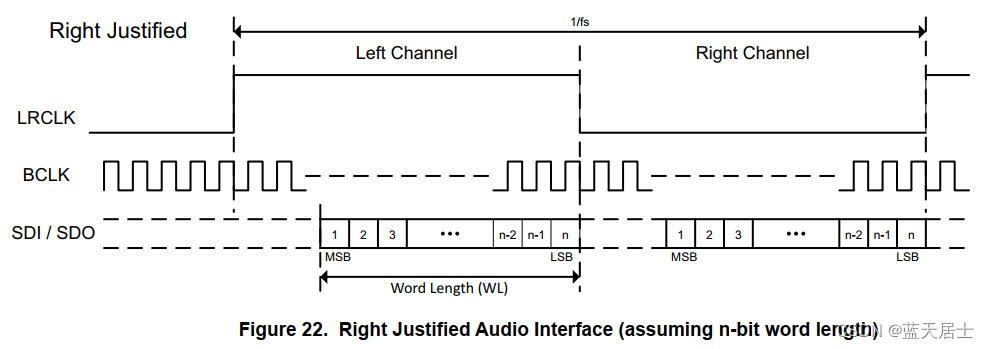

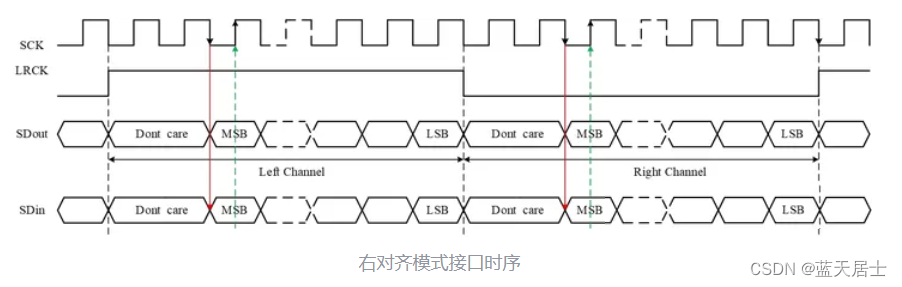

(3)右对齐(Right Justified)模式

右对齐(LSB)标准时序如下图所示:

其主要特点如下:

- LRCK(左右声道选择信号)

LRCK信号用于指示当前数据帧是左声道数据还是右声道数据。右对齐格式中,当LRCK为高时,表示当前传输的数据为左声道数据;当LRCK为低时,表示当前传输的数据为右声道数据。

正好与飞利浦标准模式相反。

- SCK(位时钟)

数据传输的时钟信号。在SCK下降沿发送数据,在SCK上升沿接收数据。

- 无Data Delay(无数据延迟)

发送的有效数据相当于LRCK跳变沿(从0到1或从1到0)不延迟。

- MSB(最高位优先)

数据发送从MSB开始;数据LSB与LRCK跳变沿对齐。

右对齐(Right Justified)模式下,声音数据LSB传输完成的同时,LRCLK完成第二次翻转(刚好是LSB和LRCLK是右对齐的,所以称为右对齐标准)。注意LRCLK为1时,传输的是左声道数据,LRCLK为0时,传输的是右声道数据,这刚好与I2S Philips标准相反。

更多内容请看下回。

本文详细介绍了WM8978编解码器的音频接口特性,包括支持的3线标准I2S接口,支持的多种音频数据格式,以及控制接口和数据接口的结构。特别重点讲解了I2S通信协议,包括I2S与I2C的关系,工作模式,数据传输模式,以及LRCK和SCK信号的作用。

本文详细介绍了WM8978编解码器的音频接口特性,包括支持的3线标准I2S接口,支持的多种音频数据格式,以及控制接口和数据接口的结构。特别重点讲解了I2S通信协议,包括I2S与I2C的关系,工作模式,数据传输模式,以及LRCK和SCK信号的作用。

2854

2854

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?