DATA 2021 波士顿大学

项目地址:https://github.com/bu-icsg/TAP-2.5D

论文地址:

一、介绍、

这些异构的2.5D集成系统中的设计挑战之一是芯片间网络的物理设计。在这里,物理设计规定了如何放置。Chiplet及其在给定逻辑拓扑下如何高效地布线。我们希望在Chiplet之间提供所需的连接性,同时最小化面积和成本,最大化性能,并避免基于热的故障。传统上,单片芯片的物理布局专注于减少连接宏单元的总线长并最小化面积[11],然而,这最终会导致紧密排列的chiplet部件,具有高功率密度,则可能会遭受基于热的故障。

与最先进的方法(详见第二部分)不同,这些方法输出芯片的小巧布局,我们提出在异构2.5D系统中战略性地插入不同芯片之间的间距,以降低温度并最小化芯片间线长。这种新的物理设计方法称为TAP-2.5D。

二、相关工作

我们的工作考虑了各种芯片数量、芯片大小、芯片形状、非均匀连接和带宽要求,并搜索了一个不受限制的芯片放置解决方案,其中智能插入间距。

三、TAP-2.5D方法

A.热评价

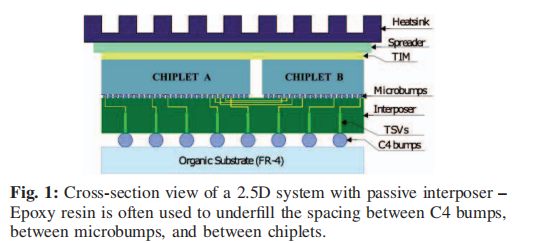

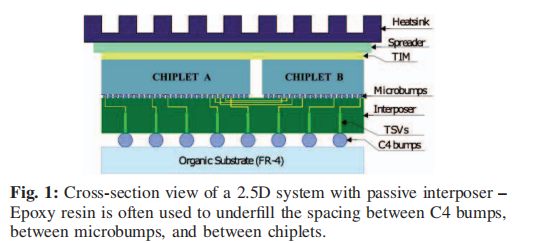

我们使用了HotSpot的扩展[27],该工具提供了详细的异构3D建模功能,支持每个建模层中的异构材料。为了建模我们的2.5D系统,我们堆叠了六个建模层。从下往上,如图1所示。我们将环境温度设定为45°C,网格模型分辨率设为64×64,散热器边缘尺寸为中介层边缘尺寸的2倍,散热片边缘尺寸为散热器边缘尺寸的2倍。为了使所有模拟中的传热系数保持一致,我们调整了散热器的对流阻力。每个HotSpot模拟的运行时间平均为23秒。

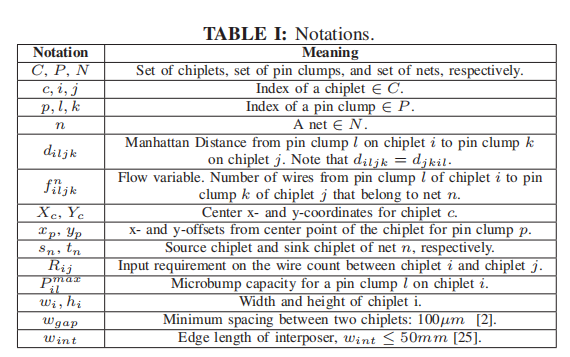

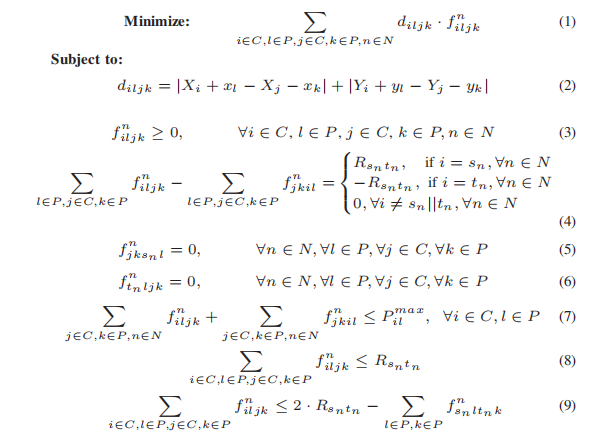

B.路由优化

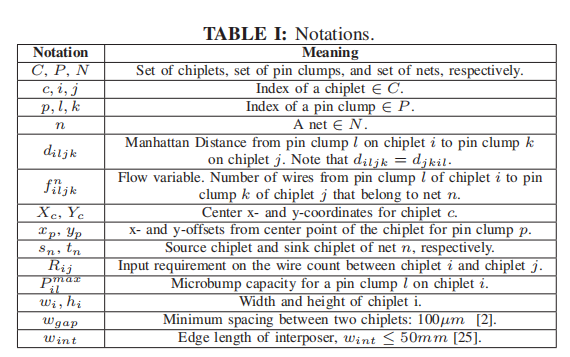

我们的布线工具的目标是找到一种布线方案,以最小化芯片间网络的总线长。将其建模为混合整数线性规划(MILP)求解器,为了限制问题规模,我们将沿芯片外围的微凸点分组为引脚簇。MILP求解器的输入包括我们热感知布局器(第III-C节)生成的芯片放置、估计的芯片间通信微凸点资源以及2.5D系统的芯片间连接性和带宽需求。MILP求解器输出最优布线方案及相应的总线长。

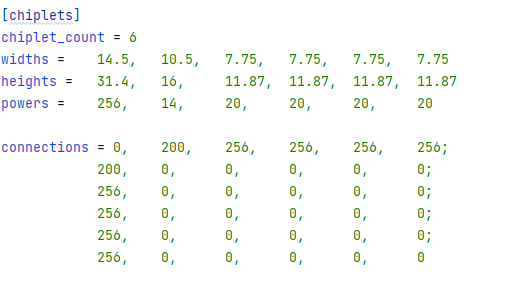

IBM Software Subscription and Support overview cplet

(1) 目标是最小化芯片间网络的总布线长度,其中 fijkf_{ijk}fijk 是芯片间传输的流量,dijkd_{ijk}dijk 是芯片间的 Manhattan 距离。l是芯片i的引脚,芯片j的引脚是k。

(2)表示X和Y芯片的曼哈顿距离,x:表示芯片 c引脚的偏移量(例如,从芯片中心到引脚的距离)

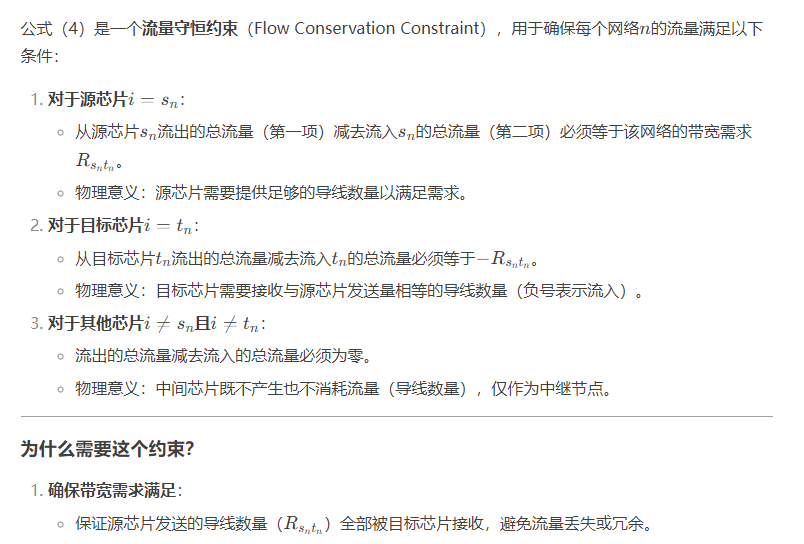

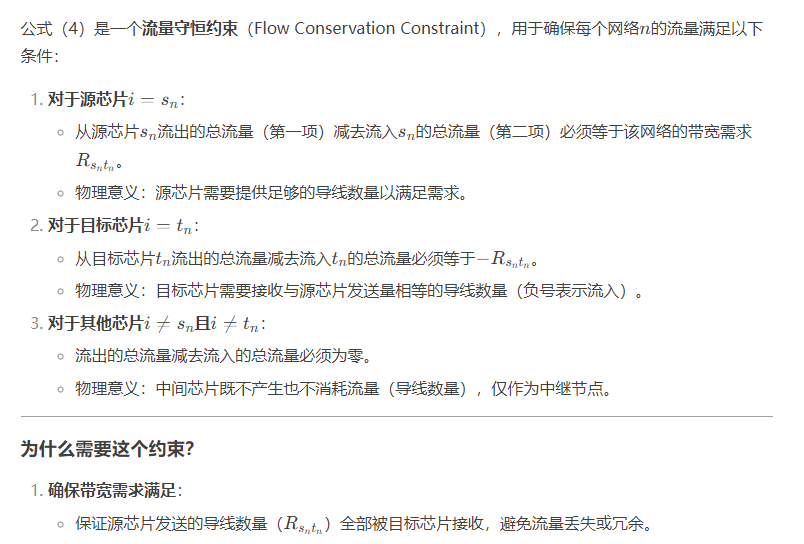

(4)

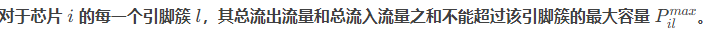

(5)即目标芯片或中间芯片不能把流量往回发送到源芯片

(6)目标芯片不能继续向外发送该网络的流量

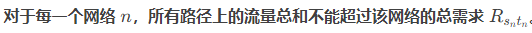

(7) ,通常由引脚l的凸点决定。

,通常由引脚l的凸点决定。

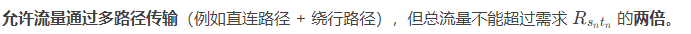

(8)

(9)

我们的MILP求解器是用IBM ILOG CPLEX v12.8 Python API实现的。每个路由优化的平均运行时间为5秒。

C.热感知定位算法

我们在芯片小结之间战略性地插入间距以提高散热效果,我们不能使用最先进的布局表示方法,如Sequence Pair [20]、TCG [21]、Otree [22]和B-tree [11],因为这些表示方法假设紧凑布局。其次,每个芯片小结布局的热评估和布线优化过程大约需要30秒。在可接受的仿真时间内,我们的方法必须找到满意的解决方案,且步骤有限。

1)安放描述:

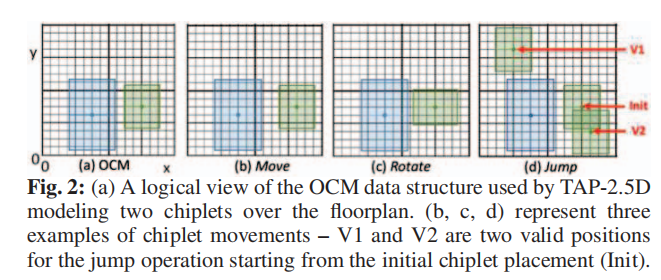

为了表示无限制的放置,我们使用芯片中心点的x和y坐标,以及芯片的宽度和高度。如图2(a)所示,假设芯片中心只能放置在网格的交点上。我们假设网格的粒度为1毫米,以放置芯片中心(芯片的宽度和高度可以是任意值),这在有限的时间内提供了解空间与解质量之间的良好平衡。有效的芯片放置没有两片芯片之间有重叠,并确保芯片[28]之间至少有0.1毫米的间隙(公式(10))。此外,芯片必须完全位于中介层上(公式(11))。

2)初次安置

然而,我们希望在有限的时间内找到满意的解决方案(如第三节C5所述,我们将模拟校准至25小时后停止)。因此,良好的初始布局至关重要。在我们的方法中,我们采用了Chen等人开发的[11]生成初始布局的方法。该方法使用B*tree数据结构,并采用快速SA算法,该算法能高效地解决现代固定轮廓布局问题中的面积减小和线长最小化问题——

Compact-2.5D

3)邻域放置

为了找到一个邻域放置,我们通过移动(图2(b))、旋转(图2(c))和跳跃(图2(d))操作来扰动当前芯片组的放置。对于旋转操作,我们随机选择一个芯片组并将其旋转90度。对于移动操作,我们随机选择一个芯片组,并以最小步长(在我们的案例中为1毫米)向上下左右方向移动,同时确保移动后没有芯片组重叠。仅使用旋转和移动操作时,芯片组的相对位置不太可能改变。即某个芯片组无法在某些方向上移动,因为其他芯片组挡住了路径。因此,我们使用跳跃操作。通过跳跃操作,随机选择的芯片组可以跳到中介层上的任何有效空位。有效的邻居放置应避免芯片组之间的重叠,并且完全位于中介层上。

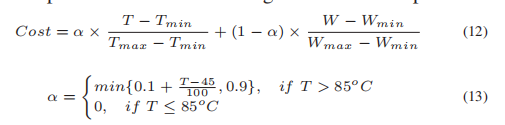

4)SA费用函数

TAP-2.5D的目标是在给定网络连接的情况下,找到一个芯片间布线方案,同时最小化异构2.5D系统的运行温度和总线长。公式(12)展示了我们的SA成本函数。我们使用最小最大缩放对温度(T)和线长(W)进行归一化处理,在设计时动态调整α以适应温度水平,如公式(13)所示。当温度较高时,我们的算法优先降低温度(实际上选择大于0.5的α值),这对于维持安全运行至关重要。当温度低于85°C时,算法则专注于最小化线长(实际上选择小于0.5的α值),因为此时没有理由为了降低温度而牺牲线长。

5)接受概率(AP)

是否接受邻近放置取决于接受概率(AP)公式(14)。 当前和邻域放置(这里应该是指扰动后重新计算得到的cost)的成本通过公式(12)计算,K是退火温度,从1衰减到0.01,衰减因子为0.95(我们使用这个值是因为它可以在25小时内完成每个实验,即4,500步)。如果邻近放置更好或相同(邻近成本≤当前成本),则AP值变为大于或等于1。如果邻近放置更差(邻近成本>当前成本),仍有一定的概率接受较差的邻近放置以避免陷入局部最小值。邻近放置越差,接受它的概率就越低。随着退火温度K的衰减,由于接受较差邻近放置的概率降低,解逐渐收敛。

四、实验

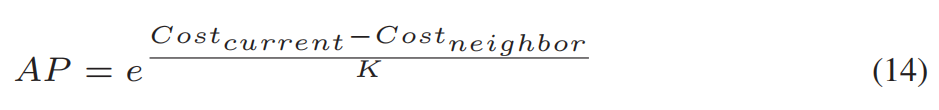

我们评估的异构2.5D系统的逻辑网络拓扑如图3所示。我们使用公开数据来确定芯片模块的尺寸和功耗(见表II)。我们的评估使用45毫米×45毫米的中介层。当然,对于更小的系统,这个中介层尺寸会更小。由于SA是一种概率方法,我们运行算法5次并选择最佳解决方案。我们将我们的TAP-2.5D与陈等人开发的代表性先进紧凑布局方法[11](B*-tree和快速SA,称为Compact-2.5D)进行比较。

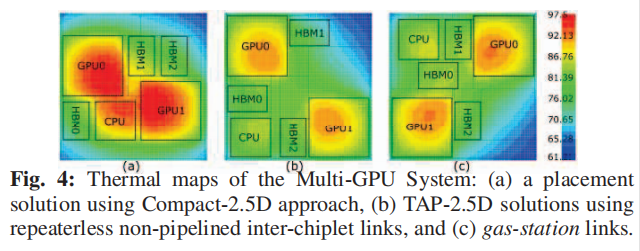

A.案例研究1:多GPU系统

图4(a)中的布局是通过Compact-2.5D方法获得的,该方法最小化了布线长度和面积,但未考虑温度因素。该系统在95.31°C下运行,总布线长度(所有芯片间链接长度之和)为88,059毫米。

图4(b)是我们使用TAP-2.5D方法得到的输出,(公式8)该方法采用无中继非流水线式芯片间链接的物理网络布局。这种布局的峰值温度较低,为91.25°C,总布线长度更长,达到96,906毫米,因为高功耗CPU和GPU芯片被推到了角落。

图4(c)是我们的气体站链接布局方案。系统的温度同样较低(91.52°C),但总布线长度减少到51,010毫米(而Compact-2.5D方法得到的总布线长度为88,059毫米)(公式9)。这是通过将HBM放置在CPU和GPU芯片之间的中央实现的,其中HBM芯片提供“气体站”,用于连接CPU和GPU芯片。

中介层尺寸的影响:在本案例研究中,我们使用了45毫米×45毫米的中介层,因为可以在该区域内容纳所有芯片。当我们把中介层尺寸增加到50毫米×50毫米并应用我们的方法时,虽然温度降低,但线长变长。

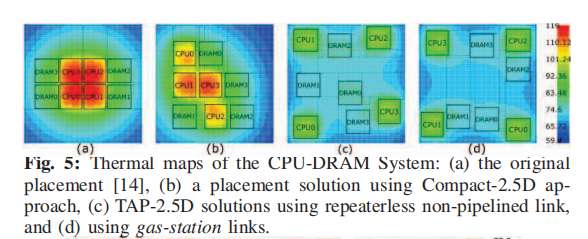

B.案例研究2:CPU-DRAM系统

图5展示了CPU-DRAM系统的热图,其中(a)是原始布局[14],(b)是使用Compact-2.5D方法的布局解决方案,(c)和(d)分别是我们的热感知布局方案,分别采用无中继非流水线芯片间链接和气体站链接。

从布线角度来看,原始布局(a)是最优的(根据我们的评估,总线长为67,686毫米)。然而,我们的热点模拟显示系统运行温度达到115.94°C,这在热学上是不可行的。

(b)中的布局也相对紧凑(总线长为100,864毫米),因此,最高温度达到113.54°C,这在热性能上是不可行的。

我们在(c)和(d)中采用的热管理布局方案成功地将最高温度分别降低到94.89°C和93.89°C。这是通过将高功耗CPU芯片推至中介层的角落实现的。

(c)和(d)的总线长分别为216,064毫米和138,956毫米。需要注意的是,我们并不是为了降低温度而牺牲2×到3×更长的线长(与原始方案(a)相比),这是我们为了将一个热不可行的设计转变为热可行设计所必须付出的代价。

对TDP的影响:由于温度降低,较长导线长度的性能损失可以通过增加的热设计功率(TDP)预算来恢复。在芯片封装中,所有芯片(chiplets)的

最高温度不得超过85°C,否则可能引发可靠性问题(如电子迁移、性能下降或寿命缩短),指在不超过温度限制(如85°C)的前提下,芯片或芯片组(如CPU+DRAM)能够长期稳定运行的

最大总功耗。在2.5D/3D封装中,温度是首要约束,需通过布局分散高功耗芯片。

若应用对延迟敏感(如HPC),需平衡布局分散度与性能损失。增加线长意味着增加延迟,TDP提升后,可通过提高运行频率(如+30%)抵消延迟损失,且无需增加散热成本。

原始系统(图5a)的TDP为400W(即所有芯片总功耗≤400W时,温度≤85°C),优化后的系统(图5c)通过热感知布局(TAP-2.5D方法)将TDP提升至550W。

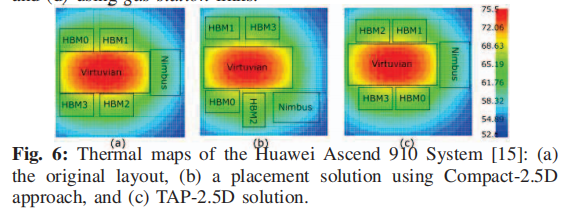

C.案例研究3

华为Ascend 910系统图6显示了现有华为Ascend 910系统[15]的热图。Ascend 910系统的原始布局(图6(a))已经实现了最小线长,并且在标称频率下运行时是热安全的。根据我们的模拟,Ascend 910系统的峰值温度为75.48°C,低于典型的可接受阈值85°C,总线长为16,426毫米。图6(b)是我们使用该方法生成的一种布局方案。

Compact-2.5D方法专注于减少布线长度和面积。该设计在(b)中的总布线长度为23,794毫米,温度为75.13°C。我们将其作为TAP-2.5D的初始布局。

图6(c)是使用TAP-2.5D方法对系统进行的布局(无论是否使用气体站链接,结果相同)。该布局的总布线长度为16,597毫米,温度为75.47°C。实际上,我们的开源布局解决方案与商用芯片的实际解决方案相当。

D.可扩展性讨论

我们方法的瓶颈在于热分析(每次HotSpot模拟平均耗时23秒)和布线优化(每次MILP操作平均耗时5秒)。热评估时间与芯片单元数量无关,因为我们使用固定的网格尺寸(64×64)来构建系统。布线优化所需的时间随O(|C| 2·|P| 2·|N|)增长,其中|C|、|P|、|N|分别是芯片单元数量、每个芯片单元的引脚簇数量以及芯片单元间的通道数量。作为未来工作的部分,我们将探索使用机器学习技术加速热分析和布线优化。

五、结论

我们的方法旨在通过联合最小化整个系统的运行温度和总芯片间网络线长来找到芯片间网络的物理设计方案。我们的方法策略性地在芯片之间插入间距以提高散热效果,从而增加整个系统的热设计功率。我们开发了一种基于模拟退火的方法,该方法搜索具有热感知性的芯片布局,并优化异构芯片间线路的布线。

![]()

![]() ,通常由引脚l的凸点决定。

,通常由引脚l的凸点决定。![]()

![]()

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?