在linux中采用,之前也会有cache相关问题,但和dma共用时,可能是采用了已经封装好的接口,导致感知不全。此次在裸板调试中,感受更加明确。特此记录。

在裸板上,cpu 的地址空间管理全部由自己划分。哪段地址配置为cache,哪段不配置等。默认情况下,映射到DDR的地址都没有cache。

在dma和cpu core会 访问同一段内存空间时,就引出此问题。而linux分配内存供CPU使用的相关接口中,已经对地址是否cache做了配置。

1) 对地址的cache属性设置通常都可以分段的,即地址段A 可以cache,而地址段B不可以cache.

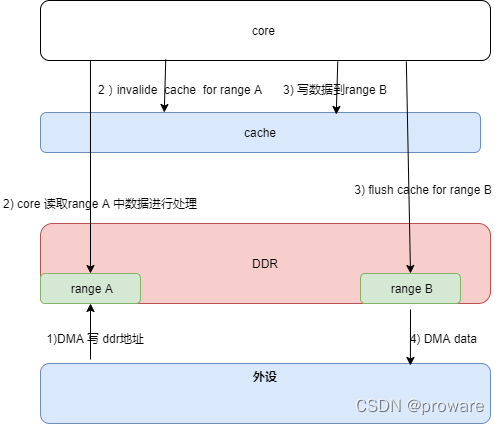

2) 对cache的操作,包括flush和invalide 两个。分别用在读写两个方面。功能示例如图,

当针对DDR range A和range B的cache功能被使能后,core在接收数据时,要先invalidate当前cache中的数据,以免读到旧数据。

当然,如果range A 和range B设置为非cache,那么core在进行针对这两段内存的访问时,时延增加明显,不满足应用场景要求。

此外收集些相关资料:

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?