[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-9Jmb62D4-1651213462466)(https://upload-images.jianshu.io/upload_images/22932333-280668cb9df868c1.png?imageMogr2/auto-orient/strip%7CimageView2/2/w/1240)]

- 五大核心组成部分:

- **运算器:**顾名思义,主要进行计算,算术运算、逻辑运算等都由它来完成。

- **存储器:**这里存储器只是内存,不包括内存,用于存储数据、指令信息。实际就是我们计算机中内存(RAM)

- **控制器:**控制器是是所有设备的调度中心,系统的正常运行都是有它来调配。CPU包含控制器和运算器。

- **输入设备:**负责向计算机中输入数据,如鼠标、键盘等。

- **输出设备:**负责输出计算机指令执行后的数据,如显示器、打印机等。

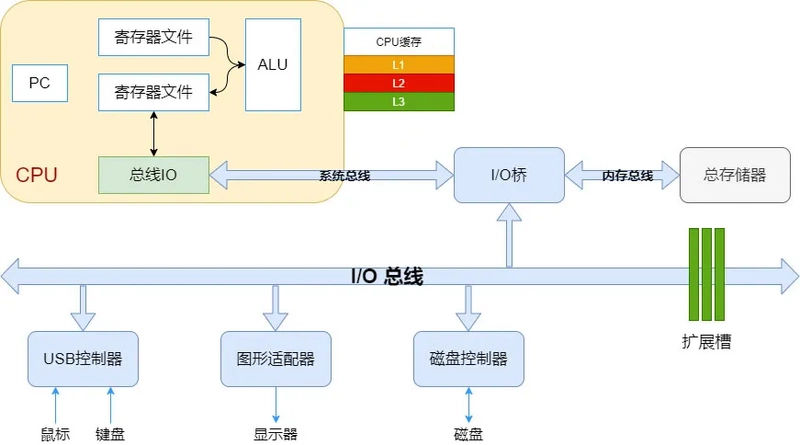

- 现代计算机硬件结构:

图中结构可以关注两个重点:

**I/O总线:**所有的输入输出设备都与I/O总线对接,保存我们的内存条、USB、显卡等等,就好比一条公路,所有的车都在上面行驶,但是毕竟容量有限,IO频繁或者数据较大时就会引起“堵车”

**CPU:**当CPU运行时最直接也最快的获取存储的是寄存器,然后会通过CPU缓存从L1->L2->L3寻找,如果缓存都没有则通过I/O总线到内存中获取,内存中获取到之后会依次刷入L3->L2->L1->寄存器中。现代计算机上我们CPU一般都是 1.xG、2.xG的赫兹,而我们内存的速度只有每秒几百M,所以为了为了不让内存拖后腿也为了尽量减少I/O总线的交互,才有了CPU缓存的存在,CPU型号的不同有的是两级缓存,有的是三级缓存,运行速度对比:寄存器 > L1 > L2 > L3 > 内存条。

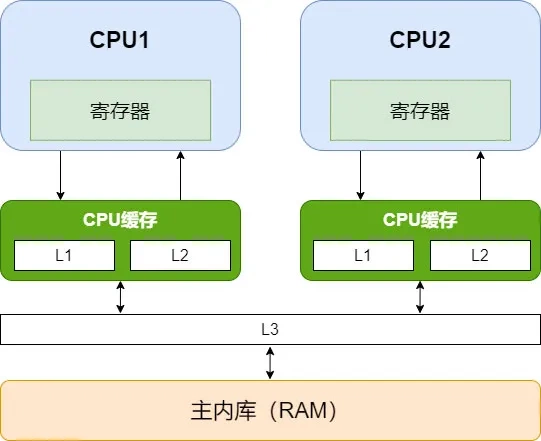

1.2 CPU多级缓存和内存

CPU缓存即高速缓冲存储器,是位于CPU与主内存之间容量很小但速度很高的存储器。CPU直接从内存中存取数据后会保存到缓存中,当CPU再次使用时可以直接从缓存中调取。如果有数据修改,也是先修改缓存中的数据,然后经过一段时间之后才会重新写回主内存中。

CPU缓存最小单元是缓存行(cache line),目前主流计算机的缓存行大小为64Byte,CPU缓存也会有LRU、Random等缓存淘汰策略。CPU的三级缓存为多个CPU共享的。

- CPU读取数据时的流程:

(1)先读取寄存器的值,如果存在则直接读取

(2)再读取L1,如果存在则先把cache行锁住,把数据读取出来,然后解锁

(3)如果L1没有则读取L2,如果存在则先将L2中的cache行加锁,然后将数据拷贝到L1,再执行读L1的过程,最后解锁

(4)如果L2没有则读取L3,同上先加锁,再往上层依次拷贝、加锁,读取到之后依次解锁

(5)如果L3也没有数据则通知内存控制器占用总线带宽,通知内存加锁,发起内存读请求,等待回应,回应数据保存到L3(如果没有就到L2),再从L3/2到L1,再从L1到CPU,之后解除总线锁定。

- 缓存一致性问题:

在多处理器系统中,每个处理器都有自己的缓存,于是也引入了新的问题:缓存一致性。当多个处理器的运算任务都涉及同一块主内存区域时,将可能导致各自的缓存数据不一致的情况。为了解决一致性的问题,需要各个处理器访问缓存时都遵循一些协议,在读写时要根据协议来进行操作,这类协议有MSI、M

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

729

729

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?