一、简要描述

TAS6511-Q1是一款单声道数字输入D类音频放大器,支持2 MHz开关频率,可实现成本和尺寸优化的单声道解决方案。该芯片的工作电压范围为4.5V至18V,可提供高达30W(14.4V,4Ω,10%失真率)和50W(14.4V,2Ω,10%失真率)的功率。该芯片还集成了直流和交流负载诊断,以在启用输出级之前确定连接负载的状态。

芯片可监测输出电流、PVDD电压、和芯片温度,并可通过TDM或I2S报告给主控。芯片通过内部集成的DSP,可以提供低延迟路径,对时间敏感的主动噪声消除(ANC:Active Noise Cancellation)和道路噪声消除(RNC:Road Noise Cancellation)处理速度提供了70%。

芯片封装相关信息如下:

推荐应用场景:

-

虚拟发动机声音系统

-

ecall

二、主要特征

-

满足AEC-Q100,环境温度范围–40°C to +125°C

-

宽电压输入4.5V~18V

-

I/O支持1.8V和3.3V

-

8个I2C地址可选

-

14.4V时空闲损耗<0.5W,关机状态,PVDD电流<5uA

-

实时负载诊断

-

内部集成DSP处理器

-

直流和交流负载诊断

-

支持I2S和TDM音频输入

-

音频采样率支持16、32、44.1~48、88.2~96和192KHz;

-

支持最大7A输出电流的音频输出

-

性能优越,109dB的信噪比以及1W输出是失真率<0.01%

-

提供各种保护

-

支持扩频技术,轻松满足CISPR25-L5 EMC规范

三、管脚定义

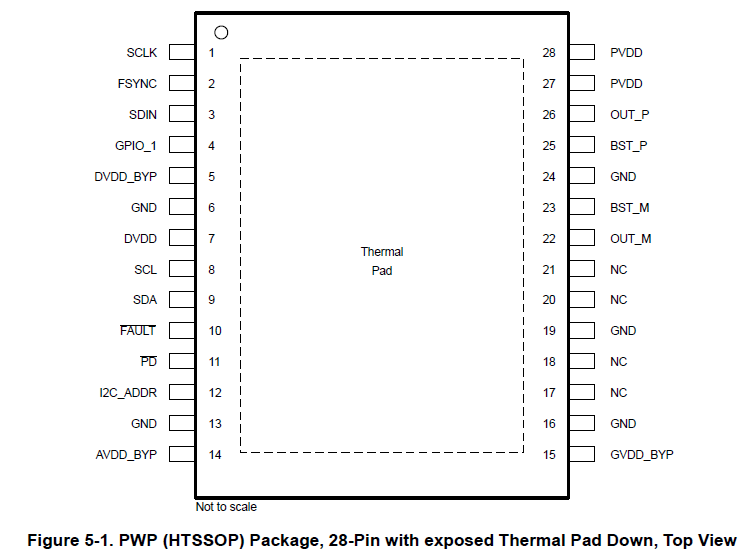

封装图如下:

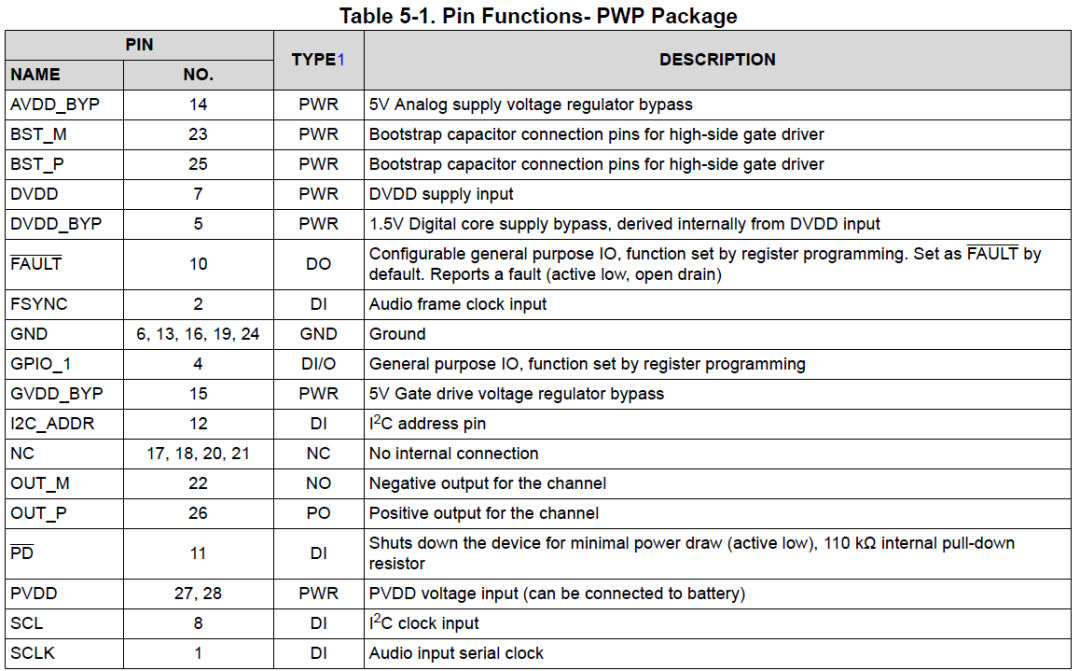

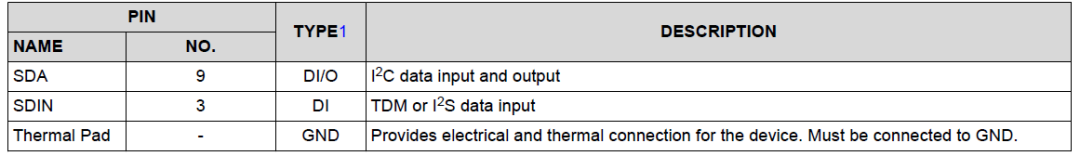

管脚详细定义如下:

四、芯片规范

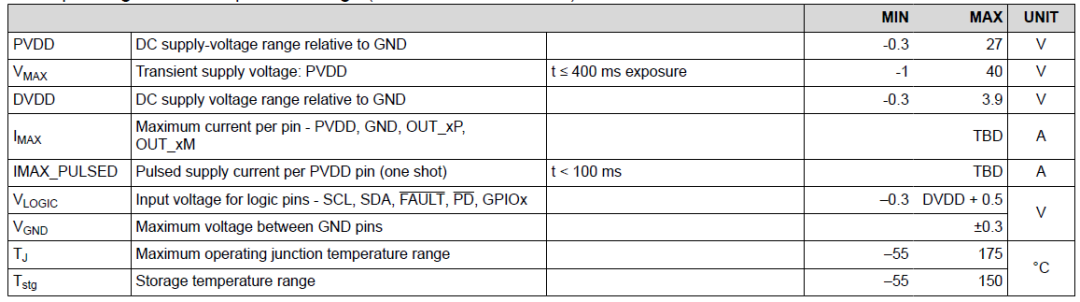

1.绝对最大范围

超过最大给到范围可能导致芯片损坏。超过建议范围但在最大范围之内,不能保证全部功能,同时也会影响芯片的可靠性和性能,并减少芯片寿命。

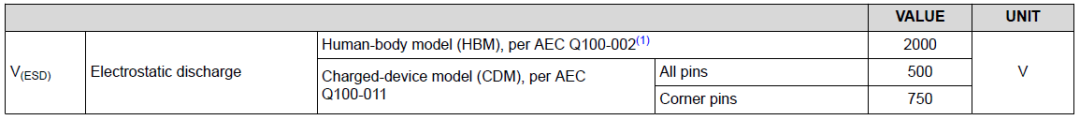

2.ESD信息

3.建议工作范围

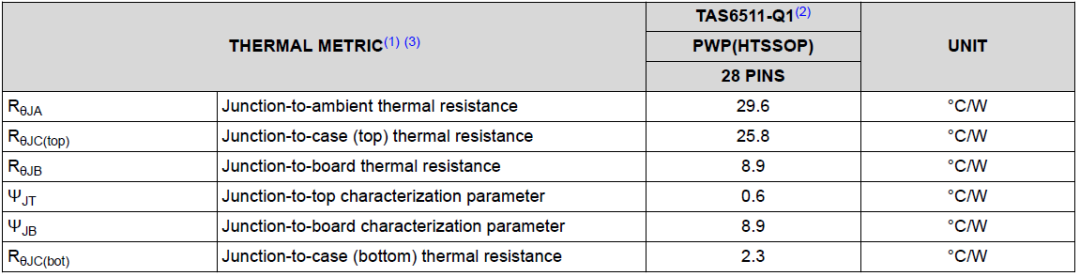

4.热阻

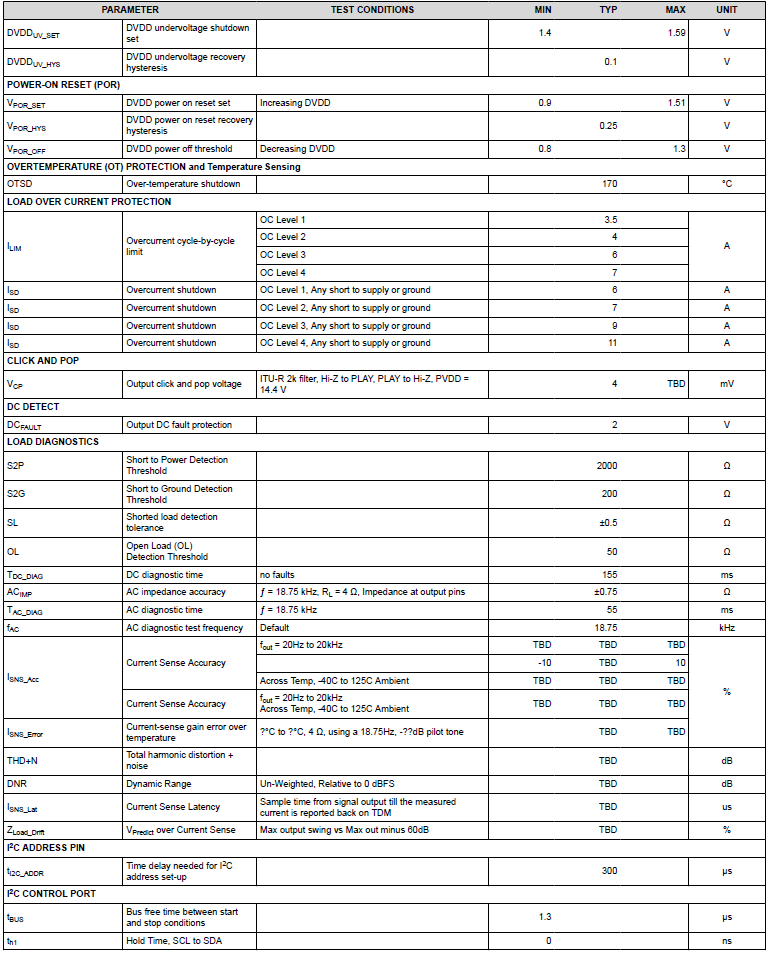

5.电气特性

测试条件:Tc=25℃,PVDD=14.4V,DVDD=1.8V,RL=4Ω,Pout=1W,fout=1KHz,Fsw=2.1MHz

五、详细描述

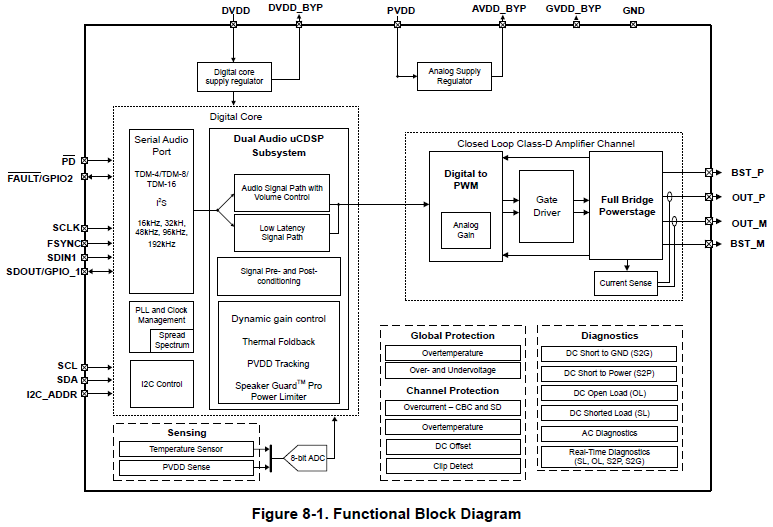

本芯片专为汽车行业设计,具有高效的D类技术,减少功耗、减少PCB面积、减少发热。同时芯片具有高保真的音频设计,具有更小尺寸、更低重量的优势。其功能框图如下:

1.电源

芯片有两个电源输入管脚,分别是PVDD和DVDD。其中DVDD可以是1.8V或者3.3V,主要给数字电路供电。PVDD电压比较高,主要给模拟电路供电。

芯片内部集成了调压器,可以产生不同的电压提供给内部电路,只需要外部对应管脚连接旁路电容即可。

当符合绝对最大范围参数时,芯片可允许偶然的电源或地开路。一般在喇叭信号线和地短路时,会导致地开路现象,此时FET的二极管提供第二地路径。

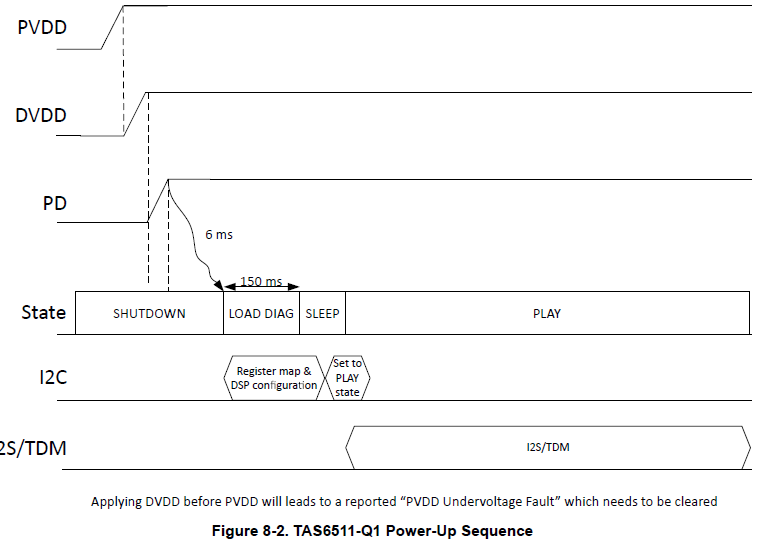

1)上电时序

首先电源先上电,然后PD管脚开始拉高(初始化数字和模拟电路),大概持续6ms左右。需要注意是建议PVDD先于DVDD供电,否则的话会有PVDD欠压报错,需要上电完成后清空Power_Fault_Mem寄存器。

在上电完成后的任意时间,如有电源错误上报,则芯片会进入到自动恢复状态(AUTOREC),直到电源错误被清除。

2)快速启动时序

部分场景可能需要从关机模式快速播放音频,这需要关闭DC负载诊断功能。时序是首先拉高PD管脚,等待1ms,设置寄存器关闭DC负载诊断,然后配置DSP和寄存器设置,最后通过设置寄存器进入播放状态。

3)下电时序

首先拉低PD管脚电平至少10ms,然后关闭PVDD和DVDD供电。建议首先关闭PVDD供电。

4)初始化和上电复位(POR)

当PD管脚拉高或者DVDD下降到POR阈值然后再恢复正常后,芯片则马上进行初始化操作。

初始化期间要把所有I2C寄存器设置成默认值,然后读取I2C_ADDR管脚信号来重新配置地址。初始化完成后,Power_Fault_Mem寄存器(Address = 0x86)的bit 4记录POR的次数,读取这个寄存器的值会重置报错信号。

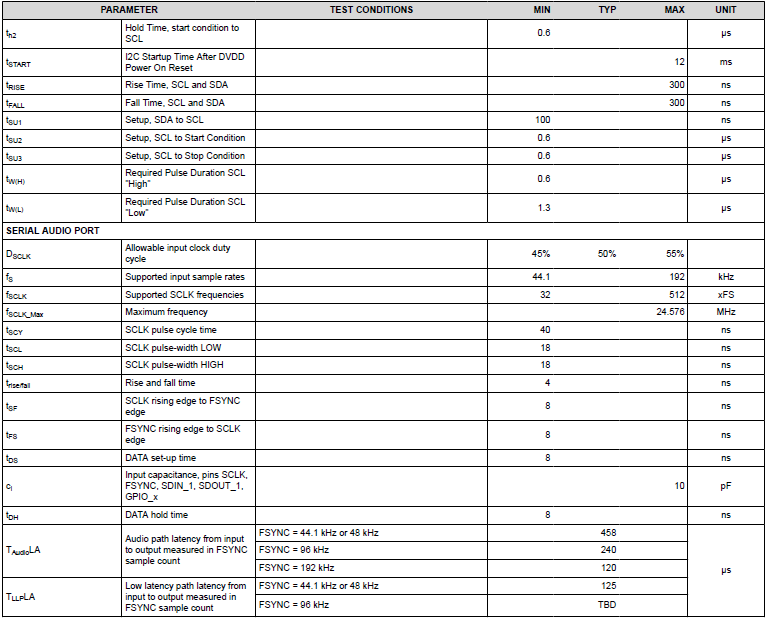

2.串行音频接口

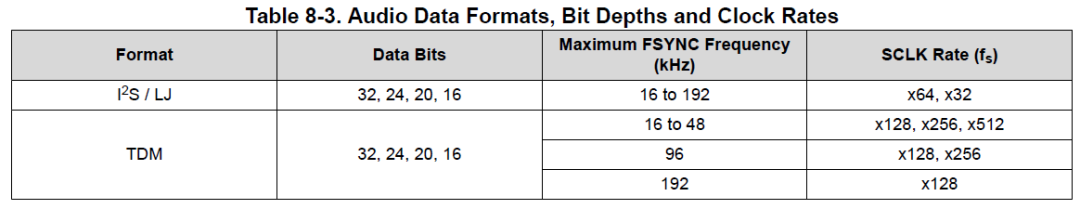

串行音频接口可以接收I2S、左对齐、DSP及TDM数据格式,另外DM信号最高支持TDM16。

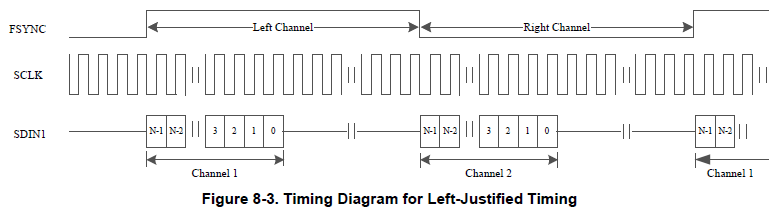

1)左对齐时序

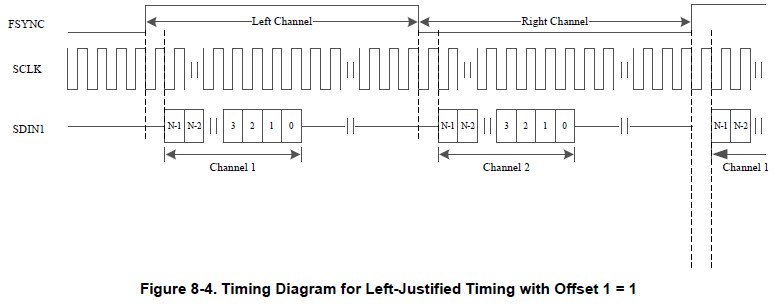

左对齐就是指FSYNC同步信号上升沿传输的左声道最高位MSB,下降沿传输右声道最高位MSB。芯片播放左声道还是右声道,可以通过寄存器ASI_CTRL2的bit4和5配置。

左对齐工作过程,首先在ASI_CTRL1寄存器(0x21)的bit2-3设置数据格式为LTJ模式(左对齐模式),然后在ASI_CTRL3寄存器 (0x23)的bit2-3设置数据长度,在ASI_CTRL7寄存器(0x27)和 ASI_CTRL8寄存器(0x28)的bit6-7配置可选的10bit偏移量(对所有通道生效)。

2)I2S模式

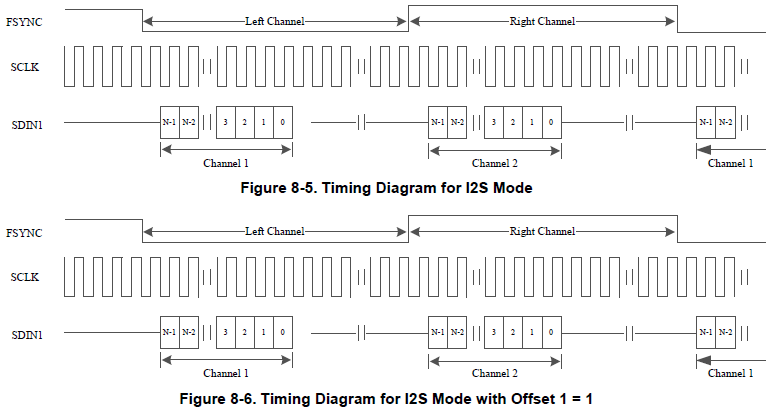

I2S模式也是通过FSYNC同步管脚定义左右声道。其中在FSYNC下降沿后的SCLK第二个上升沿采样的是左声道最高位MSB,同样FSYNC上升沿后第二个SCLK上升沿对应的是右声道最高位MSB。播放左声道或右声道也是由寄存器SI_CTRL2的bit4和5配置。

首先在ASI_CTRL1 Register (Address = 0x21)的bit2-3配置为I2S格式,然后通过ASI_CTRL3 Register (Address = 0x23)的bit2-3设置数据长度,ASI_CTRL7 Register (Address = 0x27)和ASI_CTRL8 Register (Address = 0x28)的bit6-7配置可选的10bit偏移量。

3)DSP模式

DSP模式下FSYNC信号定义音频数据的起始,不用来区分通道。FSYNC的上升沿开始传输左声道然后传输右声道数据。同样也是SCLK上升沿采样。

DSP模式工作过程,首先通过ASI_CTRL1 Register (Address = 0x21)的bit2-3设置为DSP模式,其次通过ASI_CTRL3 Register (Address = 0x23)的bit2-3设置通道1和通道2的数据长度,然后ASI_CTRL7 Register (Address = 0x27)和ASI_CTRL8 Register(Address = 0x28)的bit6-7配置偏移1的值。另外,如果FSYNC脉冲时长短于8倍的SCLK,需要设置ASI_CTRL8 Register (Address = 0x28) bit 0-1 为"01"。

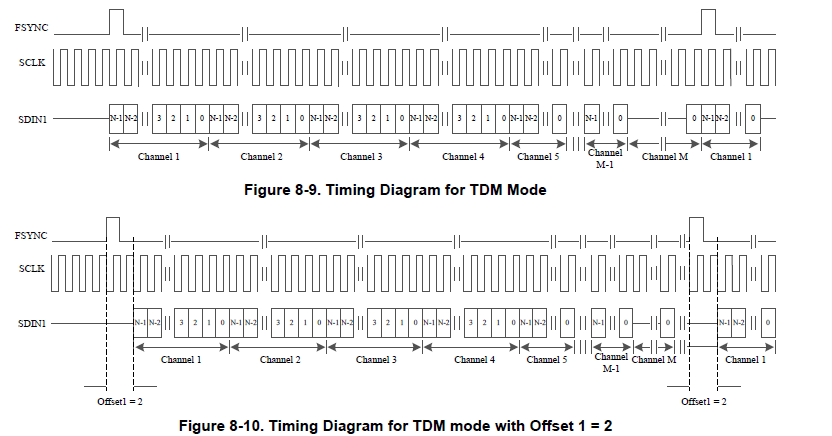

4)TDM模式

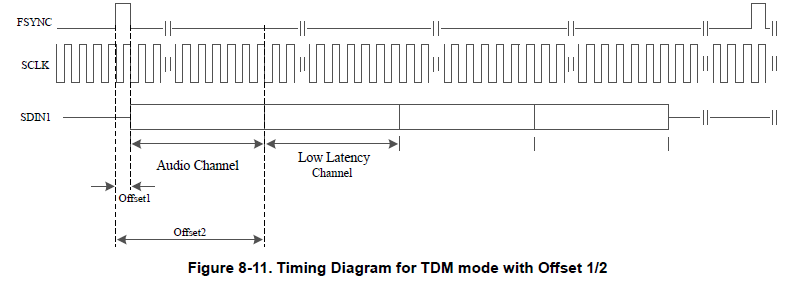

TDM模式支持4、8和16通道,数据输入管脚是SDIN。数据格式和DSP模式一致。TDM还可以传输低延迟信号(默认关闭,需配置ASI_CTRL18 Register)

工作工程,首先设置ASI_CTRL1 Register (Address = 0x21)的bit2-3为DSP模式,其次添加一个10bit偏移量防止数据重叠,所有不用的数据都放在TDM帧外:

-

音频通道:ASI_CTRL7寄存器(Address = 0x27)bit6-7设置高位MSB偏移,ASI_CTRL8寄存器(Address = 0x28)配置最低位LSB偏移量。默认偏移为0。

-

低延迟通道:ASI_CTRL7寄存器(Address = 0x27)bit4-5设置高位MSB偏移,ASI_CTRL8寄存器(Address = 0x28)配置最低位LSB偏移量。如果偏移为0,则低延迟数据紧跟着音频数据传输,如果偏移值大于0,则低延迟数据从帧起始位开始偏移该数值位数。

当如果FSYNC脉冲时长短于8倍的SCLK,需要设置ASI_CTRL8 Register (Address = 0x28) bit 0-1 为"01"。

5)SDOUT

SDOUT可以在I2S或TDM模式做为数据输出,左对齐和DSP模式不支持。DOUT可以输出以下数据:

-

通道感测电流;

-

输出电压约数,仅在采样率48KHz时支持;

-

温度数据,8bit的内部集成的温度传感器数据

-

PVDD电压,也是8为只读数据;

6)时钟

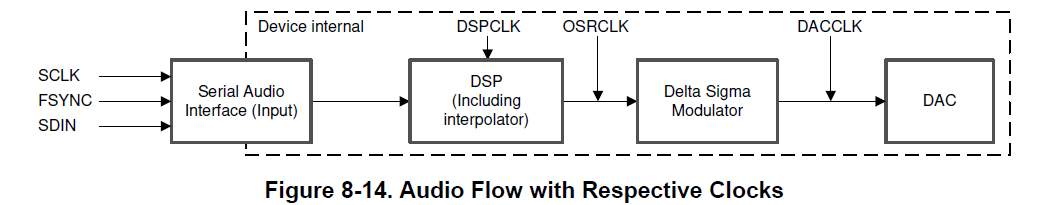

芯片需要多种频率的时钟,他们都是来自于串行音频接口输入。如下:

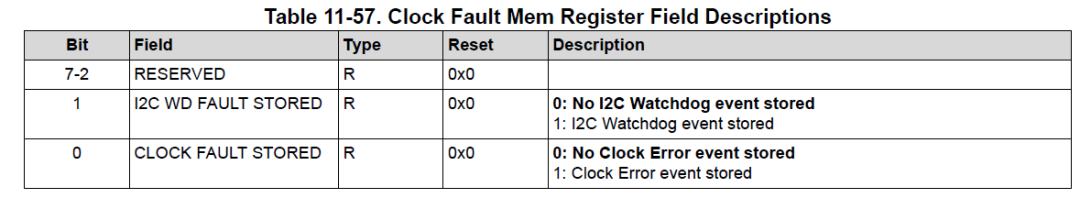

芯片会检测SCLK和FSYNC的关系,如不符合要求则会报错,具体是在Clock Fault Mem Register (Address = 0x8A)的bit0。

当时钟停止时,寄存器Clock Fault Mem的bit0置1。芯片在播放完最后一个正常数据后静音然后切换到高阻态(防止异响),如果时钟恢复,则自动切换到之前的状态。FSYNC切换采样率时(例如48KHz到96KHz),FSYNC和SCLK至少会终止30ms。

2766

2766

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?