1,ADS1220整体概述

ADS1220 是TI 公司的一款24位AD芯片,最大的优势就是位数高,但是调试时因为没有精密电源和精密参考信号,所以AD测出来的数据也一直很跳。其次就是内部集成了PGA,可编程增益放大器,最大可放大128倍,对于小信号的采集应该会很有帮助,但是我没用过。其次就是功耗低,用RIGOL DP832电源5V给PCB供电,PCB上面有AD芯片,还有两片稳压源REF5040,LM1117,大部分时间显示的电流都是0.01A,有些时候电流小到显示不出来。芯片只有四通道,可差分输入,采样率在Turbo模式下最大可达2KSPS,正常模式下最大只有1KSPS。另外这个芯片可采负电压信号。

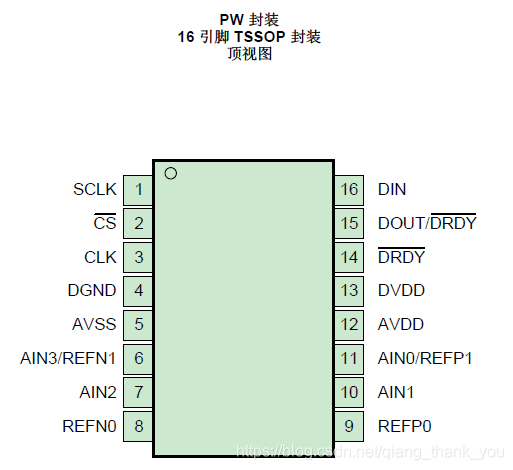

2,芯片的管脚图

整体还是很简单,四个采样输入管脚AIN0~AIN3,两个外部参考电压输入端REFN0、REFP0,模拟供电AVDD、AVSS,数字供电DVDD、DGND,外部时钟输入管脚CLK,SPI四线通信CS、DIN、DOUT、SCLK,以及一个 data ready信号引脚。

AIN0~AIN3就是模拟输入管脚,具体选择哪个脚需要配置芯片内部的寄存器,配置方式在datasheet上写的很清楚;

REFN0、REFP0是参考信号输入端,这款芯片内部有2.048V的参考信号,不过使用的时候好像发现这个参考信号不是很稳,所以最好外加一个参考信号,Datasheet上相关文档是REF50XX系列的基准电压芯片,也是TI 公司的。

模拟供电这里用的5V,数字供电用的3.3V。

这款芯片内部有4.096MHz的内部时钟,一般选择内部时钟就可以了,选择内部时钟时把CLK脚接地即可,若要用外部时钟,就把CLK接到外部时钟,新品在CLK脚检测到外部两个时钟沿后,就会禁用内部时钟,不用配置寄存器。

SPI四线通信CS、DIN、DOUT、SCLK,这四个脚就是用来写数据和读数据的,唯一一点就是,这款芯片都是在SCLK的下降沿写入或读出数据。

DRDY是数据就绪的信号,DRDY下降沿,表示数据可读出,然后可由FPGA给SCLK时钟信号读数据。DRDY会在下一个SCLK上升沿的时候变回高电平,不会影响下一个数据读取。

3,芯片其他特性

芯片输出数据频率:芯片输出数据频率可通过配置寄存器调整,其中正常模式下最大1000SPS, 占空比模式下最大250PS,TUEBO模式下最大2000SPS。另外,芯片工作模式还有掉电模式,该模式下功耗极低。

温度传感器:可配置寄存器TS位使能温度传感器模式。

上电复位:复位消耗时间约50us,这个比SCLK的周期1us大很多,使用的时候要注意。复位后默认为单次转换模式,

转换模式:单次模式和连续转换模式,可配置寄存器CM位进行选择。

SPI:空闲模式下SCLK应保持低电平。DOUT引脚也可作为DRDY信号输出端,可配置寄存器DRDYM位进行选择。SPI设置有超时功能,超时时串行接口会复位。

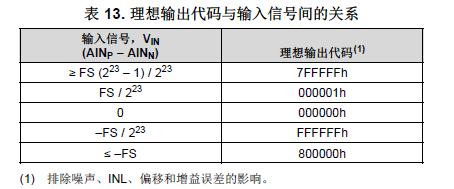

数据格式:

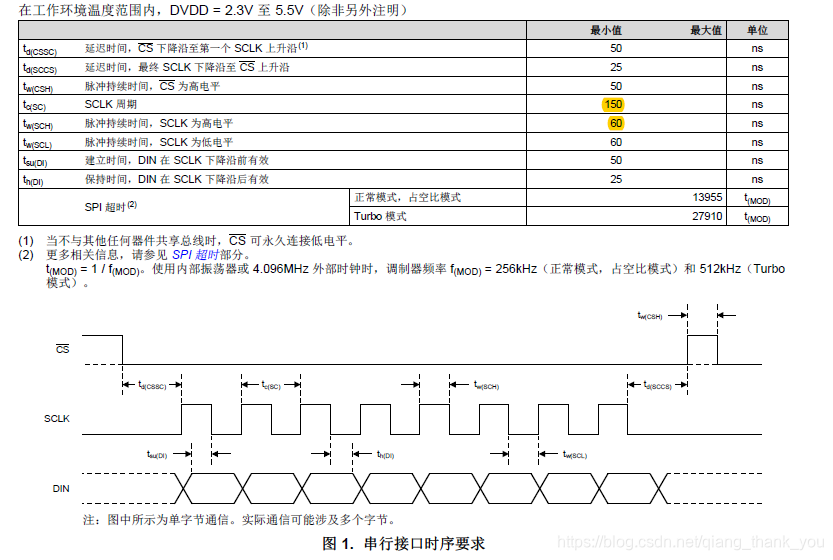

4,SPI时序要求

最长的一个时间,是SCLK的周期,为150ns,即最大频率为6.67MHz,其他时间都在这个允许范围内。我选择的是用1MHz的SCLK信号,其他信号都以1MHz为时钟,不会出现什么问题。

5,命令

一共有六种命令,都是8位的,可直接通过SPI写入芯片。

RESET,芯片复位命令;

START/SYNC,启动转换命令,连续模式下只发一次即可;

POWERDOWN:掉电工作模式时写入这个命令;

RDATA:将最新转换结果载入到输出移位寄存器;

RREG:读寄存器命令,(0010rrnn),rr为读取的起始寄存器位置,nn表示从起始寄存器位置读取(nn+1)个字节数;

WREG:写寄存器命令,(0100rrnn),从地址为rr的寄存器,开始写入(nn+1)个字节。

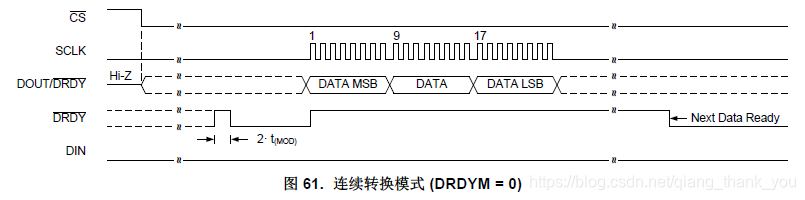

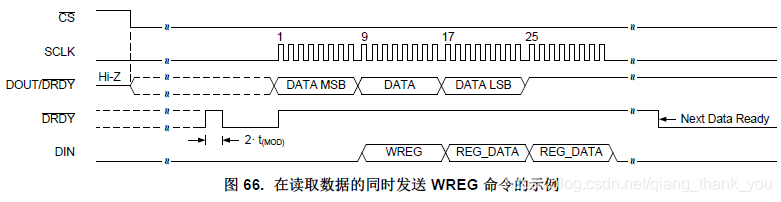

6,时序

读取数据的时序:

判断DRDY低电平到来,发送SCLK信号,从芯片连续读取24位数据。

7,寄存器配置

一共有四个寄存器,写寄存器之前,要发送WREG命令,并指示从哪个地址开始写,要写入几个寄存器。

寄存器的具体配置信息,参见Datasheet。

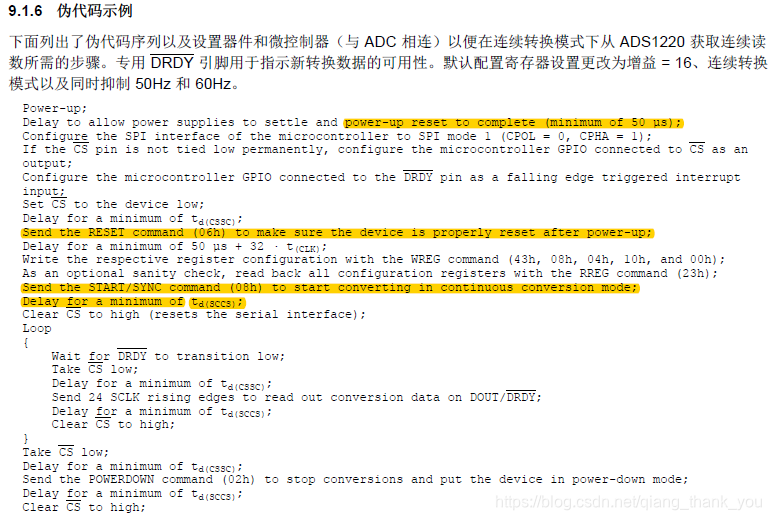

8,示例工作时序

最后附上Datasheet下载地址:http://www.ti.com/cn/lit/ds/symlink/ads1220.pdf

附上我写的代码:https://download.csdn.net/download/qiang_thank_you/11453866

本文详细介绍了TI公司的ADS1220,一款24位高精度AD芯片,涵盖其主要特点、管脚功能、工作模式、SPI通信与时序要求。深入探讨了芯片的配置方法及应用示例。

本文详细介绍了TI公司的ADS1220,一款24位高精度AD芯片,涵盖其主要特点、管脚功能、工作模式、SPI通信与时序要求。深入探讨了芯片的配置方法及应用示例。

1221

1221

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?