0.目录

文章目录

1.简介

本文介绍:Armv8-A的异常和特权模型。包括:ARM架构中的不同的异常,以及当处理器接收到异常之后的行为

本文将有助于:

- 底层编程开发,如boot或驱动

- 设置与管理异常

你将学会:

- 列出异常等级

- 阐述如何切换执行的异常等级

- 命名与描述执行状态

- 建立简单的AArch64异常向量与异常handler

2. 特权与异常等级

在我们解释Armv8-A异常模型的细节之前,让我们首先介绍特权的概念。现代软件希望被分成不同的模块,每个模块对系统和处理器资源有不同的访问级别。这方面的一个例子是操作系统内核和用户应用程序之间的分离,操作系统内核具有对系统资源的高级访问权限,而用户应用程序配置系统的能力则更有限。

Armv8-A通过实现不同级别的特权来实现这种分割。只有在在处理器接到异常或从异常返回时才能更改特权等级。因此,这些特权级别在Armv8-A体系结构中被称为异常级别。每个例外级别都有编号,级别越高的特权有越高的编号。

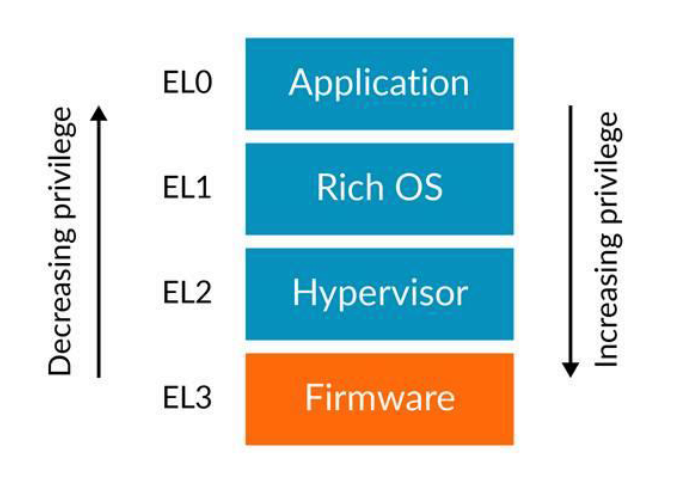

如下图所示,异常级别称为EL, x为0 ~ 3之间的数字。例如,最低级别的特权被称为EL0。

大多数应用代码运行在EL0,操作系统运行在EL1,hypervisor运行在EL2。EL3为底层固件和安全代码所保留。

注意:架构不强制要求这个软件模型,但是标准软件采用这种模式。

2.1 特权的类型

有两种与本主题相关的类型,第一种是存储系统中的特权,第二种是从访问处理器资源的视角出发的特权。这两种特权都受当前的异常等级影响。

2.2 存储特权

Armv8-A实现了虚拟存储系统。在这个系统中,MMU允许软件指定内存区域的属性。这些属性包括读写权限,可以用两个维度来进行配置。这种使得允许特权访问和非特权访问的权限得以分离。

发生在EL0的内存访问将对照非特权访问权限进行检查。相对的,EL1,EL2和EL3的访问将对照特权访问权限进行检查。

由于这种存储权限配置将用到MMU的转换表,所以在编程这些表格的时候需要考虑到这种特权。MMU的配置存储在系统寄存器中,访问这些寄存器的能力也由当前异常级别控制。

2.3 寄存器访问

一组系统寄存器存储了Armv8-A处理器的配置设置。系统寄存器的设置组合定义了当前处理器的上下文。对系统寄存器的访问由当前的异常等级决定。

系统寄存器的名称表示可以访问该寄存器的最低异常级别。例如,TTBR0_EL1是保存EL0和EL1使用的转换表的基址的寄存器。这个寄存器不能从EL0访问,如果硬要访问将导致一个异常。

Armv8-A架构有很多组功能相似的寄存器,其命名仅有后缀的异常等级不同。这些寄存器相互之间独立,在指令集中的编码不同,在硬件上单独实现。比如下面的寄存器,针对不同的转换阶段配置MMU。虽然名字相似,但是各自有各自的访问语义:

- SCTLR_EL1 – Top level system control for EL0 and EL1

- SCTLR_EL2 – Top level system control for EL2

- SCTLR_EL3 – Top level system control for EL3

注意:EL1和EL0共享MMU的配置,且只能由运行在EL1的代码进行控制。因此,没有SCTLR_EL0.

高级别可以访问低级别的寄存器。例如,切换上下文需要保存寄存器状态的时候

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?