文章目录

前言

这个系列文章主要用于本人的学习记录,可能相当长时间里只是协议的中文翻译,伴有少量个人总结,营养价值不高。有缘读到此文章的话,也建议读者结合英文原文进行理解。谢谢!

D1.1 Coherency overview 一致性概述

系统级一致性让系统部件共享内存,而无需进行软件缓存管理来保持cache间的一致性。如果两个系统部件对同一个内存位置的写操作能以同样的顺序被所有系统部件所观察到,那么该内存范围具有一致性。

ACE协议enables:

- Caches间数据共享保持正确性;

- 具有不同属性的组件交互;

- 缓存数据的最大化复用;

- 可以在高性能和低功耗间选择;

ACE协议提供了一个系统级一致性的框架。系统设计者可以决定:

- 具有一致性的内存范围;

- 实现一致性扩展的内存系统部件;

- 用于与系统部件交互的软件模型;

D1.1.1 ACE revisions

- Issue D第一次描述了AXI Coherency Extensions (ACE)

- Issue E

增加了ACE协议的说明(clarification)、建议(recommendation)和新功能(capability)。为了保持兼容性,使用property来声明新功能。 - Issue F增加了对ACE协议的扩展,包括了:

- ACE5

- ACE5-Lite

- ACE5-LiteDVM

- ACE5-LiteACP

对于低功耗接口的相关描述已经移除,该内容由AMBA Low Power Interface Specification (ARM IHI 0068)介绍。增加了新的附录用于总结transaction与signaling列表。

D1.1.2 Usage cases适用范围

ACE协议允许系统架构师为系统部件间的数据共享选择最合适的方式。本协议没有定义特定的适用情形,但典型的适用情形包括:

- 系统部件间的一致性连接;

- 具有non-uniform memory resources的子系统间的一致性连接;

- 具有高度优化局部一致性系统的部件的一致性连接;

- 一致性通信的过滤(?)The filtering of coherency communications;

- 支持不同一致性协议(如MESI/ESI/MEI/MOESI)的组件间的一致性连接;

- 包装原生不支持一致性的组件,使其能够在一个系统级一致性设计中被有效使用;

- 支持可能具有多级cache的组件与non-cached组件;

- 支持在不同粒度(如cache line粒度和large buffer粒度)存放一致性信息的组件;

- 有助于优化以下实现:

- 一个系统内的基本互联;

- 多个子系统。

D1.1.3 ACE terminology术语

A1-30介绍了AXI/ACE spec中通用的属于,且:

- 本规范不定义标准cache术语(在相关的caching文档中有)

- Glossary中定义了本规范使用的特殊名词。

ACE引入了额外的特殊名词,尤其是与caching、system master进行的memory operations。接下来的subsections总结了这些特殊名词。在适当的情况下,本节中列出的术语链接到相应的术语表定义。

-

AXI components and topology

- Caching master/manager, initiating master/manager and snooped master/manager;

- Downstream cache, Local cache, Peer cache, and Snooped cache;

- Main memory and Snoop filter.

-

Cache state terminology

- 见D1-153的cache state model,描述了一个cache entry的可能状态。

-

Actions and Permissions

- Load, speculative read, and Store;

- Permission to store and Permission to update main memory

-

Temporal descriptions

- AXI: In a timely manner, 事件按顺序发生

- ACE: At approximately the same time,从远处观察者的角度可能无法判断两个相近事件的发生顺序

D1.2 Protocol overview协议概述

D1.2.1 About the ACE protocol

ACE协议由AXI4协议扩展而来,并支持硬件一致性的caches。ACE通过如下方式实现:

- 具有5个状态的cache model来定义一致性系统中的任意cache line状态。Cache line状态决定了访问该cache line前需要采取什么行为。

- 向AXI4中已有的通道加入了额外的信号,使新的传输事务和信息传递给需要硬件一致性支持的位置。

- 相比AXI4增加了额外的通道,当其他master正在访问一个可能处于共享状态的地址时,支持与cached master的通信。

ACE协议还提供了:

- Barrier transaction来保证一个系统内的transaction ordering。*ACE5和ACE5-Lite的变体接口不支持Barrier transaction。

- 分布式虚拟内存(DVM)功能来管理虚拟内存。

D1.2.2 Coherency model一致性模型

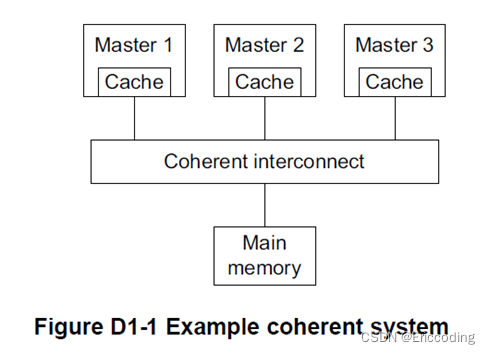

Figure D1-1展示了一个一致性系统的例子,包含了三个master组件,每个master都有一个本地cache。ACE协议允许内存中同一位置的cached copies存在于一个或多个master组件的本地cache中。

当对某一位置进行store操作时,ACE强制要求系统中仅存在一份copy,以保证所有masters都能观察到任意地址的正确数据。

【main memory的刷新】 没有必要每时每刻保持main memory中的数据是最新的,只需要在一份数据copy不再被任何cache持有之前写回即可。*虽无必要,但允许在有cached copies时刷新main memory。

ACE协议让master来决定如果一条cache line是某内存地址的唯一copy,或者存在同一地址的其他copies,因此:

• 如果一条cache line时唯一copy,该master可以修改cache line的值,而无需通知系统内的其他master。

• 如果一条cache line可能存在于其他cache中,该master必须使用恰当的transaction通知其他caches。

D1.2.3 cache state model

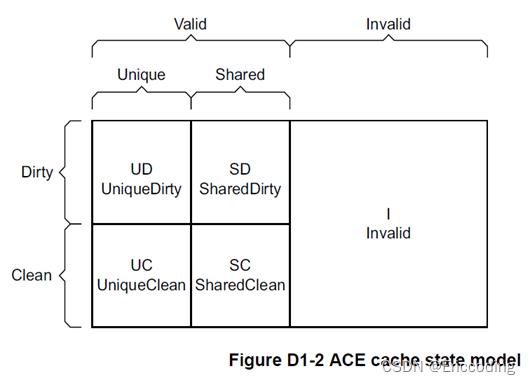

为了决定一个组件在访问一条cache line时需要采取的行为,ACE协议定义了cache states。每个cache state均基于该条cache line的特点。

Cache line一般有如下特点:

-

Valid或Invalid,valid态表示该条cache line处于cache中,invalid态表示该条cache line不处于cache中。

-

Unique或shared, unique态表示该条cache line仅存在于一个cache中,shared态表示该条cache line可能存在于多于一个cache中(not guaranteed)。

-

Clean或dirty, clean态表示该cache没有责任(responsibility)更新main memory,dirty态表示相比main memory该条cache line发生了修改,而这个cache必须保证最终更新main memory(具有更新main memory的责任)。

Figure D1-2展示了ACE的五态cache model。Table D1-2提供了每种状态的更多信息。 -

Invalid(I): 该cache line不存在于这个cache中。

-

UniqueClean (UC): 该cache line只被这个cache持有且相比main memory没有被修改;该组件可以对该cache line进行store操作,而无需通知其他caches。

-

UniqueDirty (UD): 该cache line只被这个cache持有;相比main memory进行过修改,这个cache该修改最终要通知main memory;该组件可以对cache line进行stores操作而无需通知其他caches。

-

SharedClean (SC): 该cache line可能存在于其他cache;该cache line相比main memory是否进行过修改不可知,该组件也无义务更新memory;该组件必须在对该cache line进行store操作前通知其他caches。

-

SharedDirty (SD): 该cache line可能存在于其他cache;相比main memory进行过修改,这个cache该修改最终要通知main memory;该组件必须在对该cache line进行store操作前通知其他caches。

Cache state规则:

- Unique态的cache line只能被一个cache持有。

- 被多个cache所持有的cache line,在每个cache中的状态都必须是Shared。

- 当一个cache获取了一条新cache line,而其他cache也持有该cache line的copy且可能处于Unique态,那么必须通知其将其持有的line改为Shared态。

- 当一个cache丢弃一条cache line,无需通知其他持有该cache line的caches。这个要求意味着:Shared态的cache line也可能只被一个cache所持有。

- 当一条cache line相比main memory被修改过,必须在该cache中处于dirty状态。

- 当一条cache line相比main memory被修改过且被多于一个cache所持有,那么dirty态只存在于一个cache中。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?