前言

我自己做的答案,仅供参考,欢迎指正。

建议手写,助教可能给分更高。

第一题

特点对比:

①指令长度:A64和A32指令固定为32位,T16指令固定为16位,T32指令集混合使用32位和16位指令。

②地址长度:A32和T32适合32位内存总线,T16适合16位内存总线,A64适合64位内存总线。

③代码量:以A32为基准,T16代码压缩30%~40%,T32代码体积减少26%。

④处理性能:A64性能高于A32,T16性能高于A32,T32性能高于Tl6。

当使用32位的存储器时,A32指令集会快于T16指专集。并且A32指令会比T16更复杂,因此某些操作在A32中可以用单个指令完成,而在T16中要用多个指令完成。例如将寄存器值移动到另一个寄存器:

A32中指令为 MOV R1,R2 ,一条指令即可完成。

T16中指令为 LDR R1,=R2

LDR RI,[RI],需要使用两条指令。

第二题

优势和特点:

①采用不同的核心满足不同的功耗和性能需求,可以在不同负载下实现性能与能效的最佳平衡。其中超大核提供高性能,大核提供中等性能,小核以低性能处理日常任务。

②操作系统可以根据任务的需求,灵活地将任务分配给最合适的核心,高效利用处理器资源。

③并行处理多个任务时,操作系统可将任务分配给不同的、合适的核心,提高计算效率。

实例:快手的LaoFe NDP架构就是一种"超大核+大核+小核"的架构。其中英特尔® FPGA作为超大核处理并行度高、延迟敏感的任务:英特尔®至强®可扩展处理器作为大核,处理复杂的计算任务;英特尔®傲腾

(忽略.)持久内存作为小核,提供快速的数据存储和访问。这种架构使得快手的参数服务器吞吐性能提升了5-6倍,整体请求延时降低了70%-80%,同时成本更低。通过这个实例可以看出该架构大幅提升了处理器性能和能耗比。

第三题

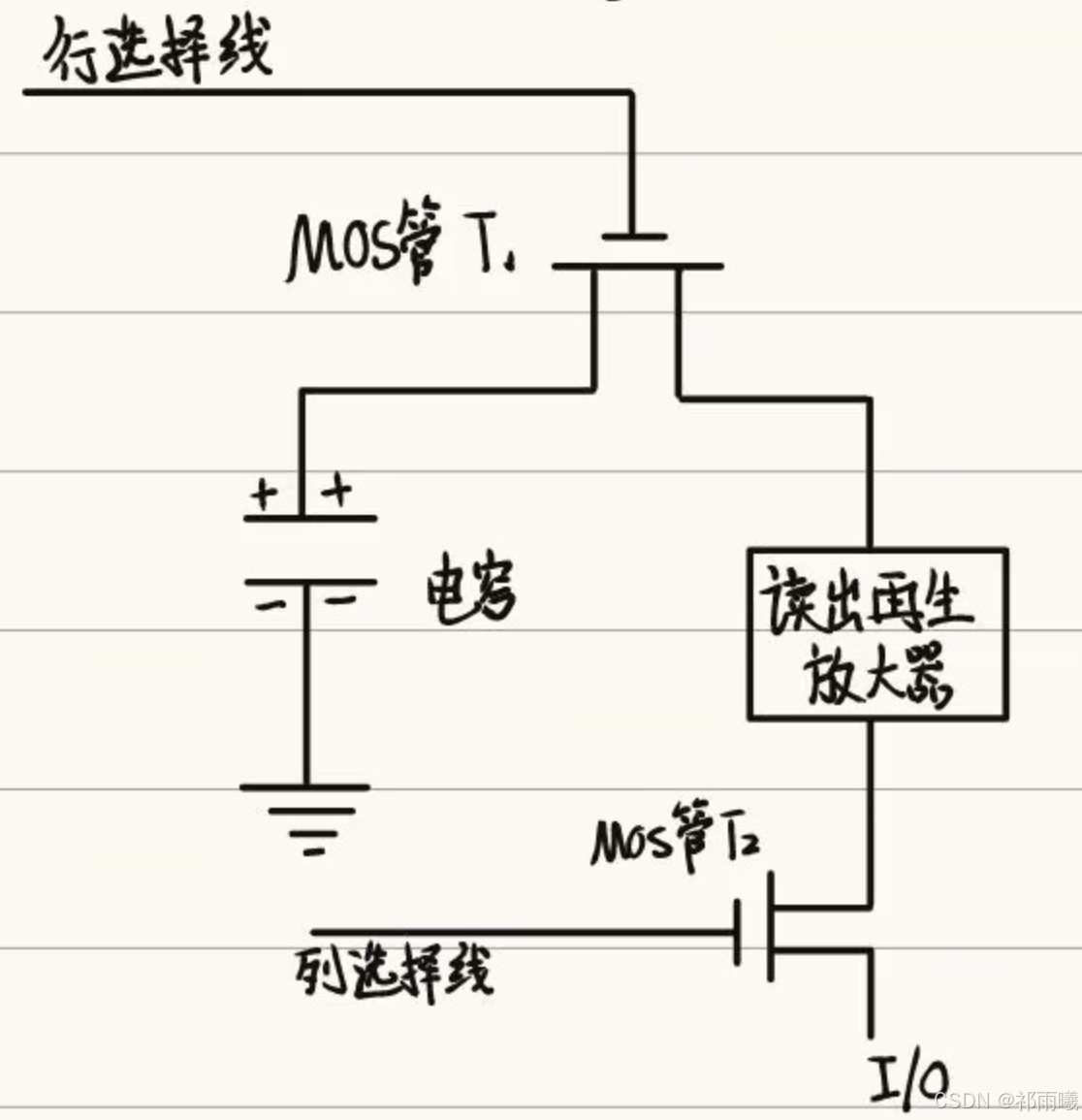

(1)DRAM存储单元:

工作过程:

① 写操作:行、列选择线为高电平,两个MOS管导通,数据从I/O引脚输入。写入1时,I/O引脚为高电平,电容充电;写入0时,I/O引脚为低电平,电容放电。

② 读操作:行、列选择线为高电平,两个MOS管导通,数据从I/O引脚输出。当电容没电时,读出0;当电容有电时,电荷经再生放大器放大,从I/O引脚读出1。

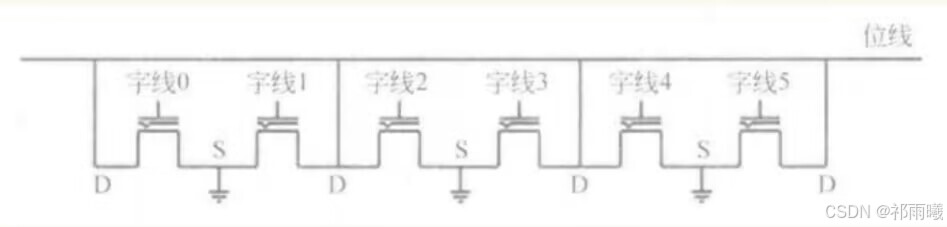

(2)NOR Flash:

架构特点:内部存储单元以平行方式连接到位线。

工作过程:

① 写入数据0:给控制栅加高电压、源极不接电压。

② 擦除(写入1):源极接高电压而漏极、控制栅浮空。

③ 读取:控制栅施加小电压或不施加电压,源极接地,漏极接位线。当浮栅有电子时,电流小,读出0;没有电子时,电流大,读出1。

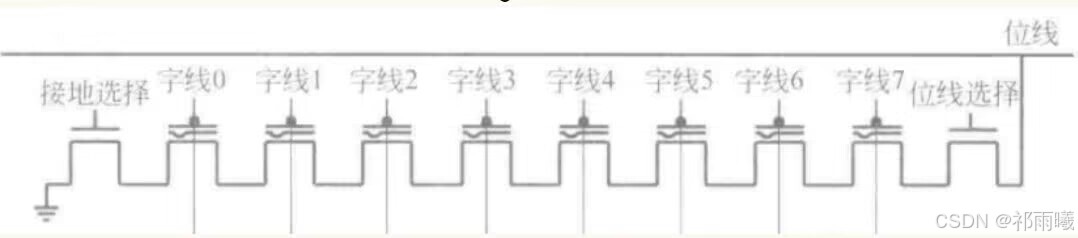

NAND Flash:

架构特点:使用复杂I/O接口串行存取数据,共用一套总线作为地址总线和数据总线。

工作过程:

① 写入0:控制栅加偏置电压、源、漏、衬底全部接地。

② 擦除:衬底施加高电压,源漏极浮空,控制栅接地。

③ 读取:被读取的晶体管的控制栅不加偏置电压,其他七个晶体管都加偏置电压导通。位线为低电平读出0,位线为高电平读出1。

NOR Flash有独立的地址线和数据线,读取和传输速度快,但擦除和写入速度较慢,所以比较适合存放代码等无需改动及可执行的内容。

NAND Flash具有更高的存储密度、更快的写入速度、更低的价格以及更好的擦写耐用性等优点,且地址传输开销大,因此适合存放大块数据。

(3)手机、平板中使用NAND Flash来存储操作系统、应用程序和用户数据。符合前一问中的Flash功能设定,即用于大量数据的存储。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?