目录

前言

本文对.do文件进行整理介绍,并在后文引用 “ bitrocco ” 的一篇博文做补充介绍。

经验之言:

事例:

1、SIM文件夹下:test_model.v是RTL代码(需要被仿真的文件),test_model_2019.v是备份的历史代码(不是想仿真的文件)。由于编译指令是编译SIM文件夹下的所有.v文件,从而若test_model_2019.v存在逻辑错误、而test_model.v中没有,则会导致一种现象,modelsim的波形与test_model.v逻辑描述不一样。该问题可能是由于test_model_2019.v文件影响导致,因为两个文件的模块名一致,从而导致modelsim编译文件的时候,使用了错误的文件。

2、ISE编译的仿真库与vivado编译的仿真库不通用;vivado编译的仿真库与Modelsim版本有关,若版本不匹配,会导致仿真库编译时个别IP 报错。

仿真

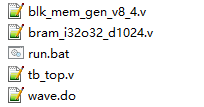

1、文件准备:将待仿真的 tb_top.v、被测文件.v、批处理文件.bat、wave.do文件准备好。

2、文件功能说明。

run.bat:批处理文件是将modelsim的工作路径切换到当前文件夹路径;之后运行wave.do。

wave.do:执行:创建本地库、将逻辑库名映射库路径、编译IP、编译RTL、添加仿真库等功能。

bram_i32o32_d1024.v:被仿真文件。由于这个Xilinx IP会调用blk_mem_gen_v8_4.v文件,因此需要将blk_mem_gen_v8_4.v也放在该文件夹中。

3、在以上文件准备好后,直接运行run.bat,即可实现自动打开modelsim对tb_top进行仿真。

备注:该仿真文件夹中不可以含有其他modelsim版本编译产生的work文件夹,否则会导致编译失败。也即在仿真文件夹中,只需要准备上面所需的文件,不要含有其他东西即可。

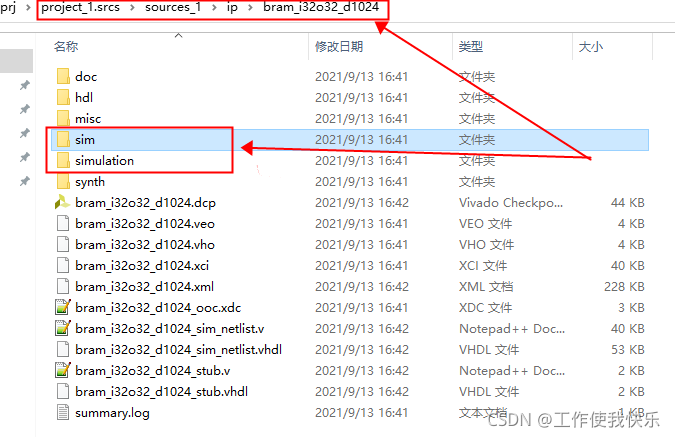

4、vivado软件在创建IP时,sim文件夹里存放的是IP仿真文件,simulation文件夹里放的是仿真model,有的IP会调用simulation中的文件用于行为仿真。

这里提供wave.do的参考示例。

#================================================================

# Clear

#================================================================

# 退出当前仿真

quit -sim

# 清输出窗口

.main clear

#================================================================

# Create work library

#================================================================

# It will create a "work" folder in current folder

# 创建本地库

vlib work

# 将逻辑库名映射库路径

vmap work work

#================================================================

# Compile Xilinx/Inter IP core

#================================================================

# Add File path and Compile them

vlog ./*.v

##================================================================

## Compile RTL

##================================================================

## 编译当前目录下的所有v文件

#vlog ./*.v

## 编译上一级目录下的所有v文件

#vlog ../*.V

#================================================================

# Start the emulator(启动仿真器)

#================================================================

#语法:优化部分参数(-voptargs=+acc),链接到默认的work 库;启动仿真顶层测试逻辑库(work)里面的tb_top文件

#方式一:Add ise_lib

#vsim -L xilinxcorelib -L simprim -L unimacro -L unisim -voptargs=+acc work.tb_top

#方式二:Add vivado_lib

#vsim -L secureip -L unisim -L unimacro -L unifast -L unisims_ver -L simprims_ver -voptargs=+acc work.tb_top

#方式三:Add quartus_lib

#vsim -novopt -t 1ps -c -L altera_lnsim_ver -L altera_mf_ver -L altera_ver -L cycloneii_ver -L lpm_ver -L sgate_ver -l ./log/report.log -wav ./wave/tb.wlf -voptargs=+acc work.TB

#================================================================

# Set the window types

#================================================================

view wave

view structure

view signals

#================================================================

# Add watch wave

# color : green cyan yellow pink violet orchid gray40

# radix : binary unsigned hexadecimal

# 建议:常量/寄存器的值波形使用gray40;数据总线cyan;FSM pink;控制信号yellow/pink;其他信号green

#================================================================

add wave -noupdate -color green -format Logic -radix unsigned -group {TOP} /tb_top/*

#================================================================

# run

#================================================================

.main clear

run 1us相关内容参考如下:

Modelsim指令介绍

| 指令 | 功能 |

| vlib work | 建库:在当前工作目录下建立一个 work 工作库 |

| vmap work work | 映射:将目前的逻辑工作库work和实际工作库work映射对应 |

| vlog "./*.v" | 编译:编译当前路径文件夹里的所有后缀为.v的文件 |

| vlog ../IP/*.V | 编译:编译上一级路径里IP文件夹下的所有后缀为.v的文件 |

| vlog -work work ./../design/*.v | 编译:"- work" 参数用来具体指定将 verilog 源代码编译到哪个库中,缺省编译到 work 库。 |

| vcom | 编译:编译 vhdl 源代码 |

| vsim tb_top | 启动仿真器 :(tb_top测试文件顶层) |

| vsim -常用参数 | -novopt :仿真优化选项 -t : 指定仿真的时间分辨率(缺省为 ns) -c :让 vism 工作在命令行模式 -l :输出 log 文件 -L :指定工作逻辑库 -wav :创建波形文件 -do :开始仿真后运行 tcl 脚本 work.** :指定仿真的 top module,“ ** ”需要指定tb顶层的文件名(非模块名) |

| run 1us | 运行仿真: |

| run 常用参数 | *<时间单位 > ; 指定运行时间 (run 1us) @<数量> ; 运行仿真到 "数量 "个单位时间 -all ; 指定一直运行仿真 -continue ; 继续已停止的仿真 |

| add wave | 添加信号到波形文件 |

| add wave 常用参数 | -format : 显示格式(logic等) -color : 波形的颜色 -divider : 添加一个分割线,通常按功能模块分割 -radix : 数值显示形式(binary, ascii , decimal, octal, hex) -group : 信号分组显示 |

| quit -sim | 退出当前仿真 |

| .main clear | 清输出窗口 |

| view wave | 打开波形窗口 |

| view structure | 打开structure窗口 |

| view signals | 打开信号窗口 |

modelsim波形常用颜色:

| 波形颜色 | 名称 |

| 浅蓝 | cyan,数据总线可以采用浅蓝色 |

| 蓝 | blue |

| 黄 | yellow,管脚的EN类信号可以采用黄色,用于突出 |

| 粉 | pink,粉色,状态机类的信号,可以采用粉色用于突出 |

| 绿 | green,不太需要关注的信号,往往采用绿色即可 |

| 灰色 | gray40,寄存器配置类型的常量,可以采用灰色,表示不用重点关注 |

modelsim观察常用进制:

| 进制 | radix |

| 二进制 | binary |

| 八进制 | octal |

| 十进制 | decimal |

| 十六进制 | hexadecimal |

| 有符号数 | |

| 无符号数 | unsigned |

| 阿斯科码 | ascii |

工程文件夹说明

| rtl | 存放RTL代码 | |

| 00_xilinx_ip | 存放Xilinx IP | |

| 01_use_ip | 存放user IP | |

| sim | 存放SIM文件,存放rum_sim.bat文件。将modelsim工作路径调整到该文件夹。 | |

| log | 存放log文件 | |

| cov | 存放cov文件,仿真覆盖率文件 | |

| sim_model | 存放仿真模型文件 | |

| tb_pattern | 存放仿真顶层文件tb_top | |

| wave | 存放wlf波形文件 | |

| wave_do | 存放run_wave.do文件 | |

| work |

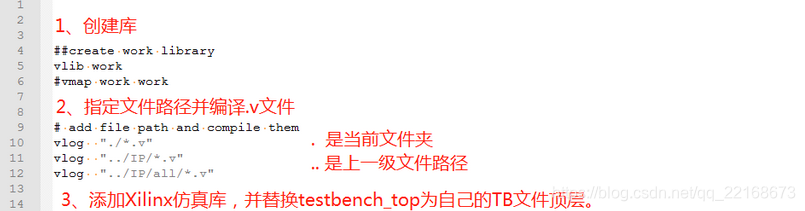

步骤一:创建run_wave.do

在ISE与modelsim关联好之后,modelsim里就会有“ xilinxcorelib, simprim,unimacro, unisim ” 这四个仿真库,-L 即是指定这四个逻辑库的过程。

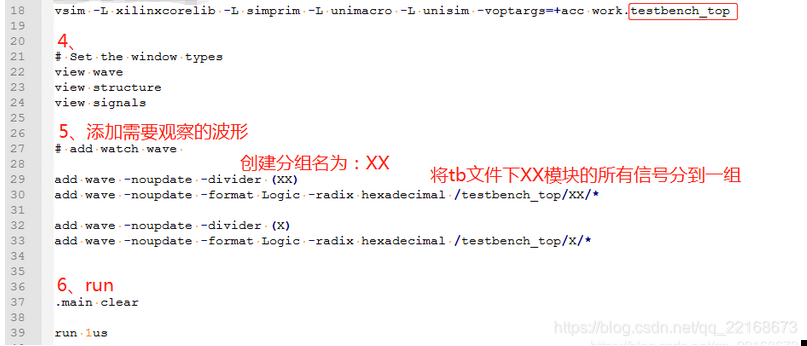

步骤3,work.testbench_top, “testbench_top”是tb的模块名,而非.v文件的文件名,注意两者名称存在不同。

步骤5,添加模块信号,都是模块名,而非.v文件的文件名。两者名称可能存在不同。

下面是一种示例的 run_wave.do 文件的示例:

#================================================================

# Clear

#================================================================

# 退出当前仿真

quit -sim

# 清输出窗口

.main clear

#================================================================

# Create work library

#================================================================

# It will create a "work" folder in current folder

# 创建本地库

vlib work

# 将逻辑库名映射库路径

vmap work work

#================================================================

# Compile IPcore

#================================================================

# Add File path and Compile them

vlog ../../xilinx_ip/*.V

vlog ./*.V

#================================================================

# Compile RTL

#================================================================

# 编译当前目录下的所有v文件

vlog ./*.v

# 编译上一级目录下的所有v文件

vlog ../*.V

#================================================================

# Start the emulator(启动仿真器)

#================================================================

#方式一:

vsim -L xilinxcorelib -L simprim -L unimacro -L unisim -voptargs=+acc work.tb_top

#方式二:

vsim -novopt -t 1ps -c -L simprim -L unimacro -L unisim -l ./log/report.log -wav ./wave/tb.wlf -voptargs=+acc work.tb_top

#方式三:添加quartus仿真库

#vsim -novopt -t 1ps -c -L altera_lnsim_ver -L altera_mf_ver -L altera_ver -L cycloneii_ver -L lpm_ver -L sgate_ver -l ./log/report.log -wav ./wave/tb.wlf -voptargs=+acc work.TB

#================================================================

# Set the window types

#================================================================

view wave

view structure

view signals

#================================================================

# Add watch wave

# color : green cyan yellow pink violet orchid gray40

# radix : binary unsigned hexadecimal

# 建议:常量/寄存器的值波形使用gray40;数据总线cyan;FSM pink;控制信号yellow/pink;其他信号green

#================================================================

add wave -noupdate -divider (TB_TOP)

add wave -noupdate -color green -format Logic -radix unsigned -group {TB_TOP} /TB_TOP/*

#================================================================

# run

#================================================================

.main clear

run 10us在run_wave.do 文件里,参考下面代码,modelsim仿真时让状态机波形显示状态的名字。

建议状态机类型的信号都采用下面这种方法,便于观察分析波形。

#1、使用ModelSim的 virtual type 命令定义一个新的枚举类型(FSM_TYPE)。注意:状态变量之间需要一个空格

virtual type { {0x00 IDLE} {0x01 S0} {0x02 S1} } FSM_TYPE

#2、将需要显示的信号(/simple_fsm_tb/u_simple_fsm/curr_state,注意信号在wave窗口中的完整名字)进行类型转换,转换成一个新的信号(state1)

virtual function {(FSM_TYPE)/simple_fsm_tb/u_simple_fsm/curr_state} state1

#3、将新的信号加入到wave窗口中

add wave -noupdate -color pink -format Logic -radix hexadecimal -group {TX} /simple_fsm_tb/u_simple_fsm/state1

#4、添加原波形

add wave -color pink /simple_fsm_tb/u_simple_fsm/curr_state

步骤二:打开Modelsim

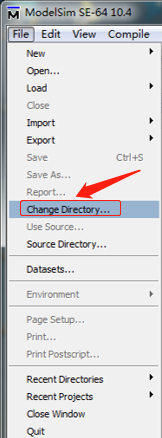

写好上面 run_wave.do 文件后,打开modelsim软件,将工作路径指定到 run_wave.do 所在的文件路径。

file--change directory

步骤三:do run_wave.do

| 常用指令 | 功能 |

| do run_wave.do | 运行当前路径下的run_wave.do文件 |

| do XX/run_wave.do | 运行当前路径下XX文件夹下的run_wave.do文件 |

| do ../XX/run_wave.do | 运行上一级文件路径下XX文件夹下的run_wave.do文件 |

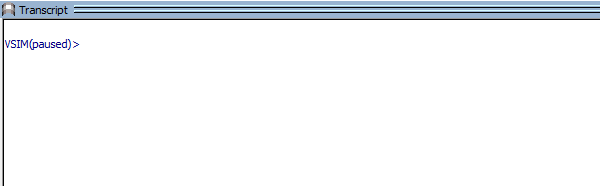

在下面指令窗口中,输入"do XX/run_wave.do",do即执行,中间有一个空格,XX/run_wave.do即当前路径下XX文件夹里run_wave.do文件。即执行该路径下XX文件夹里run_wave.do文件。

在输入“do XX/run_wave.do”指令时,可以采用“Tab键”补全功能!

步骤4:run_sim.bat

可以写一个.bat文件,内容有两行 cd ##此处填写路径## vsim -do file.do 这样保存后双击这个.bat文件就可以启动运行ModelSim了。

创建文件run_sim.bat文件,输入下面两行代码。

第一行:指定run_wave.do所在的决对路径,即在文件夹wave_do里面;

第二行:打开modelsim软件,运行run_wave.do文件。

cd C:/Users/sim/wave_do

vsim -do run_wave.do如果要运行wave_do文件夹下子文件夹里的程序,可参考:

cd C:/Users/sim/wave_do

vsim -do do/compile.do -do do/tb.do

上述指令第二行执行动作是

- 打开modelsimSE软件,

- 执行该文件夹下子文件do文件夹里的compile.do文件;

- 顺序执行该文件夹下子文件do文件夹里的tb.do文件

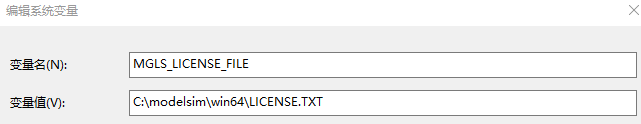

如果遇到点击bat,ModelSimSE打不开的情况,首先检查环境变量MGLS_LICENSE_FILE设置的路径对不对;

其次检查环境变量里PATH路径下是否含有ModelSimSE.exe的安装路径,或该路径是否存在。不存在添加上即可。

注:

如果运行bat出现错误,删掉第一行,保留第二行。再次运行bat。

如果,再次执行步骤4出问题的话,可忽略步骤4。采用步骤3启动modelsim进行仿真即可。

modelsim仿真波形分析

在modelsim仿真中常见到的问题是波形信号是红色的,或者波形信号是4'hXX这类的不定状态。产生XX不定状态的原因可能是该信号没有复位逻辑,或者该信号与其他模块连接的地方发送冲突。

需要上电被赋初值的寄存器信号,比如r_SIGNAL需要上电就被赋初值,可以参考下面的语句。之后,再在always语句块中进行逻辑赋值操作。

initial r_SIGNAL = 1'b0;具体波形分析步骤可以参考:

1、首先检查被测模块时钟(clk)复位(rst)状态是否正常。

2、其次检查所有信号在复位后的值是否正常,是否存在5'hXX等这类带XX的信号,XX表示该信号状态不确定,会对FPGA逻辑造成不确定的状态。

3、检查被测模块的信号输入端,是否是按设计进行控制的。这个过程,需要注意每个波形信号的进制表示,便于分析。

4、之后,检查被测模块的状态运转以及时序功能是否正常。

补充介绍

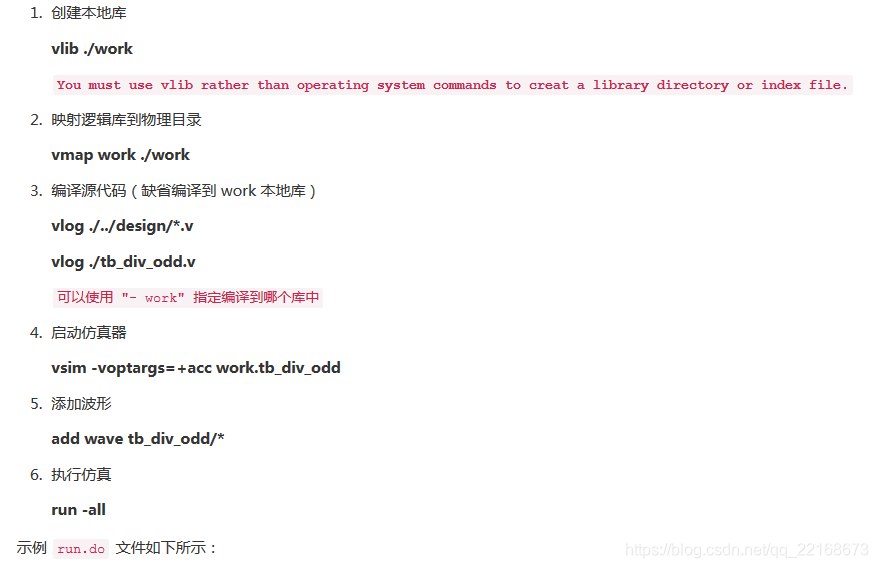

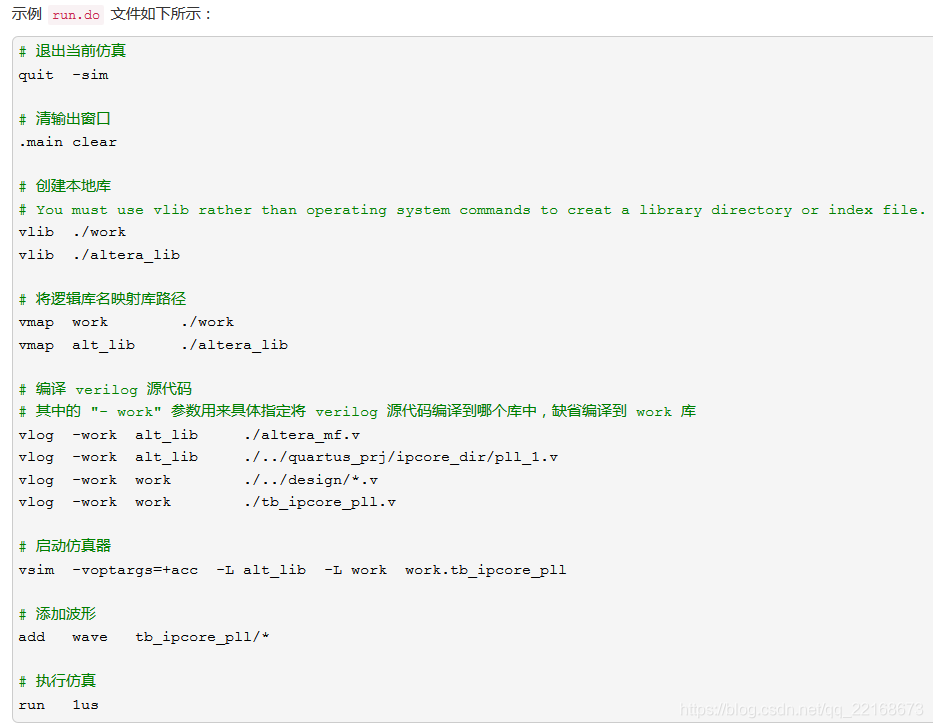

下文转载自博文: https://www.cnblogs.com/bitrocco/p/9576505.html

# 退出当前仿真

quit -sim

# 清输出窗口

.main clear

# 创建本地库

# You must use vlib rather than operating system commands to creat a library directory or index file.

vlib ./work

vlib ./altera_lib

# 将逻辑库名映射库路径

vmap work ./work

vmap alt_lib ./altera_lib

# 编译 verilog 源代码

# 其中的 "- work" 参数用来具体指定将 verilog 源代码编译到哪个库中,缺省编译到 work 库

vlog -work alt_lib ./altera_mf.v

vlog -work alt_lib ./../quartus_prj/ipcore_dir/pll_1.v

vlog -work work ./../design/*.v

vlog -work work ./tb_ipcore_pll.v

# 启动仿真器

vsim -voptargs=+acc -L alt_lib -L work work.tb_ipcore_pll

# 添加波形

add wave tb_ipcore_pll/*

# 执行仿真

run 1us# ========================================================================

vsim -t ns -voptargs=+acc -L design -L base_space base_space.*.v

# -t 运行仿真的精度是 ns

# -L 链接库关键字

# ========================================================================

# ========================================================================

# ---- 虚拟信号 ----

virtual type {

{01 IDLE}

{02 A}

{04 B}

{08 C}

{16 D}

{32 E}

} vir_new_signal

virtual function {

(vir_new_signal)tb_seq_det/seq_det_inst/state

} new_state

add wave tb_seq_det/seq_det_inst/new_state

# ========================================================================

quit -sim

.main clear

vlib ./lib/

vlib ./lib/work/

vmap work ./lib/work/

vlog -work work ./tb_shift_reg.v

vlog -work work ./../design/shift_reg.v

vsim -voptargs=+acc work.tb_shift_reg

add wave tb_shift_reg/clk

add wave tb_shift_reg/rst_n

add wave tb_shift_reg/mem1x16

add wave tb_shift_reg/i_30

add wave tb_shift_reg/i_data

add wave tb_shift_reg/shift_reg_inst/shift_reg

add wave tb_shift_reg/shift_reg_inst/s_cnt

add wave tb_shift_reg/shift_reg_inst/s_flag

add wave tb_shift_reg/shift_reg_inst/s_flag_delay

add wave tb_shift_reg/shift_reg_inst/o_data

add wave tb_shift_reg/o_data

run 10us

# ========================================================================

# ---- 后仿真 ----

quit -sim

.main clear

vlib ./lib/

vlib ./lib/work/

vlib ./lib/altera_lib/

vmap work ./lib/work/

vmap altera_lib ./lib/altera_lib/

vlog -work work ./tb_seq_det.v

vlog -work work ./../design/*.vo

vlog -work altera_lib ./altera_lib/*.v

vsim -t ns -sdfmax tb_seq_det/seq_det_inst=seq_det_v.sdo -voptargs=+acc -L altera_lib work.tb_seq_det

add wave tb_seq_det/*

run 10us

# ========================================================================参考

| 1、作者 | 博文 |

| Modelsim自动化仿真之do文件书写 | |

| modelsim仿真时让状态机波形显示状态的名字 | |

| 基于脚本的modelsim自动化仿真笔记 | |

| 一曲挽歌 FPGA辅助设计脚本——Tcl |

本文详细介绍Modelsim自动化仿真的流程,包括.do文件的编写、批处理文件的使用、仿真库的管理和信号波形的分析技巧。同时,文章提供了实用的TCL脚本示例,帮助读者快速掌握Modelsim自动化仿真技术。

本文详细介绍Modelsim自动化仿真的流程,包括.do文件的编写、批处理文件的使用、仿真库的管理和信号波形的分析技巧。同时,文章提供了实用的TCL脚本示例,帮助读者快速掌握Modelsim自动化仿真技术。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?