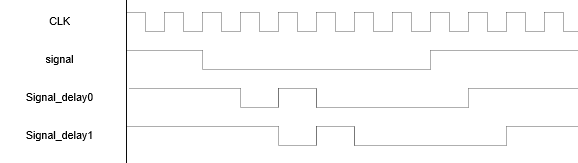

问题现象:将该信号在FPGA内部使用250MHZ连续打若干拍。示波器抓取原始信号如图所示。

使用chipscope抓取该信号和打拍后的信号,可以看到该信号没有毛刺,但是打拍后的信号在低电平前8ns会存在有一个时钟周期的高电平毛刺现象。

解决方式:添加数字滤波,或者脉宽检测也可以。检测信号signal低电平的时候启动计数器、否则计数器清零;当计数器大于3时,产生一个低电平信号XX_n,将该低电平信号XX_n代替原始信号signal做逻辑设计。

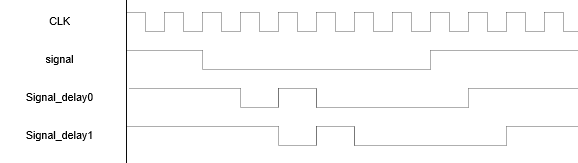

问题现象:将该信号在FPGA内部使用250MHZ连续打若干拍。示波器抓取原始信号如图所示。

使用chipscope抓取该信号和打拍后的信号,可以看到该信号没有毛刺,但是打拍后的信号在低电平前8ns会存在有一个时钟周期的高电平毛刺现象。

解决方式:添加数字滤波,或者脉宽检测也可以。检测信号signal低电平的时候启动计数器、否则计数器清零;当计数器大于3时,产生一个低电平信号XX_n,将该低电平信号XX_n代替原始信号signal做逻辑设计。

1899

1899

3382

3382

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?