一、IEEE-754规范

IEEE-754标准数值表示包括:浮点数,特殊值(零,无穷大,非标准数值,nan), 单精度、双精度、单精度扩展格式的浮点数。

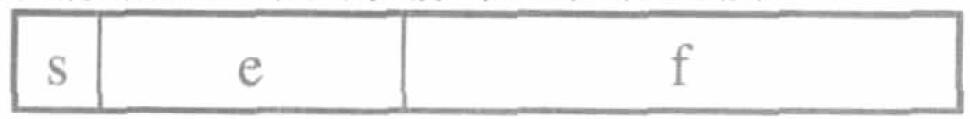

(1)浮点格式。在IEEE-754标准中,所有的浮点数都用二进制模板表示:

其中,S域表示符号位,E域表示指数,M域表示尾数(对数的一部分或小数)。 对于标准浮点数,默认总是存在1个隐含的引导位“1”。例如,二进制数1.0011或十进制数1.1875用IEEE-754标准格式表示时其M域的值为0011,在标识格式中不保存隐含的引导位“1”。对于非标准浮点数,引导位可以是“1”或“0”。对于零,无穷大和nan, M域没有隐含的引导位“1”或者没有明确的引导位。

(2)单精度浮点数。单精度浮点数用32位二进制数表示,其中最高位( Bit[31], MSB)为符号位,即S域; Bit[30:23]为 E域,这8位数据表示指数;最低的23位(Bit[22:0], LSB )为M域,用于表示浮点数的小数部分。

(3)双精度浮点数。双精度浮点数用64位二进制数表示,其中最高位( Bit[63], MSB)为符号位,即S域; Bit[62:52]为E域, 这11位表示指数;最低的52位(Bit[51:0], LSB)为M域,用于表示浮点数的小数部分。

所以它表示的浮点数y值如下所示

二、浮点数的加减运算

浮点加法运算的实现包括以下几个步骤符号判断、: 对阶、尾数加减操作、规格化、舍入操作、溢出判断。具体实现时通常把规格化、舍入操作、溢出判断作为一个步骤实现。浮点数的格式显然可以分为两部分, 即符号和数据的绝对值。若符号相同则符号不便绝对值相加; 若符号不同则须比较两绝对值的大小然后两绝对值作差运算。符号不同时首先判断和的符号, 显然若两浮点数的阶不同时和的符号当与阶数大的操作数相同; 若阶数不同则继续比较对阶操作首先比较两浮点数的阶数大小。然后需要两数对阶。对阶的原则是小阶对大阶,小阶对大阶的好处是,当小阶不同于大阶时,只需要移除小阶数的尾数部分的低位部分。加法流程图见下图

三、浮点数的乘法运算

浮点数的乘法运算相对比较简单,只需要将两个操作数的符号位进行异或运算,再将阶码部分做和、尾数部分做积即可。同时需要检查操作数的运算结果是否有溢出问题。乘法流程如下图:

四、使用Altera的IP核实现浮点运算

下图为Altera提供的浮点加法运算IP核设置界面。

IP核设置为64位输入与输出、延迟14个时钟周期输出结果、选择速度优化、使能‘加、减’动态切换功能。模块功能引脚见下表

| 信号名称 | 信号方向 | 说明 |

| dataa | I | 数据输入符合IEEE-754标准 |

| datab | I | 数据输入符合IEEE-754标准 |

| add_sub | I | 加减法功能动态切换,高电平执行加操作 |

| clk | I | 系统时钟 |

| result | O | 运算输出 |

| NaN | O | NaN异常输出 |

| overflow | O | overflow异常输出, |

| underflow | O | underflow异常输出 |

| zero | O | 零输出 |

接下来例化加法模块,然后写一个tb进行功能仿真,仿真结果下图所示,其中inNum1和inNum2为两个加数,outNum为运算结果数。

五、总结

在FPGA中做运算时特别是浮点运算时,相比ARM和DSP总是显得力不从心,但FPGA 来实现浮点运算成为具有高速、低成本、开发周期短等优点。并且使用IP核进行开发FPGA可以大大缩短算法在FPGA上实现的周期。

本文为笔者学习笔记,笔者经验不足,能力有限,如有纰漏望即使提出。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?