chapter2 chapter2:DSP 48E1 的描述和细节

目录

2.2Architectural Highlights of the 7 Series FPGA DSP48E1 Slice

2.4 Simplified DSP48E1 Slice Operation

2.5 DSP48E1 Slice Attributes(属性)

本章提供7系列FPGA(DSP48E1 Slice)中可用的DSP元件的技术细节。

DSP48E1 Slice可提高灵活性和利用率,提高应用效率,降低总体功耗并提高最大频率。 高性能允许设计人员使用时分复用方法在单个DSP48E1 Slice中实现多个较慢的操作。

DSP48E1 Slice支持许多独立功能。 这些功能包括乘法,乘法累加(MACC),乘法加法,三输入加法,桶形移位(barrel shift),宽总线多路复用(wide-bus multiplexing),幅度比较器(magnitude comparator,),按位逻辑功能(bitwise logic functions),模式检测和宽计数器(pattern detect, and wide counter)。 该架构还支持级联多个DSP48E1 Slice以形成宽数学函数,DSP滤波器和复杂算术,而无需使用通用FPGA逻辑。

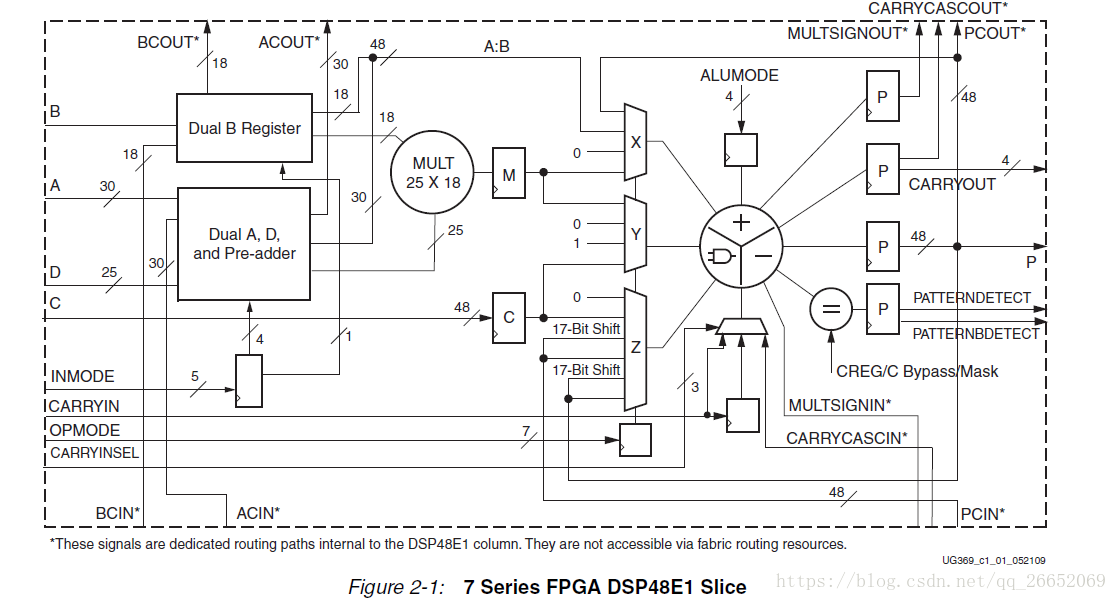

7系列FPGA DSP48E1 Slice如图2-1所示。 该片在功能上等同于Virtex®-6 FPGA DSP48E1片,是Virtex-5器件中DSP48E片的扩展,在Virtex-5 FPGA XtremeDSP设计注意事项用户指南[参考文献1]中有所描述。

2.1 DSP48E1 Slice Features

本节介绍7系列FPGA DSP48E1 Slice功能。

DSP片由乘法器(multiplier)和累加器(accumulator)组成。乘法和乘法累加运算至少需要三个流水线寄存器才能全速运行。第一阶段中的乘法运算生成两个需要在第二阶段中加在一起的部分乘积。

当乘法器设计中只存在一个或两个寄存器时,应始终使用M寄存器来节省功耗并提高性能。

加/减和逻辑单元操作需要至少两个流水线寄存器(输入,输出)才能全速运行。

DSP Slice的级联功能在实现基于加法器级联而非加法器树的高速流水线滤波器方面非常高效。

多路复用器由动态控制信号控制,例如OPMODE,ALUMODE和CARRYINSEL,可实现极大的灵活性。使用寄存器和动态opmode的设计可以更好地利用DSP切片功能而不是组合乘法。

通常,由于动态OPMODE和级联功能,DSP Slice支持顺序和级联操作。快速傅立叶变换(FFT),浮点,计算(乘法,加/减,除),计数器和大型总线多路复用器是DSP Slice的一些应用。

DSP Slice的其他功能包括同步复位和时钟使能,双A输入流水线寄存器,模式检测,逻辑单元功能,单指令/多数据(SIMD)功能,以及96位的MACC和Add-Acc扩展。 DSP Slice支持收敛和对称舍入,计数器的终端计数检测和自动复位,以及顺序累加器的上溢/下溢检测。

ALU功能与7系列FPGA DSP48E1 Slice相同,与Virtex-6 FPGA DSP48E1 Slice相同。有关详细信息,请参阅第35页的ALUMODE输入。

2.2Architectural Highlights of the 7 Series FPGA DSP48E1 Slice

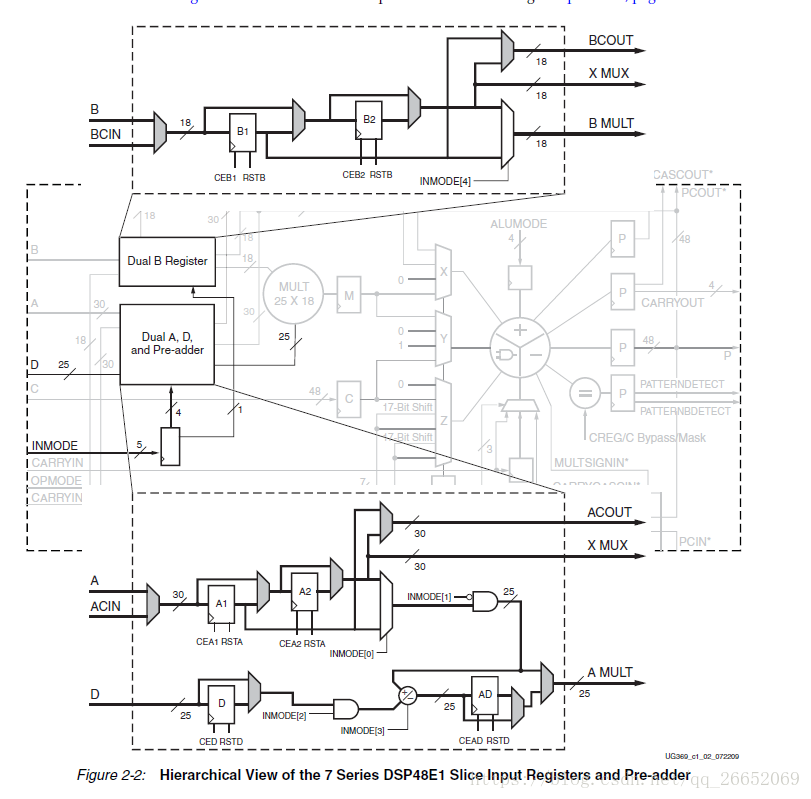

7系列FPGA DSP48E1 Slice在功能上与Virtex-6 FPGA DSP48E1相当。 7系列FPGA DSP48E1 Slice在A寄存器之后包含一个预加法器,该寄存器具有一个名为D的25位输入向量.D寄存器可用作预加法器寄存器或乘法器的备用输入。 DSP48E1的具体功能如图2-2所示。 从输入端口(第29页)开始可以找到更详细的说明。

7系列FPGA DSP48E1片的功能:

- 带有D寄存器的25位预加法器,以用于增强A路径的功能

- 当在multiply(A * B)即乘法操作和(A:B)add操作之间动态切换时,INMODE控件支持平衡流水线操作

- 25 x 18乘法

- 30-bit的A输入,其低25位馈送到乘法器的A输入,整个30位输入形成48位A:B连接内部总线的高30位。

- 级联A和B输入

-可在直接路径和级联路径之间进行半独立选择的流水线操作

- 独立时钟使能两个深度的A和B组输入寄存器

- 独立的C输入和C寄存器,且具有独立的复位和时钟使能。

- CARRYCASCIN和CARRYCASCOUT内部级联信号支持两个DSP48E1片中的96位累加器/加法器/减法器

- MULTSIGNIN和MULTSIGNOUT内部级联信号具有特殊的OPMODE设置,支持96位MACC扩展

- 用于三输入加法器/减法器的单指令多数据(SIMD)模式,它排除了在第一阶段使用乘法器即说明用了SIMD模式就不能使用乘法器?

- 双24位SIMD加法器/减法器/累加器,带有两个独立的CARRYOUT信号

- 四路12位SIMD加法器/减法器/累加器,带有四个独立的CARRYOUT信号

- 48位逻辑单元

-按位逻辑运算 - 双输入AND,OR,NOT,NAND,NOR,XOR和XNOR

-逻辑单元模式可通过ALUMODE动态选择

- 模式检测器

- 溢出(Overflow)/下溢(underfolw)支持

- 收敛舍入(Convergent rounding)支持

- 终端计数检测支持和自动重置

- 级联48位P总线支持内部低功耗加法器级联

48位P总线允许12位/ QUAD或24位/ DUAL SIMD加法器级联支持

- 可选的17位右移以实现更宽的乘法器实现

- 动态的用户控制操作模式

7位OPMODE控制总线提供X,Y和Z多路复用器选择信号

- Carry in for第二阶段加法器

支持舍入

支持更广泛的加法/减少

3位CARRYINSEL多路复用器

- Carry for第二阶段加法器

支持更广泛的添加/减少

适用于每个SIMD加法器(最多四个)

- 级联CARRYCASCOUT和MULTSIGNOUT允许MACC扩展高达96位

- 可选输入,流水线和输出/累加寄存器

- 控制信号的可选控制寄存器(OPMODE,ALUMODE和CARRYINSEL)

- 独立时钟使能和复位具有更高的灵活性,且复位优先。

- 为了在不使用第一级乘法器时节省功耗,USE_MULT属性允许客户关闭内部乘法器逻辑。

每个DSP48E1 Slice都有一个双输入乘法器,后面是多路复用器和一个三输入加法器/减法器/累加器。 DSP48E1乘法器具有非对称输入,可接受18位二进制补码操作数和25位二进制补码操作数。乘法器阶段以两个部分乘积的形式产生43位二进制补码结果。这些部分乘积在X多路复用器和Y多路复用器中被符号扩展(sign-extended)为48位,并馈入到三输入加法器以进行最终求和。这导致43位乘法输出,该输出被符号扩展为48位。因此,当使用乘法器时,加法器有效地成为两输入加法器。

第二级加法器/减法器接受三个48位二进制补码操作数,当通过将USE_MULT属性设置为NONE并使用适当的OPMODE设置绕过乘法器时,产生一个48位,二进制补码结果。在SIMD模式下,48位加法器/减法器还支持带有CARRYOUT位的双24位或四路12位SIMD算术运算。在此配置中,动态ALUMODE控制信号还支持两个48位二进制数的按位逻辑运算。

DSP48E1列中的各个DSP48E1片段级联支持更高级别的DSP功能。两个数据路径(ACOUT和BCOUT)和DSP48E1片输出(PCOUT,MULTSIGNOUT和CARRYCASCOUT)提供级联功能。级联数据路径的能力在滤波器设计中很有用。例如,有限脉冲响应(FIR)滤波器设计可以使用级联输入来排列一系列输入数据样本和级联输出,以排列一系列部分输出结果。级联的能力提供了DSP滤波器功能的高性能和低功耗实现,因为不使用结构中的一般路由。

C输入端口允许形成许多3输入数学函数,例如3输入加法或带有加法的2输入乘法。该函数的一个子集是对乘以零或向无穷大对称舍入的有价值的支持。 C输入与模式检测器一起还支持会聚舍入。

对于多精度算术,DSP48E1 Slice提供了17的右移位。因此,来自一个DSP48E1 Slice的部分乘积可以右对齐并添加到在相邻DSP48E1 Slice中计算的下一个部分乘积。使用这种技术,DSP48E1切片可用于构建更大的乘法器。

输入操作数,中间产品和累加器输出的可编程流水线操作增强了吞吐量。 48位内部总线(PCOUT / PCIN)允许在单列中聚合DSP片。跨越多列时需要结构逻辑。

DSP48E1 Slice输出端的模式检测器支持收敛舍入,上溢/下溢,块浮点,并支持累加器终端计数(计数器自动复位)。模式检测器可以检测DSP48E1切片的输出是否与模式匹配,如掩模所限定。

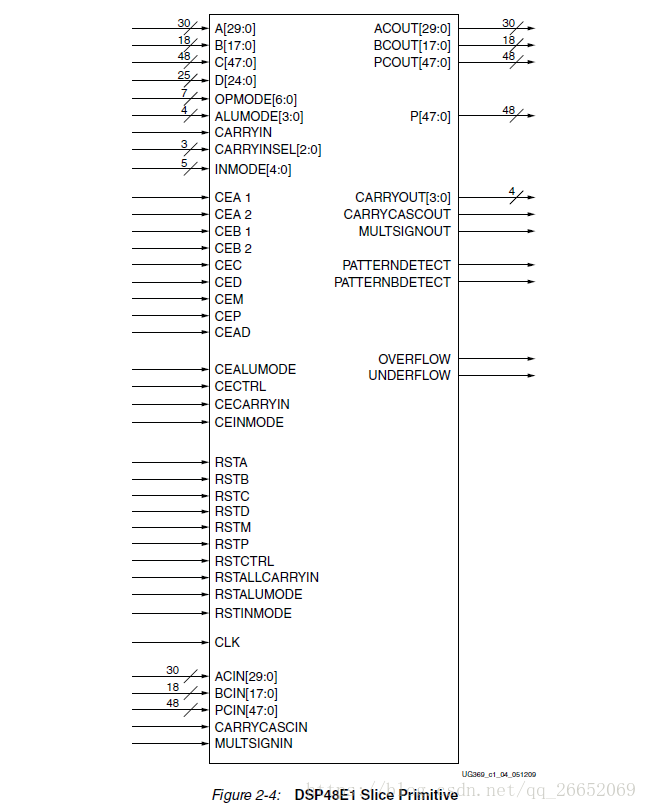

2.3DSP48E1 Slice Primitive

图2-4显示了DSP48E1原语。 它还显示了DSP48E1 Slice的输入和输出端口以及每个端口的位宽。 端口定义见表2-2。

Table 2-2 DSP 48E1 Port Description

| Name | Direction | BitWidth | Description |

|---|---|---|---|

| A | In | 30 | A [24:0]是乘法器或预加法器的A输入。 A [29:0]是A:B级联输入到第二级加法器/减法器或逻辑函数的最高有效位(MSB)。 |

| ACIN | In | 30 | 从先前DSP48E1片的ACOUNT输入的级联数据(与A混合)。 |

| ACOUT | Out | 30 | 级联数据输出到下一个DSP48E1片的ACIN |

| ALUMODE | In | 4 | 控制DSP48E1 Slice中逻辑功能的选择(见表2-13)。 |

| B | In | 18 | 乘法器的B输入。 B [17:0]是A:B级联输入到第二级加法器/减法器或逻辑函数的最低有效位(LSB)。 |

| BCIN | Out | 18 | 从以前的DSP48E1片的BCOUT口输入的级联数据(与B muxed) |

| BCOUT | Out | 18 | 输出到下一个DSP48E1片的BCIN |

| C | In | 48 | 到第二级加法器/减法器,模式检测器或逻辑功能的数据输入 |

| CARRYCASCIN | In | 1 | 来自先前DSP48E1切片的CARRYCASCOUT的级联进位输入。 |

| CARRYCASCOUT | Out | 1 | 级联进位输出到下一个DSP48E1切片的CARRYCASCIN。 该信号在内部反馈到同一DSP48E1 Slice的CARRYINSEL多路复用器输入端。 |

| CARRYIN | In | 1 | Carry input from the FPGA logic. |

| CARRYINSEL | In | 3 | Selects the carry source (see Table 2-11). |

| CARRYOUT | Out | 4 | 来自累加/加法器/逻辑单元的每个12位字段的4位进位输出。 正常的48位操作仅使用CARRYOUT3。 SIMD操作可以使用四个进位(CARRYOUT [3:0])。 |

| CEA1 | In | 1 | 第一个A(输入)寄存器的时钟使能。 A1仅在AREG = 2或INMODE [0] = 1时使用。 |

| CEA2 | In | 1 | 第二个A(输入)寄存器的时钟使能。 A2仅在AREG = 1或2且INMODE [0] = 0时使用。 |

| CEAD | In | 1 | 用于预加法器输出AD流水线寄存器的时钟使能 |

| CEALUMODE | In | 1 | ALUMODE(控制输入)寄存器的时钟使能。 |

| CEB1 | In | 1 | 第一个B(输入)寄存器的时钟使能。 B1仅在BREG = 2或INMODE [4] = 1时使用。 |

| CEB2 | In | 1 | 第二个B(输入)寄存器的时钟使能。 B2仅在BREG = 1或2且INMODE [4] = 0时使用 |

| CEC | In | 1 | Clock enable for the C (input) register. |

| CECARRYIN | In | 1 | Clock enable for the CARRYIN (input from FPGA logic) register. |

| CECTRL | In | 1 | OPMODE和CARRYINSEL(控制输入)寄存器的时钟使能。 |

| CED | In | 1 | Clock enable for the D (input) register. |

| CEINMODE | In | 1 | Clock enable for the INMODE control input registers. |

| CEM | In | 1 | 后乘法M(流水线)寄存器和内部乘法轮?舍入? CARRYIN寄存器的时钟使能。 |

| CEP | In | 1 | Clock enable for the P (output) register. |

| CLK | In | 1 | CLK是DSP48E1输入时钟,对所有内部寄存器和触发器都是通用的。 |

| D | In | 25 | 输入到预加法器的25位数据或乘法器的替代输入。 预加法器实现由INMODE3信号来确定的D + /-A. |

| INMODE | In | 5 | 这五个控制位选择预加器,A,B和D输入以及输入寄存器的功能。 如果未连接,这些位应默认为5'b00000。 这些可选地是可逆的,提供了路由灵活性。 |

| MULTSIGNIN | In | 1 | 来自先前DSP48E1切片的乘法结果的符号用于MACC扩展。 |

| MULTSIGNOUT | Out | 1 | 乘法结果的符号 级联到下一个用于MACC扩展的DSP48E1片。 |

| OPMODE | In | 7 | 控制DSP48E1 Slice中X,Y和Z多路复用器的输入(见表2-7,表2-8和表2-9)。 |

| OVERFLOW | Out | 1 | 与模式检测器的适当设置一起使用时溢出指示。 |

| P | Out | 48 | Data output from second stage adder/subtracter or logic function. |

| PATTERNBDETECT | Out | 1 | Match indicator between P[47:0] and the pattern bar. |

| PATTERNDETECT | Out | 1 | Match indicator between P[47:0] and the pattern. |

| PCIN | In | 48 | Cascaded data input from PCOUT of previous DSP48E1 slice to adder. |

| PCOUT | Out | 48 | Cascaded data output to PCIN of next DSP48E1 slice. |

| RSTA | In | 1 | Reset for both A (input) registers. |

| RSTALLCARRYIN | In | 1 | Reset for the Carry (internal path) and the CARRYIN register. |

| RSTALUMODE | In | 1 | Reset for ALUMODE (control inputs) registers. |

| RSTB | In | 1 | Reset for both B (input) registers. |

| RSTC | In | 1 | Reset for the C (input) register. |

| RSTCTRL | In | 1 | Reset for OPMODE and CARRYINSEL (control inputs) registers. |

| RSTD | In | 1 | Reset for the D (input) register and for the pre-adder (output) AD pipeline register. |

| RSTINMODE | In | 1 | Reset for the INMODE (control input) registers. |

| RSTM | In | 1 | Reset for the M (pipeline) register. |

| RSTP | In | 1 | Reset for the P (output) register. |

| UNDERFLOW | Out | 1 | 与模式检测器的适当设置一起使用时的下溢指示。 |

【注意】

1.当不使用这些数据端口时为了降低漏电功耗时,数据端口输入信号必须接高电平,必须选择端口输入寄存器,CE和RST输入控制信号必须接低电平。 比如未使用的C端口,推荐设置的示例是C [47:0] =全1,CREG = 1,CEC = 0和RSTC = 0。

2.这些信号是DSP48E1列内部的专用路由路径。 它们无法通过结构路由资源访问。

3.所有信号均为高电平有效。

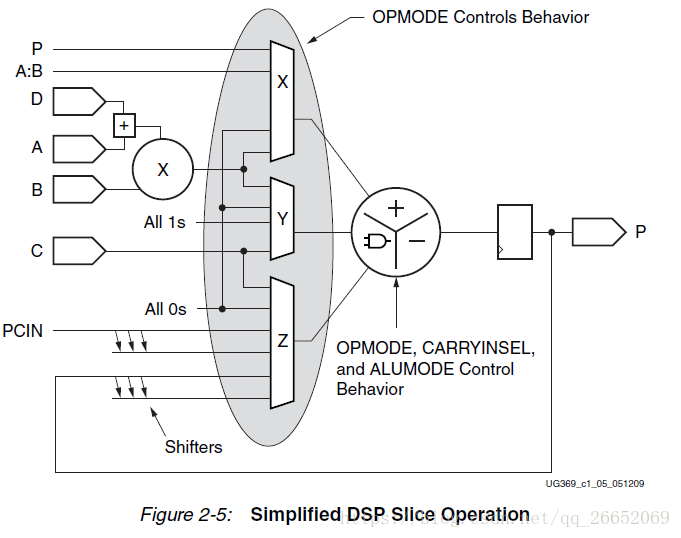

2.4 Simplified DSP48E1 Slice Operation

DSP48E1 Slice的数学部分包括一个25位预加法器,一个25位乘18位二进制补码乘法器,后跟三个48位数据路径多路复用器(带有输出X,Y和Z)。接下来是三输入加法器/减法器或双输入逻辑单元(见图2-5)。使用双输入逻辑单元时,不能使用乘法器。

DSP48E1 Slice的数据和控制输入提供算术和逻辑级。 A和B数据输入可选择寄存一次或两次,以帮助构建不同的高流水线DSP应用解决方案。 D路径和AD路径均可以寄存一次。其他数据输入和控制输入可以选择性地寄存一次。数据手册中规定的最大频率操作是通过使用流水线寄存器实现的。更详细的时序信息可在第3章DSP48E1设计注意事项中找到。

在最基本的形式中,加法器/减法器/逻辑单元的输出是其输入的函数。输入由上游多路复用器,进位选择逻辑和乘法器阵列驱动。

公式2-1总结了加法器/减法器对X,Y,Z和CIN的组合。 CIN,X多路复用器输出和Y多路复用器输出始终加在一起。该组合结果可以选择性地添加到Z多路复用器输出或从Z多路复用器输出中减去。通过将ALUMODE设置为0001来获得第二个选项。

(2-1)

Slice的典型用法是将A和B输入相乘,并将结果加到C寄存器或从C寄存器中减去。基于控制和数据输入的更详细操作将在后面的章节中介绍。选择乘法器功能会消耗X和Y多路复用器输出以馈送加法器。来自乘法器的两个43位部分乘积在被发送到加法器/减法器之前被符号扩展到48位。

当不使用第一级乘法器时,48位双输入按位逻辑功能实现AND,OR,NOT,NAND,NOR,XOR和XNOR。 这些功能的输入是通过X和Z多路复用器选择的A:B,C,P或PCIN,Y多路复用器根据逻辑操作选择全1或全0。

加法器/减法器或逻辑单元的输出馈送模式检测器逻辑。模式检测器允许DSP48E1 Slice支持收敛舍入,达到计数值时的计数器自动复位,以及累加器中的溢出/下溢/饱和。结合逻辑单元,可以扩展模式检测器以执行两个48位字段的48位动态比较。这使得能够实现诸如A:B NAND C = = 0或A:B(按位逻辑)C = =模式的功能。

图2-5以非常简化的形式显示了DSP48E1 Slice。 7个OPMODE位控制X,Y和Z多路复用器的选择,将输入馈送到加法器/减法器或逻辑单元。在所有情况下,从乘法器到X和Y多路复用器的43位部分乘积数据被符号扩展,形成加法器/减法器的48位输入数据路径。基于43位操作数和48位累加器输出,保护位的数量(即可用于防止溢出的位)为5.要扩展MACC操作的数量,应使用MACC_EXTEND功能,这允许MACC通过两个DSP48E1片扩展到96位。如果A端口限制为18位(符号扩展为25),则MACC有12个保护位。乘法运算期间CARRYOUT位无效。 OPMODE,ALUMODE,CARRYINSEL和CARRYIN的组合控制加法器/减法器或逻辑单元的功能。

2.4.1 DSP48E1 Slice Attributes(属性)

本节描述了DSP48E1 Slice的综合属性。 这些属性在控件和数据路径中调用流水线寄存器。 属性的值设置寄存器的数量。 见表2-3。

| 属性名称 Attribute Name | Settings (Default) |

|---|---|

| Register Control Attributes | |

| ACASCREG | 与AREG一起,选择A级联路径上的A输入寄存器的数量ACOUT。 此属性必须等于或小于AREG值: AREG = 0:ACASCREG必须为0

|

| ADREG | 选择AD流水线寄存器的数量。 |

| ALUMODEREG | 选择ALUMODE输入寄存器的数量。 |

| AREG | 选择A输入寄存器的数量。 选择1时,使用A2寄存器。 |

| BCASCREG | 与BREG一起,选择B级联路径BCOUT上的B输入寄存器的数量。 此属性必须等于或小于BREG值: BREG = 0: BCASCREG must be 0 |

| BREG | 选择B输入寄存器的数量。 选择1时,使用B2寄存器。 |

| CARRYINREG | 选择结构(fabric)CARRYIN输入寄存器的数量。 |

| CARRYINSELREG | 选择CARRYINSEL输入寄存器的数量。 |

| CREG | 选择C输入寄存器的数量。 |

| DREG | 选择D输入寄存器的数量 |

| INMODEREG | 选择INMODE输入寄存器的数量 |

| MREG | 选择M流水线寄存器的数量 |

| OPMODEREG | 选择OPMODEREG输入寄存器的数量 |

| PREG | 选择P输出寄存器的数量(也由CARRYOUT / PATTERN_DETECT / CARRYCASCOUT / MULTSIGNOUT等使用)。 |

| Feature Control Attributes | |

| A_INPUT | 选择并行输入(DIRECT)之间的A端口输入或前一个切片(CASCADE)的级联输入 |

| B_INPUT | 选择并行输入(DIRECT)之间B端口的输入或前一个切片(CASCADE)的级联输入 |

| USE_DPORT | 确定是否使用预加法器和D端口。 |

| USE_MULT | 选择乘法器的用法。 仅使用加法器/逻辑单元时,设置为NONE以节省功耗。 DYNAMIC设置表示用户正在动态切换A * B和A:B操作,因此需要获得两个路径的最坏情况时序。 |

| USE_SIMD | 选择加法器/减法器的操作模式。 属性设置可以是一个48位加法器模式(ONE48),两个24位加法器模式(TWO24)或四个12位加法器模式(FOUR12)。 选择ONE48模式与Virtex-6器件DSP48操作兼容,实际上并不是真正的SIMD模式。 当模式设置为ONE48时,支持典型的乘法 - 加法运算。当选择TWO24或FOUR12模式时,不能使用乘法器,并且USE_MULT必须设置为NONE。 |

| Pattern Detector Attributes | |

| AUTORESET_PATDET | 如果在此时钟周期内发生了模式检测事件,则在下一个时钟周期自动复位P寄存器(累计值或计数器值)。 RESET_MATCH和RESET_NOT_MATCH设置可区分DSP48E1 Slice是否应在下一个周期自动复位P寄存器: if the pattern is matched |

| MASK | 该48位值用于在模式检测期间屏蔽掉某些位。 当MASK位设置为1时,忽略相应的模式位。 当MASK位设置为0时,比较模式位。 |

| PATTERN | 该48位值用于模式检测器。 |

| SEL_MASK | 选择要用于模式检测器的掩码。 C和MASK设置用于模式检测器的标准用途(计数器,溢出检测等)。 ROUNDING_MODE1(C-bar左移1)和ROUNDING_MODE2(C-bar左移2)选择基于可选的寄存器C端口的特殊掩码。 这些舍入模式可用于使用模式检测器在DSP48E1切片中实现收敛舍入。 |

| SEL_PATTERN | 选择模式字段的输入源。 输入源可以是48位动态“C”输入或48位静态属性字段。 |

| USE_PATTERN_DETECT | 选择是使用模式检测器和相关功能(PATDET)还是不使用(NO_PATDET)。 此属性仅用于速度指定和模拟模型。 |

| Table 2-4: Internal Register Descriptions | |

| Register | Description and Associated Attribute |

| 2-Deep A Registers | 这两个A输入的可选寄存器由AREG选择,分别由CEA1和CEA2使能,并由RSTA同步复位。 |

| 2-Deep B Registers | 这两个用于B输入的可选寄存器由BREG选择,分别由CEB1和CEB2使能,并由RSTB同步复位。 |

| AD Register | 该可选预加法结果的寄存器由ADREG选择,由CEAD使能,并由RSTD同步复位。 |

| ALUMODE Register | ALUMODE控制信号的可选流水线寄存器由ALUMODEREG选择,由CEALUMODE启用,并由RSTALUMODE同步复位。 |

| C Register | 该输入的可选寄存器由CREG选择,由CEC使能,并由RSTC同步复位。 |

| CARRYIN Register | CARRYIN控制信号的可选流水线寄存器由CARRYINREG选择,由CECARRYIN启用,并由RSTALLCARRYIN同步复位。 |

| CARRYINSEL Register | CARRYINSEL控制信号的可选流水线寄存器由CARRYINSELREG选择,由CECTRL启用,并由RSTCTRL同步复位。 |

| D Register | 可选D预加器输入的寄存器由DREG选择,由CED使能,并由RSTD同步复位。 |

| INMODE Register | 该5位寄存器选择预加法器及其模式,以及馈送乘法器的A寄存器的符号和源。 该寄存器由INMODEREG选择,由CEINMODE使能,并由RSTINMODE同步复位。 |

| Internal Mult Carry Register | 内部进位信号的此可选流水线寄存器(仅用于乘法对称舍入)由CEM启用,并由RSTM同步复位。 |

| M Register | 用于乘法器输出的这个可选流水线寄存器由两个43位部分乘积组成。 这两个部分结果( two partial products)输入到X和Y多路复用器中,最后输入到加法器/减法器中以创建product输出。 M寄存器由MREG选择,由CEM使能,并由RSTM同步复位。 |

| OPMODE Register | OPMODE控制信号的可选流水线寄存器由OPMODEREG选择,由CECTRL启用,并由RSTCTRL同步复位。 |

| Output Registers | PEG,OVERFLOW,UNDERFLOW,PATTERNDETECT,PATTERNDETECT和CARRYOUT输出的可选寄存器由PREG选择,由CEP启用,并由RSTP同步复位。 同一个寄存器还输出PCOUT,CARRYCASCOUT和MULTSIGNOUT,它们是下一个DSP48E1 Slice的级联输出 |

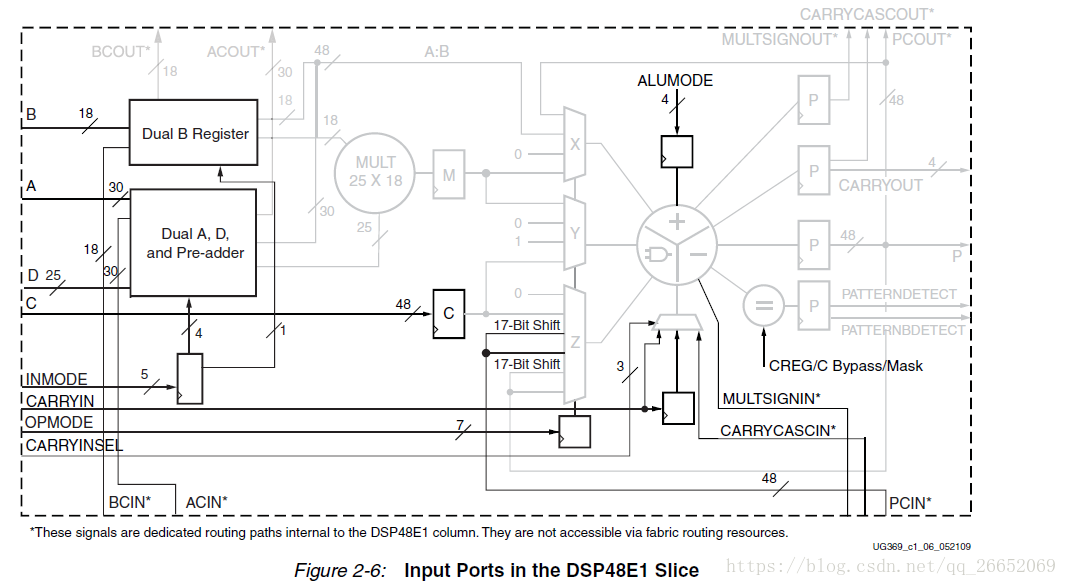

2.4.2 Input Ports

A,B,C,CARRYIN,CARRYINSEL,OPMODE,BCIN,PCIN,ACIN,ALUMODE,CARRYCASCIN,MULTSIGNIN以及相应的时钟使能输入和复位输入是传统端口。 D和INMODE端口是DSP48E1 Slice独有的。

本节详细介绍DSP48E1 Slice的输入端口。 DSP48E1 Slice的输入端口如图2-6所示。

A, B, C, and D Ports

DSP48E1 Slice输入数据端口支持许多常见的DSP和数学算法。 DSP48E1 Slice有四个标记为A,B,C和D的直接输入数据端口.A数据端口为30位宽,B数据端口为18位宽,C数据端口为48位宽,且预先加法器D数据端口为25位宽。

A端口的其中25位(A [24:0])和B端口的全部18位,为25位×18位二进制补码乘法器提供输入数据。通过独立的C端口,每个DSP48E1 Slice都能够进行乘加,乘减和 Multiply-Round 运算。

串联的A和B端口(A:B)绕过乘法器并馈送X多路复用器输入即 30位A输入端口构成A:B级联数据路径的高30位,18位B输入端口构成A:B数据路径的低18位。

倘若不使用乘法器(即将USE_MULT设置为NONE或DYNAMIC来实现的0,A:B数据通路与C输入端口一起使每个DSP48E1 Slice能够实现完整的48位加法器/减法器。

每个DSP48E1 Slice还具有两个级联输入数据路径(ACIN和BCIN),在相邻的DSP48E1 Slice之间提供级联输入流。级联路径对于A输入为30位宽,对于B输入为18位宽。受益于此功能的应用包括FIR滤波器,复数乘法,多精度乘法和复杂MACC。

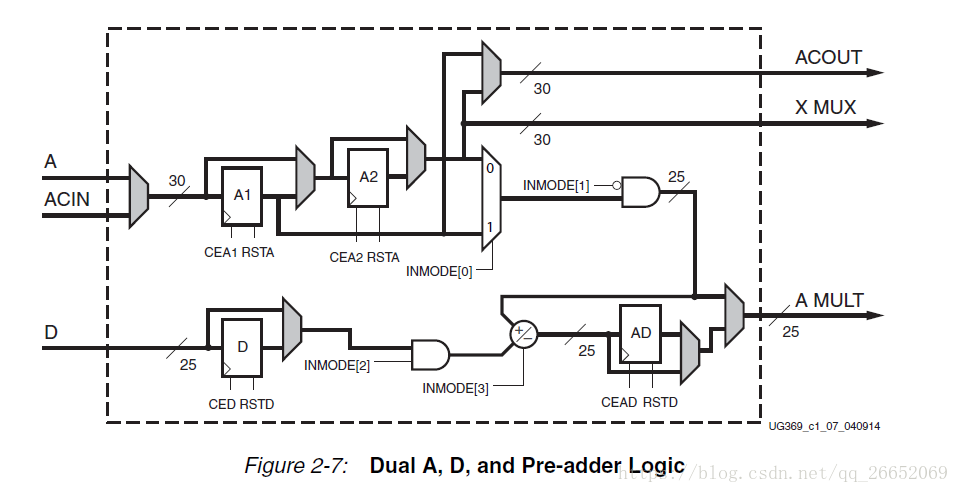

A和B输入端口以及ACIN和BCIN级联端口在其数据路径中可以具有0,1或2个流水线级。双A,D和预加法器端口逻辑如图2-7所示。

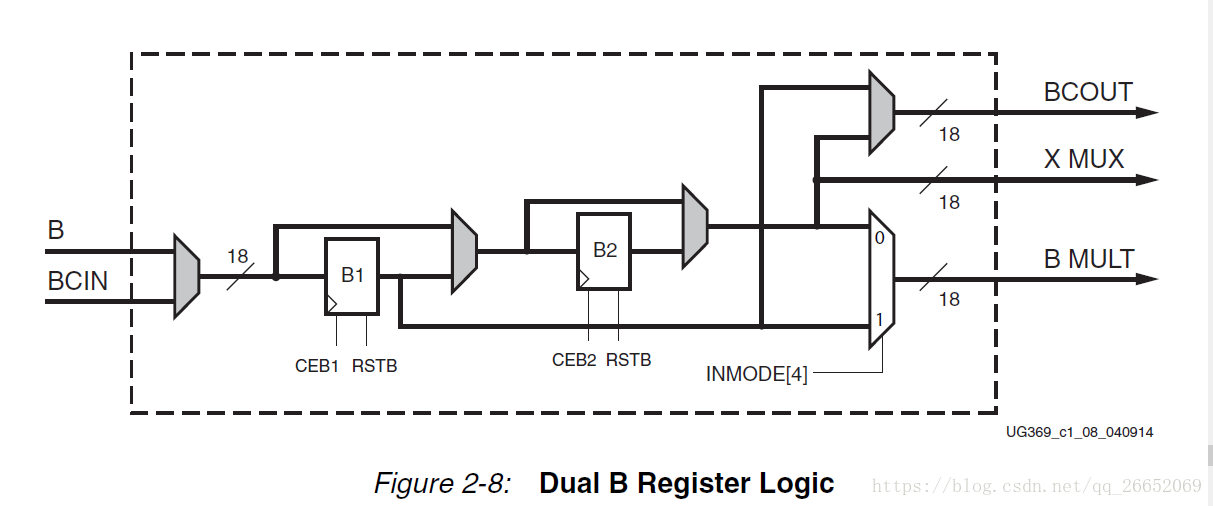

双B寄存器端口逻辑如图2-8所示。使用属性设置不同的pipestages。属性AREG和BREG用于选择A和B直接输入的流水线级数(设置几个寄存器)。属性ACASCREG和BCASCREG选择ACOUT和BCOUT级联数据路径中的流水线级数。允许的属性设置如上述表2-3所示。多路复用器是由配置位控制从而选择流经的路径,可选寄存器或级联输入。数据端口寄存器允许用户通常权衡增加的时钟频率(即,更高的性能)与数据等待时间。

下表2-5显示了INMODE [3:0]控制位的编码。 这些位用来选择预加器,A和D输入寄存器的功能。 必须将USE_DPORT属性设置为TRUE才能启用表2-5中所述的预加器功能。 用于选择B1还是B2的INMODE [4]如表2-6所示。

总之,INMODE和USE_DPORT属性控制预乘法器功能以及乘法器之前的A,B和D寄存器总线多路复用器。 如果未使用预加法器,则默认值USE_DPORT为FALSE。

表2-5:INMODE [3:0]功能(当AREG = 1或2时)

| INMODE[3] | INMODE[2] | INMODE[1] | INMODE[0] | USE_DPORT | Multiplier A Port |

| 0 | 0 | 0 | 0 | FALSE | A2 |

| 0 | 0 | 0 | 1 | FALSE | A1 |

| 0 | 0 | 1 | 0 | FALSE | Zero |

| 0 | 0 | 1 | 1 | FALSE | Zero |

| 0 | 0 | 0 | 0 | TRUE | A2 |

| 0 | 0 | 0 | 1 | TRUE | A1 |

| 0 | 0 | 1 | 0 | TRUE | Zero |

| 0 | 0 | 1 | 1 | TRUE | Zero |

| 0 | 1 | 0 | 0 | TRUE | D + A2 |

| 0 | 1 | 0 | 1 | TRUE | D + A1 |

| 0 | 1 | 1 | 0 | TRUE | D |

| 0 | 1 | 1 | 1 | TRUE | D |

| 1 | 0 | 0 | 0 | TRUE | -A2 |

| 1 | 0 | 0 | 1 | TRUE | -A1 |

| 1 | 0 | 1 | 0 | TRUE | Zero |

| 1 | 0 | 1 | 1 | TRUE | Zero |

| 1 | 1 | 0 | 0 | TRUE | D – A2 |

| 1 | 1 | 0 | 1 | TRUE | D – A1 |

| 1 | 1 | 1 | 0 | TRUE | D |

| 1 | 1 | 1 | 1 | TRUE | D |

Notes:

1.设置D和A1 / A2端口上的数据,使不支持饱和的预加器不会上溢或下溢。 参见预加法器,page 40。

结合Figure2-7

- INMODE [0],用于选择A1(INMODE [0] = 1)或A2(INMODE [0] = 0)。

- INMODE [1] = 1时,强制将预加法器的A输入设为0。

- INMODE [2] = 0时,强制预加法器的D输入为0。

- INMODE [3]提供预加法减法控制,其中INMODE [3] = 1表示减法,INMODE [3] = 0表示加法。

- INMODE [4]选择乘法器B端口,参见Figure-2-8,如下表2-6所示。

Table 2-6: INMODE[4] Encoding (when BREG = 1 or 2)

| INMODE[4] | Multiplier B Port |

| 0 | B2 |

| 1 | B1 |

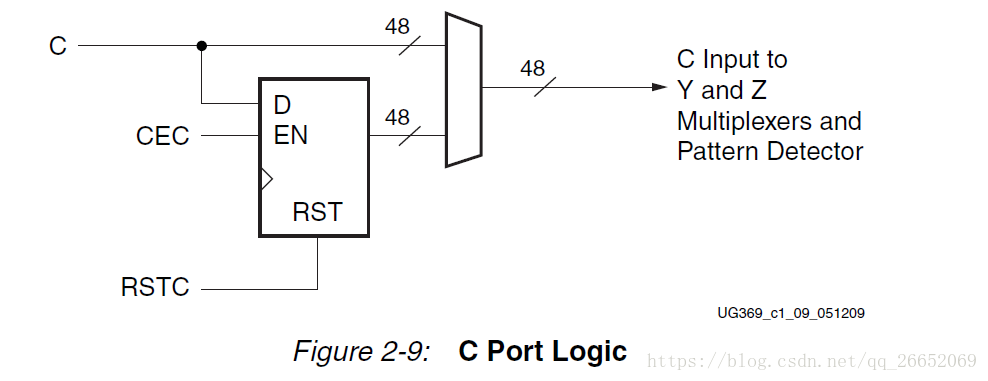

48位C端口用作多路复用器的通用输入即Y输入和Z输入,以执行加,减,三输入加/减和逻辑功能。 C输入还连接到模式检测器,用于舍入功能实现。 C端口逻辑如图2-9所示。 CREG属性选择C输入数据路径的流水线级数。

OPMODE, ALUMODE, and CARRYINSEL Port Logic

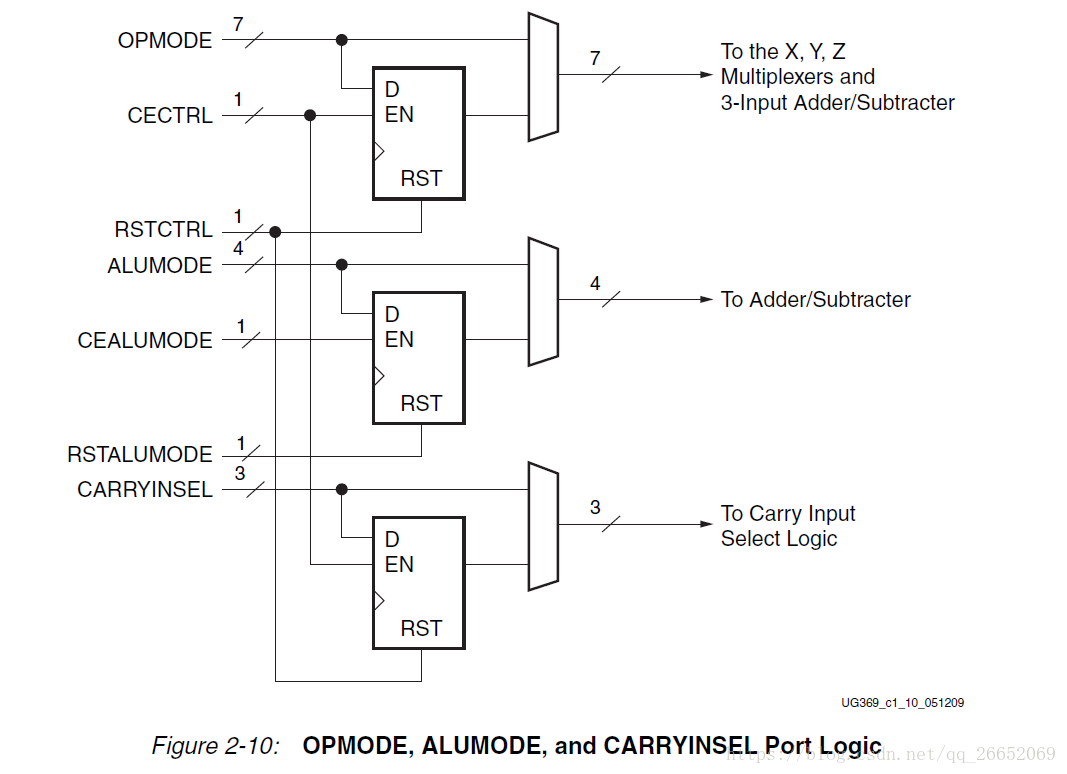

OPMODE,ALUMODE和CARRYINSEL端口逻辑支持流通或寄存输入控制信号。 由配置位控制的多路复用器用于选择流通或可选寄存器。 控制端口寄存器允许用户在增加的时钟频率(即更高的性能)与数据延迟之间进行权衡。 寄存器具有独立的时钟使能和复位功能。 OPMODE和CARRYINSEL寄存器由RSTCTRL复位。 ALUMODE由RSTALUMODE重置。 时钟使能,OPMODE,ALUMODE和CARRYINSEL端口逻辑如图2-10所示。

X, Y, and Z Multiplexers

OPMODE(操作模式)控制输入包含用于X,Y和Z多路复用器选择的字段。

OPMODE输入为您提供了一种从时钟周期到时钟周期动态更改DSP48E1功能的方法(例如,相对于给定的计算序列更改DSP48E1片的内部数据路径配置)。

可以使用OPMODEREG属性(如表2-3中所示)选择性地寄存OPMODE位(缓存)。

表2-7,表2-8和表2-9列出了OPMODE的可能值以及三个多路复用器(X,Y和Z多路复用器)输出端的结果函数。 多路复用器输出为以下加法器/减法器提供三个操作数。 并非允许多路复用器选择位的所有可能组合。 有些在表格中标记为“非法选择”,并给出未定义的结果。 如果选择乘法器输出,则X和Y多路复用器都用于将乘法器部分乘积提供给加法器/减法器。

| Z OPMODE[6:4] | Y OPMODE[3:2] | X OPMODE[1:0] | X Multiplexer Output | Notes |

| xxx | xx | 00 | 0 | 默认情况 |

| xxx | 01 | 01 | M | 必须选择OPMODE [3:2] = 01 |

| xxx | xx | 10 | P | 必须选择PREG = 1 |

| xxx | xx | 11 | A:B | 48 bits wide |

| Z OPMODE[6:4] | Y OPMODE[3:2] | X OPMODE[1:0] | Y Multiplexer Output | Notes |

| xxx | 00 | xx | 0 | 默认 |

| xxx | 01 | 01 | M | 必须选择OPMODE [1:20 = 01 |

| xxx | 10 | xx | 48'FFFFFFFFFFFF | 主要用于X和Z多路复用器上的逻辑单元按位操作 |

| xxx | 11 | xx | C |

| Z OPMODE[6:4] | Y OPMODE[3:2] | X OPMODE[1:0] | Z Multiplexer Output | Notes |

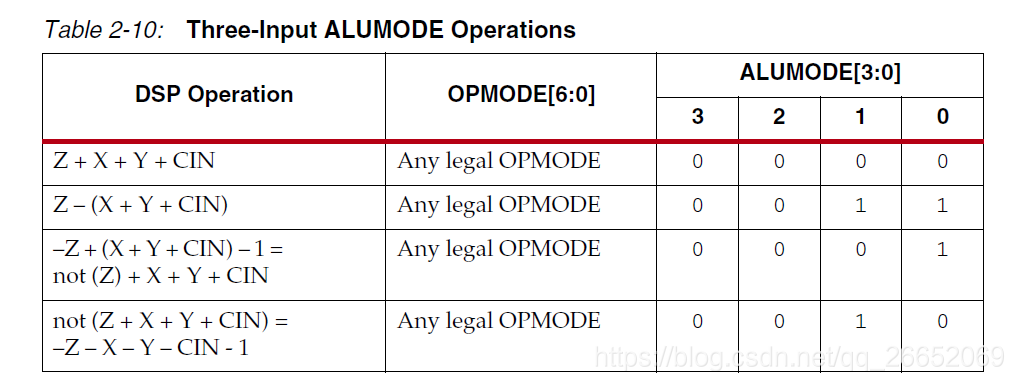

ALUMODE Inputs

4位ALUMODE控制第二级add / sub / logic单元的行为。

- ALUMODE = 0000选择Z +(X + Y + CIN)形式的添加操作。 CIN是CARRYIN多路复用器的输出(见图2-11)。

- ALUMODE = 0011,选择Z-(X + Y + CIN)形式的减法运算。

- ALUMODE = 0001,可以实现-Z +(X + Y + CIN)-1。

- ALUMODE = 0010,可以实现 - (Z + X + Y + CIN)-1,相当于不(Z + X + Y + CIN)。

通过执行按位求逆并加1,例如-k = not(k)+ 1,可以获得二进制补码的负数。其他减法和逻辑运算也可以通过增强实现

添加/子/逻辑单元。 见表2-10

Notes:

1.二进制补码:-Z = not(Z)+ 1有关双输入ALUMODE操作和第A-3页,第56页,请参见表2-13,第42页。

未完待续。。。。。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?