一、arm 的 PSRs

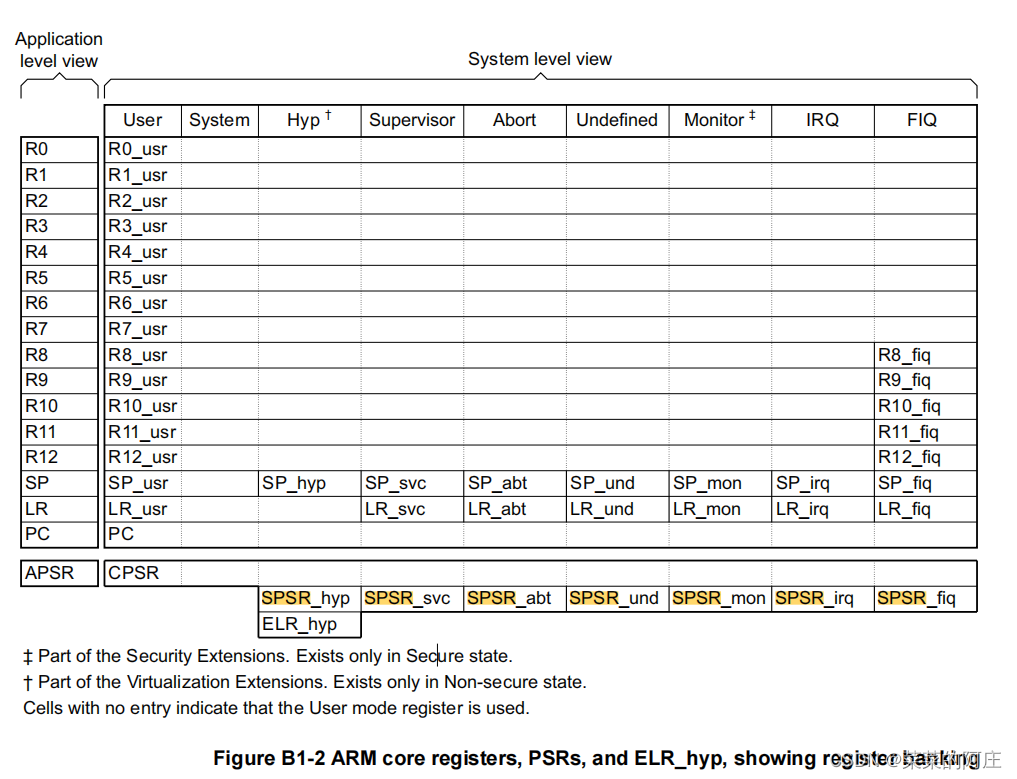

arm 中有很多程序状态寄存器(Program Status Registers,PSRs)用于存储处理器的状态信息,包括 CPSR\SPSR\FPSR\APSR 等:

- CPSR(Current Program Status Register):当前程序状态寄存器,用于存储当前程序的状态信息,包括处理器模式、条件码、中断使能状态等。

- SPSR(Saved Program Status Register):保存程序状态寄存器,用于保存异常处理程序执行前的状态,以确保异常处理程序执行完毕后能够正确地返回到原来的程序状态。每个异常模式都有对应的 SPSR。

- APSR(Application Program Status Register):应用程序状态寄存器,用于存储特定于应用程序的状态信息。在 ARMv7-M 架构中,APSR 包含了条件码和标志位。

二、CPSR

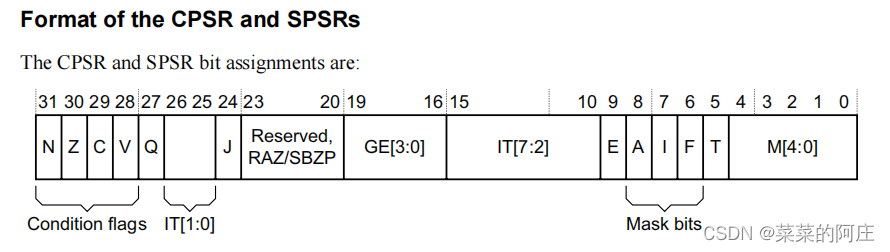

The Current Program Status Register (CPSR),当前程序状态寄存器,寄存器格式如下:

存储了以下处理器状态和控制信息:

- APSR(N Z C V Q GE),存储特定于应用程序的状态信息,在下面 APSR 中详细介绍;

- 程序指令集信息,bit24 J 和 bit5 T 的不同组合,区分 ARM\Thumb\Jazelle\ThumbEE 不同的指令集;

- IT 保存了 Thumb 的 IT 指令的 If-Then 执行状态;

- E 保存了大小端信息;

- M 保存了 ARM 的处理器模式(usr\fiq\irq\svc\mon\abt\hyp\und\sys);

- A I F (Abort\IRQ\FIQ)是中断和异常的使能 bit 位;

2.1 CPSR_cxsf

为了防止在某些操作 CPSR 寄存器的场景中,误操作其它 bit 位,CPSR(PSRs,其它状态寄存器也都具备这个功能)有 c x s f 几个不同的字段指代不同的 bit 位。

- c:control 字段,PSR[7:0] bit 位;

- x:extension 字段,PSR[15:8] bit 位;

- s:status 字段,PSR[23:16] bit 位;

- f:flag 字段,PSR[31:24] bit 位;

cxsf 字段可以任意单个或多个组合,例如 CPSR_c 指代只操作 CPSR 的低 8bit 位、CPSR_xs 指代只操作 CPSR 的[23:8] bit 位。

三、SPSR

The Saved Program Status Registers (SPSRs),程序状态保存寄存器,每个异常模式都有对应的 SPSR,是各个异常模式下 CPSR 的拷贝。

- 当进入某个异常,CPSR 会被拷贝到这个异常状态下的 SPSR 中;

- 当异常处理完成后,为了恢复导致回去的程序状态,将 SPSR restore 到 CPSR;

总的来说,CPSR 用于存储当前程序的状态,而 SPSR 则用于保存异常处理程序执行前的状态,以确保异常处理程序执行完毕后能够正确地返回到原来的程序状态。SPSR 在异常处理过程中起到了保护和恢复程序状态的作用。

四、APSR

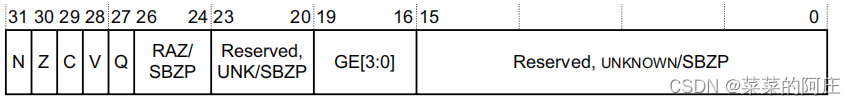

The Application Program Status Register (APSR),在 ARMv7-A,是 application level view 下的 CPSR,包含以下 bit 位:

- N(Negative):该位表示最近一条指令的运算结果是否为负数。当运算结果为负数时,N 位被设置为 1;否则,N 位被清零。

- Z(Zero):该位表示最近一条指令的运算结果是否为零。当运算结果为零时,Z 位被设置为 1;否则,Z 位被清零。

- C(Carry):该位用于处理无符号数运算中的进位。当运算产生了进位时,C 位被设置为 1;否则,C 位被清零。

- V(Overflow):该位用于处理带符号数运算中的溢出。当运算结果超出了有符号数的表示范围时,V 位被设置为 1;否则,V 位被清零。

- Q(Sticky Overflow):该位用于处理 SIMD(Single Instruction, Multiple Data)指令中的溢出情况。Q 位是一个粘性位,当 V 位被设置时,Q 位也会被设置,直到被显式清除。

- GE( The Greater than or Equal flags):意为大于等于,用于控制条件分支指令的执行。

2738

2738

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?