只发PCB电路相关27 随时更新~~ whaosoft aiot http://143ai.com

一、某大厂DCDC芯片PCB layout布局及设计

在DCDC电源电路中,PCB的布局对电路功能的实现和良好的各项指标来说都十分重要。本文以buck电路为例,简单分析一下如何进行合理PCB layout布局以及设计中的注意事项。如有问题,欢迎指正。

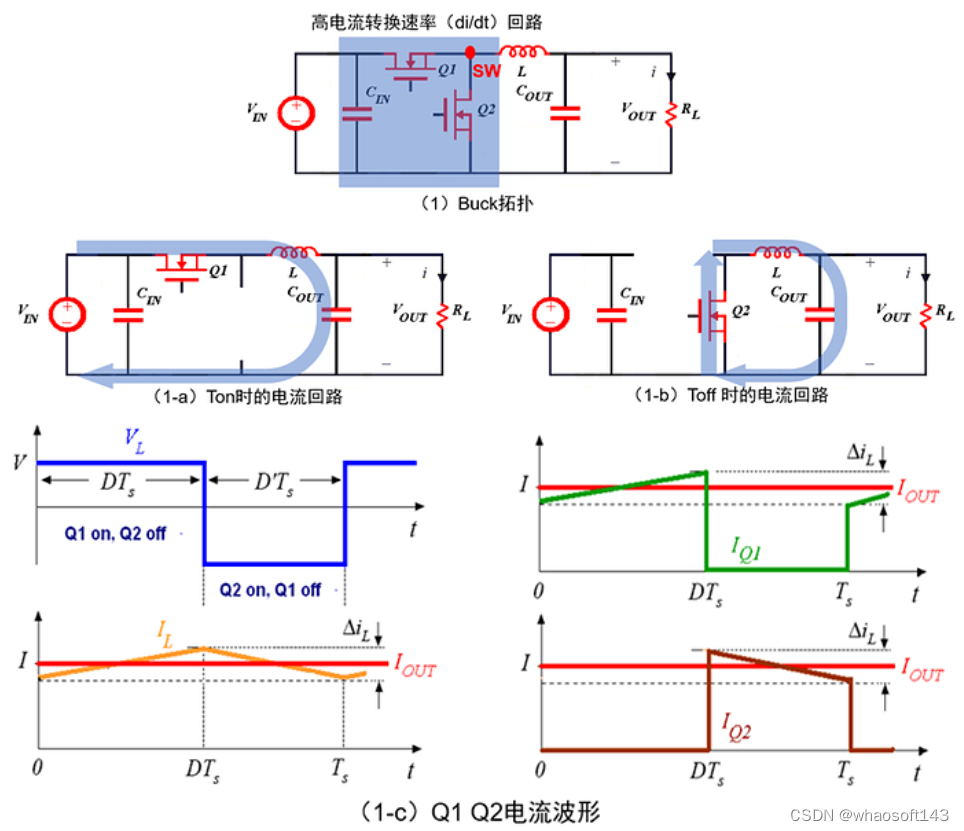

首先,以最简单的BUCK电路拓扑为例,下图(1-a)和(1-b)中分别标明了在上管开通和关断时刻电流的走向,即功率回路部分。这部分电路负责给用户负载供电,承受的功率较大。 结合图(1-c)中Q1和Q2的电流波形,不难发现,由于电感的存在,后半部分电路中不会存在一个较高的电流变化趋势,只有在两个开关管的部分会出现高电流转换速率。

结合图(1-c)中Q1和Q2的电流波形,不难发现,由于电感的存在,后半部分电路中不会存在一个较高的电流变化趋势,只有在两个开关管的部分会出现高电流转换速率。

在PCB布线时需要特别注意,尽可能减小这一快速变化的环节的面积,来减少对其他部分的干扰。随着集成工艺的进步,目前大部分电源芯片都将上下管集成到了芯片的内部。

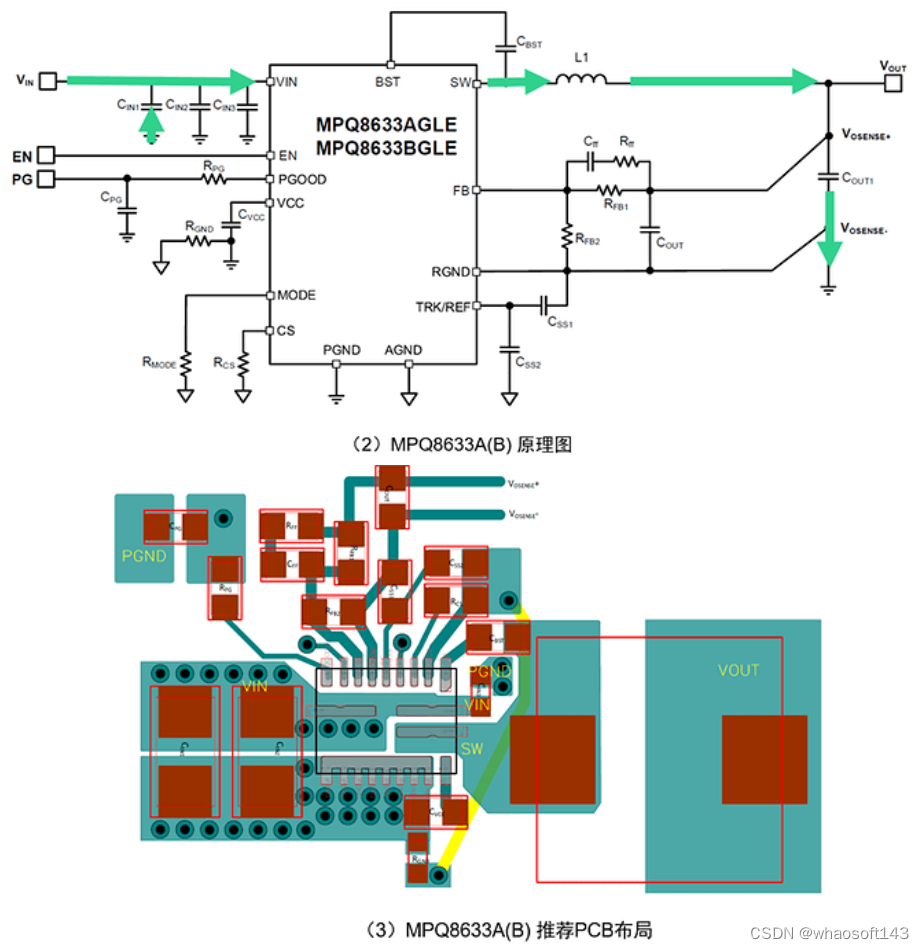

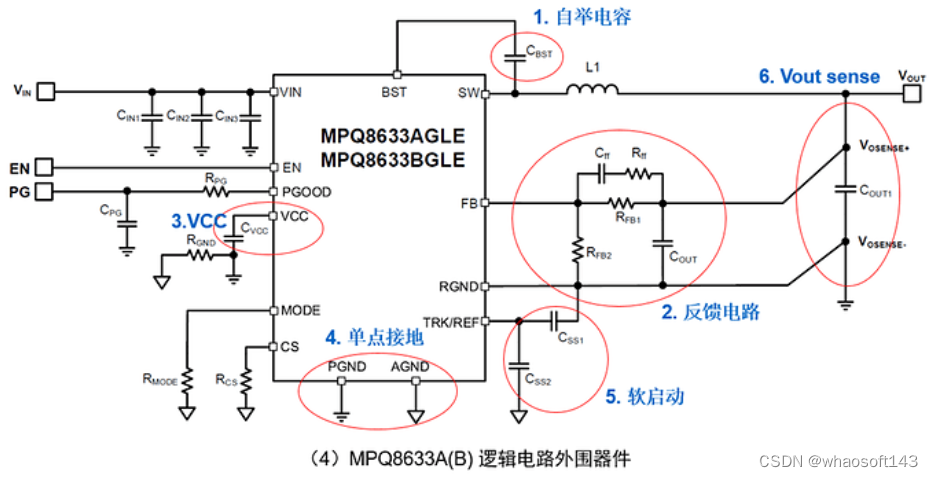

了解了高电流转换速率部分后,让我们回到整个功率回路布局来看。以MPS的非常受欢迎的MPQ8633A(B)系列产品为例,这是一款完全集成的高频同步降压转换器可以实现高达12-20A的输出电流,其原理图如下,其功率回路(绿色标注)中包含输入电容,电感以及输出电容等器件。 功率回路也需要做到尽可能地占用较小的环路面积,来减少噪声的发射以及回路上的寄生参数。推荐的PCB布局如图(3)所示。注意点如下:

功率回路也需要做到尽可能地占用较小的环路面积,来减少噪声的发射以及回路上的寄生参数。推荐的PCB布局如图(3)所示。注意点如下:

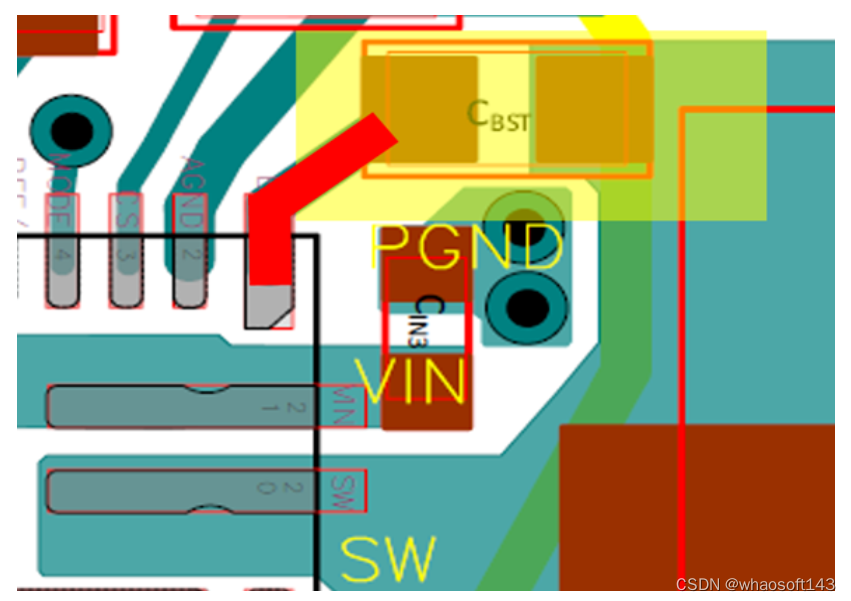

1、输入电容就近放在芯片的输入Vin 和功率地PGND ,减少寄生电感的存在,因为输入电流不连续,寄生电感引起的噪声对芯片的耐压以及逻辑单元造成不良影响。VIN 的管脚旁边至少各有1 个去耦电容 ,用来滤除来自电源输入端的交流噪声和来自芯片内部(倒灌)的电源噪声,同时也为芯片储能。且电容需要紧挨管脚,两者的间距需要小于40mil 。 2、功率回路尽可能的短粗,保持较小的环路面积 ,减少噪声的发射。

2、功率回路尽可能的短粗,保持较小的环路面积 ,减少噪声的发射。

3、SW 点是噪声源,保证电流的同时保持尽量小的面积 ,远离敏感的易受干扰的位置,例如FB等。

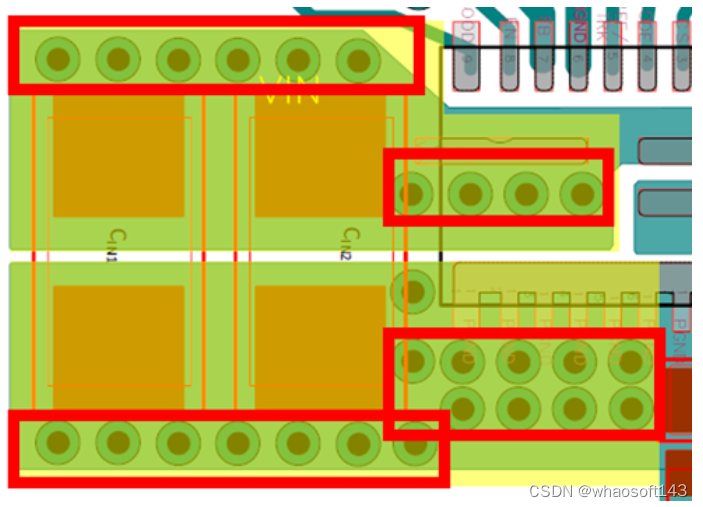

4、铺铜面积和过孔数量会影响到PCB 的通流能力和散热。 由于PCB的载流能力与PCB板材、板厚、导线宽厚度以及温升相关,较为复杂,可以通过IPC-2152标准来进行准确的查找和计算。一般,对于MPQ8633A(B)的PCB来说,需要在VIN(至少打6个过孔)和PGND(至少打9个过孔)处多打过孔,这两处的铺铜应最大化来减小寄生阻抗。SW处的铺铜也需要加宽,以免出现限流的情况,导致工作异常。 讨论完功率回路部分,转眼看芯片逻辑电路部分,这部分的PCB布局也是有所讲究的。

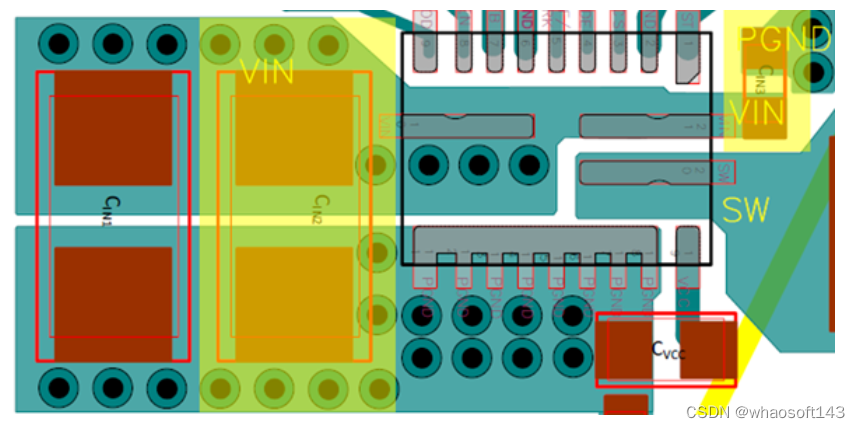

讨论完功率回路部分,转眼看芯片逻辑电路部分,这部分的PCB布局也是有所讲究的。 结合图(3)和(4)可总结注意点如下:

结合图(3)和(4)可总结注意点如下:

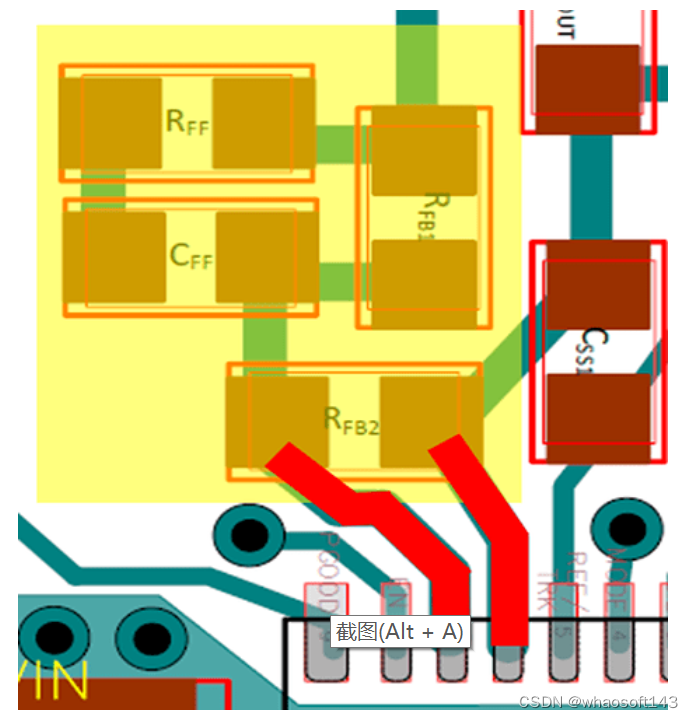

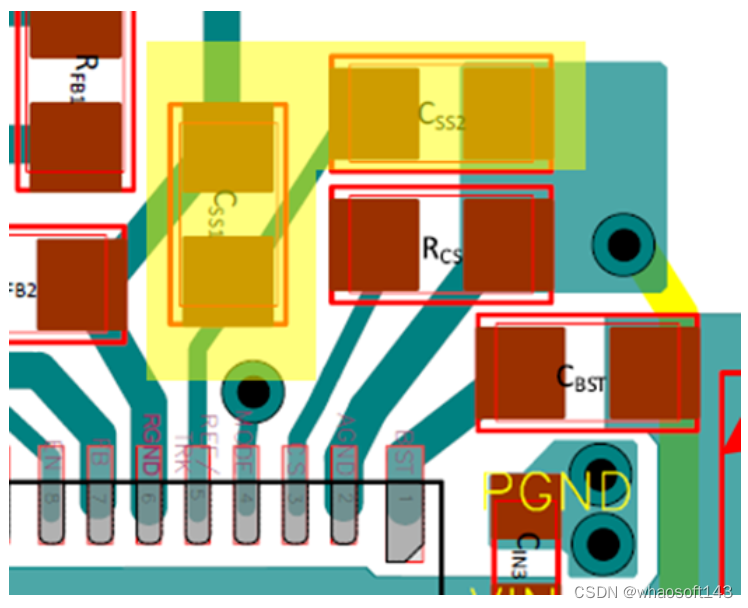

将BST 电容放置在尽可能靠近BST 和SW 的位置 ,使用20mil 或更宽 来布线路径。 FB 电阻连接到FB 管脚尽可能短, 减少噪声的耦合。这是芯片最敏感,最容易受干扰的部分,是引起系统不稳定的十分常见原因。需要将其远离噪声源,例如:SW点,电感,二极管等(在非同步buck中,MPQ8633外围无二极管)。如图,RFF、CFF、RFB1、RFB2都尽量靠近芯片摆放。

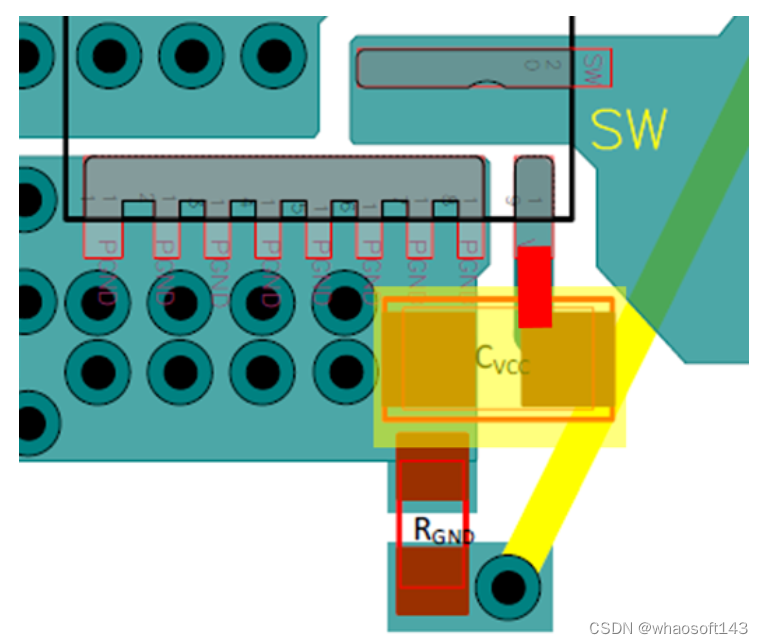

FB 电阻连接到FB 管脚尽可能短, 减少噪声的耦合。这是芯片最敏感,最容易受干扰的部分,是引起系统不稳定的十分常见原因。需要将其远离噪声源,例如:SW点,电感,二极管等(在非同步buck中,MPQ8633外围无二极管)。如图,RFF、CFF、RFB1、RFB2都尽量靠近芯片摆放。 VCC 电容应就近放置在芯片的VCC 管脚和芯片的信号地之间,尽量在一层,没有过孔 。对于信号地(AGND)和功率地(PGND)在一个管脚的芯片,同样就近和该管脚连接。

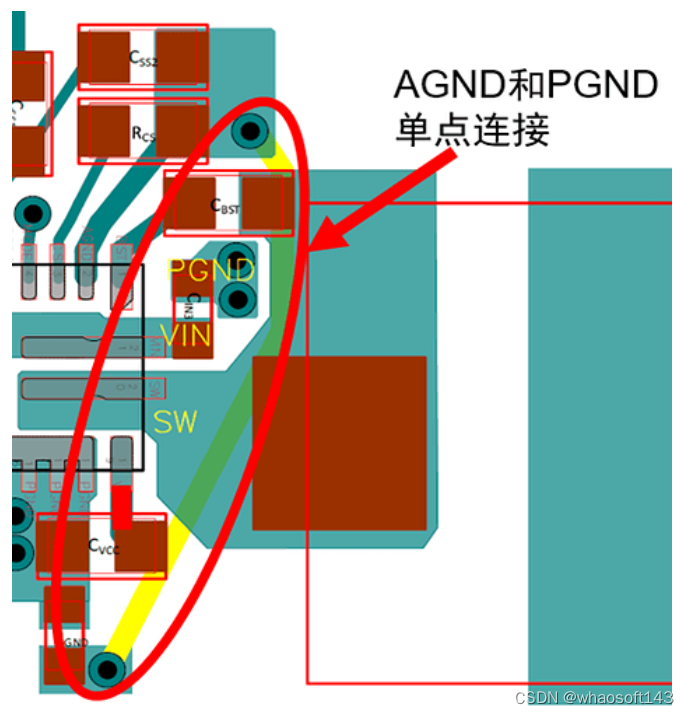

VCC 电容应就近放置在芯片的VCC 管脚和芯片的信号地之间,尽量在一层,没有过孔 。对于信号地(AGND)和功率地(PGND)在一个管脚的芯片,同样就近和该管脚连接。 AGND和PGND需要进行单点连接。

AGND和PGND需要进行单点连接。  将SS电容靠近TRK/REF至RGND 。

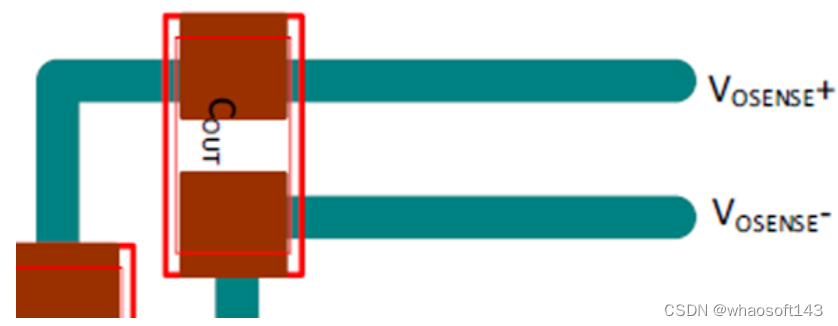

将SS电容靠近TRK/REF至RGND 。 将SENSE电容置于输出SENSE线之间,平行走线。

将SENSE电容置于输出SENSE线之间,平行走线。 PCB layout 中走线和铺铜都尽量避免90 °直角 ,走45°或者圆弧角,特别是在高频信号传输线部分。避免由传输线宽带来的反射和传输信号的失真。

PCB layout 中走线和铺铜都尽量避免90 °直角 ,走45°或者圆弧角,特别是在高频信号传输线部分。避免由传输线宽带来的反射和传输信号的失真。

最后,为了方便大家了解自己画的PCB是否合理,可以参考以下简易表格做一个自评:

以上表格适用于简单的buck、boost电路的PCB设计,多用单层或者双层板即可。

以上表格适用于简单的buck、boost电路的PCB设计,多用单层或者双层板即可。

二、Type C接口的PCB布局布线要求

USB Type C,又称为USB-C。需要注意的是,Type-C只是一种接口,和USB的版本没有任何关系。该接口的亮点在于更加纤薄的设计、更快的传输速度,即最高10Gbps以及更强悍的电力传输(最高100W)。

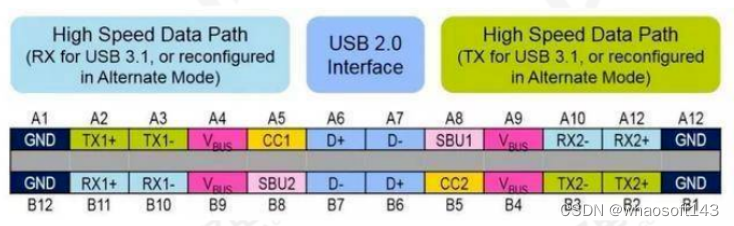

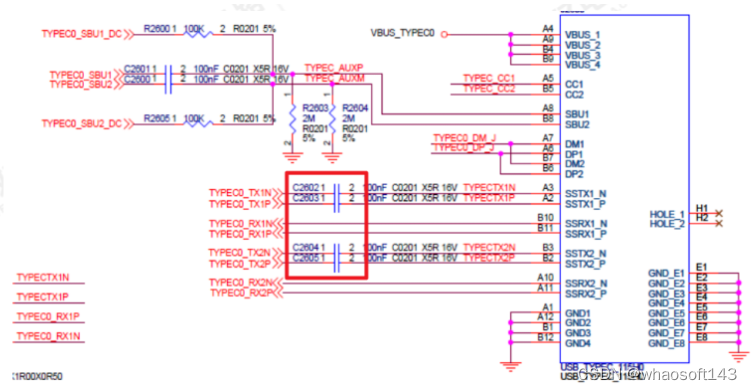

Type-C双面可插接口最大的特点的支持USB接口双面插入,主要面向更轻薄、更纤细的设备。如下图所示,为Type-C接口的管脚定义。

图1:Type C接口的管脚定义

图1:Type C接口的管脚定义

Type C接口的PCB设计要求:

1)ESD、共模电感器件靠近Type C接口,放置的顺序是ESD→共模电感→阻容;同样也要注意ESD和Type C的距离,留有一定的间距,考虑后焊情况。

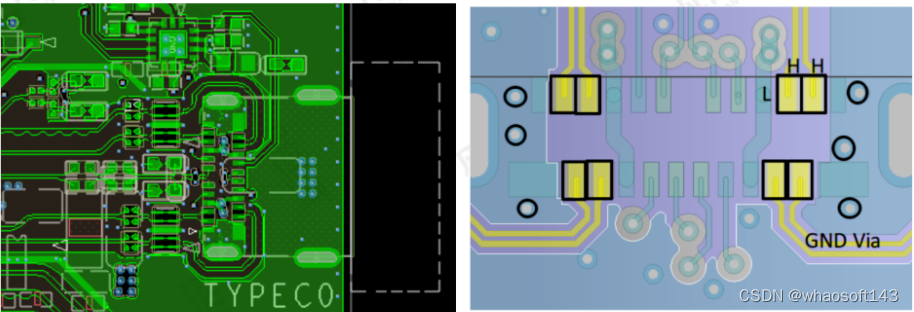

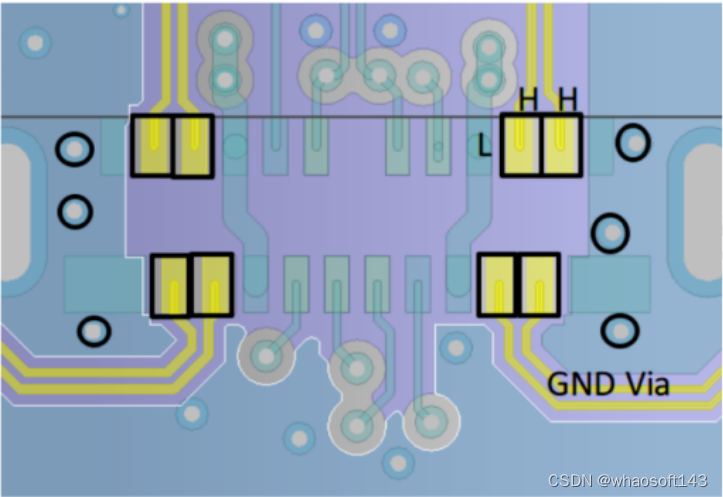

2)TX信号线的耦合电容应靠近接口放置,RX信号线的耦合电容由设备端提供,如图2所示:

图2:TX信号线的耦合电容

图2:TX信号线的耦合电容

3)Type C差分走线阻抗控制90ohm±10%,为了保证阻抗的连续性,应该有良好的参考平面和不跨分割,信号打孔换层时数量不超过2个。

4)Type-C有RX/TX1-2四组差分信号,两组D+/D-差分信号,一共六对差分线,差分信号线要求至少紧邻一个地平面,两侧都紧邻地平面最好,走线尽量短,走线最长不要超过6inchs。

5)保证Type C差分线长匹配,对内等长误差<6mil,等长按照差分等长规范。

6)保证Type C差分对于对间或者差分对于其他信号的影响,对内间距建议是大于等于4倍Type C线宽。与其他信号之间的间距保持尽量大于等于4倍Type C线宽。

7)CC1/CC2是两个关键引脚,作用很多:探测连接,区分正反面,区分DFP和UFP,也就是主从配置Vbus,走线时面要加粗处理。

图3:Type-C连接器布线示意

当Type-C连接器工作速率≥8Gbps时,请按照以下设计要求进行设计:

1)在连接器内走线要中心出线。如果高速信号在连接器有一端信号没有与GND相邻PIN时,设计时应在其旁边加GND孔。

2)如果接口的信号工作速率≥8Gbps,那么这些接口的连接器要能符合相应的标准要求(如HDMI2.1/DP1.4/PCI-E3.0协议标准)。推荐使用这些厂商的连接器:Molex、Amphenol、HRS等。

3)根据接口选择挖空一层或者两层地平面,如果挖空连接器焊盘正下方的L2地参考层,需隔层参考,即L3层要作为地参考层;如果挖空L2和L3的地参考层,那么L4层需要为地平面,作为隔层参考层。挖空尺寸需结合连接器型号并根据实际叠层通过仿真确定。

4)建议在连接器的每个地焊盘各打2个地通孔,且地孔要尽可能靠近焊盘。

下表给出了基于EVB一阶HDI叠层的挖空参考尺寸:

表1:连接器焊盘挖空尺寸参考值

连接器推荐布线方式:

图4:Type c连接器布线示意

三、经典运算放大器的应用电路分析

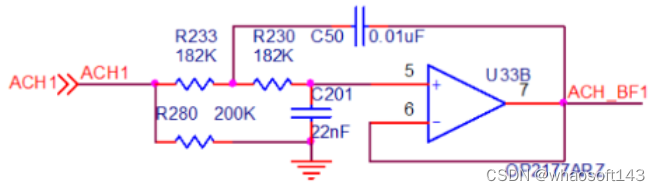

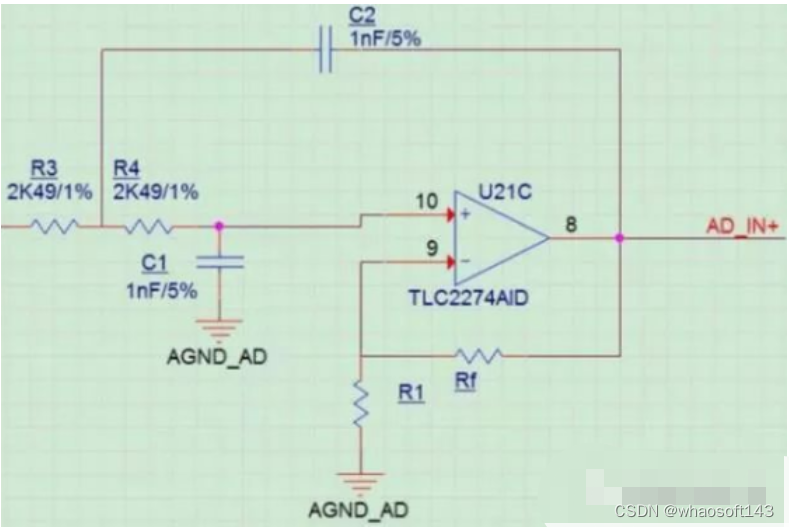

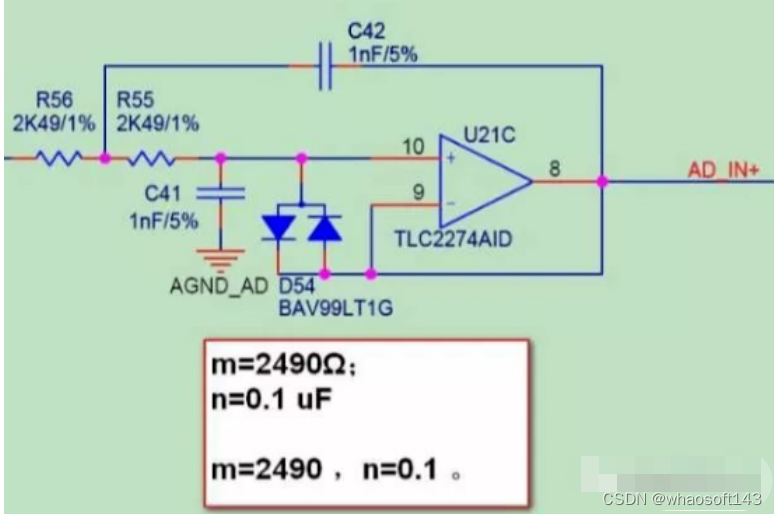

上图是典型的有源滤波电路(赛伦-凯 电路,是巴特沃兹电路的一种)。有源滤波的好处是可以让大于截止频率的信号更快速的衰减,而且滤波特性对电容、电阻的要求不高。

该电路的设计要点是:在满足合适的截止频率的条件下,尽可能将R233和R230的阻值选一致,C50和C201的容量大小选取一致(两级RC电路的电阻、电容值相等时,叫赛伦凯电路),这样就可以在满足滤波性能的情况下,将器件的种类归一化。其中电阻R280是防止输入悬空,会导致运放输出异常。

滤波最常用的3种二阶有源低通滤波电路为:巴特沃兹,单调下降,曲线平坦最平滑。

巴特沃兹低通滤波中用的最多的是赛伦凯乐电路,即仿真的该电路。

一个滤波器,要知道其截至频率是多少,或者能写出传递函数和频率响应也可以。如果该滤波器还有放大功能,要知道该滤波器的增益是多少。

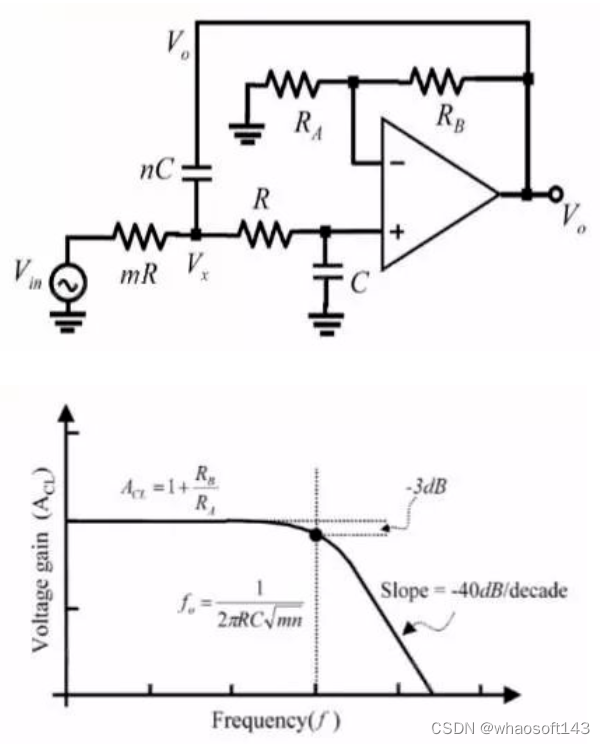

当两级RC电路的电阻、电容值相等时,叫赛伦凯电路,在二阶有源电路中引入一个负反馈,目的是使输出电压在高频率段迅速下降。

二阶有源低通滤波电路的通带放大倍数为 1+Rf/R1 ,与一阶低通滤波电路相同。如下两图分别是二阶Sallen-Key低通滤波器电路,及其振幅响应。

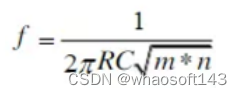

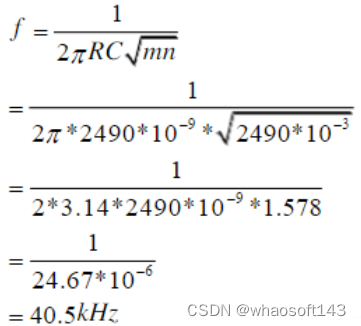

滤波器截止频率为:

注:m的单位为欧姆, n的单位为uF。

所以计算得出 截止频率为:

切比雪夫 ,迅速衰减,但通带中有纹波。

贝塞尔(椭圆),相移与频率成正比,群延时基本是恒定。

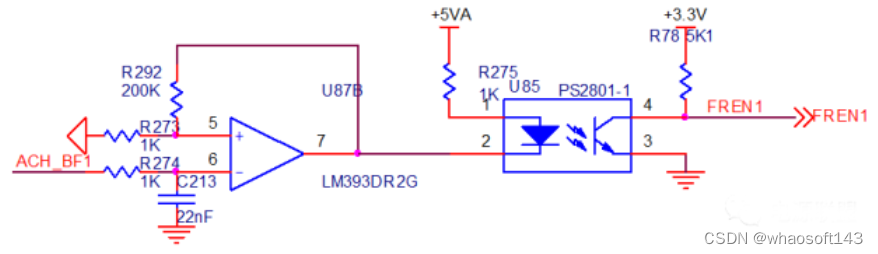

运放在电压比较器中的应用

电压比较

电压比较

上图是典型信号转换电路,将输入的交流信号,通过比较器LM393,将其转化为同频率的方波信号(存在反相,让软件处理一下就可以),该电路在交流信号测频中广泛使用。

该电路实际上是过零比较器和深度放大电路的结合。

将输出进行(1+R292/R273)倍的放大,放大倍数越高,方波的上升边缘越陡峭。

该电路中还有一个关键器件的阻值要注意,那就是R275,R275决定了方波的上升速度。

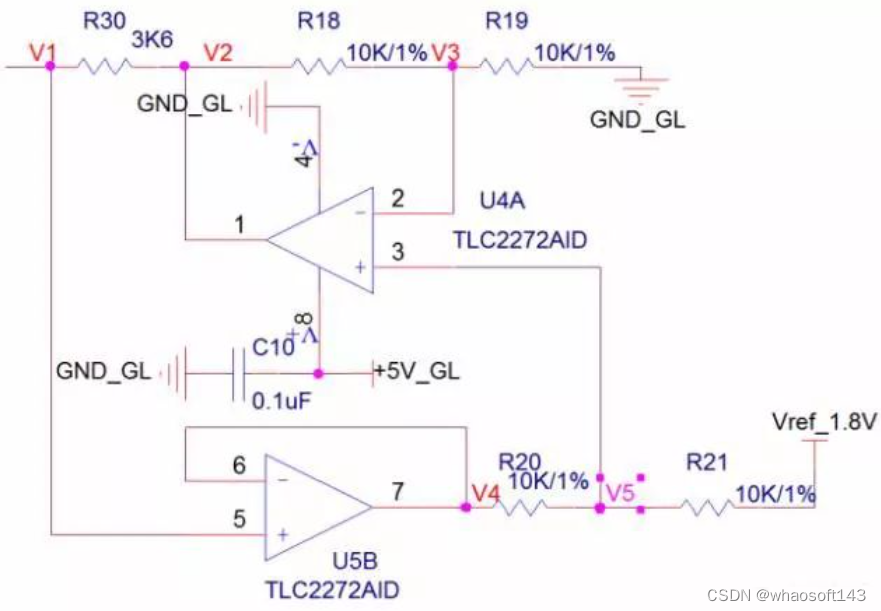

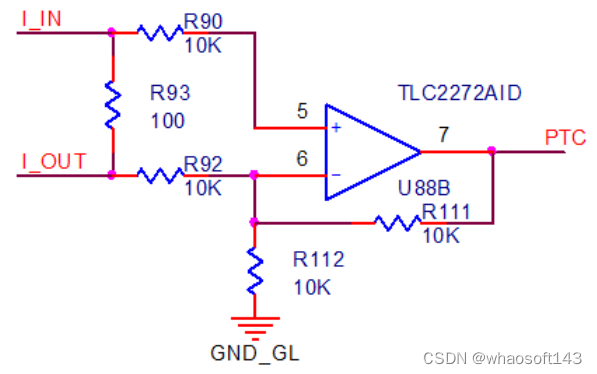

恒流源电路的设计

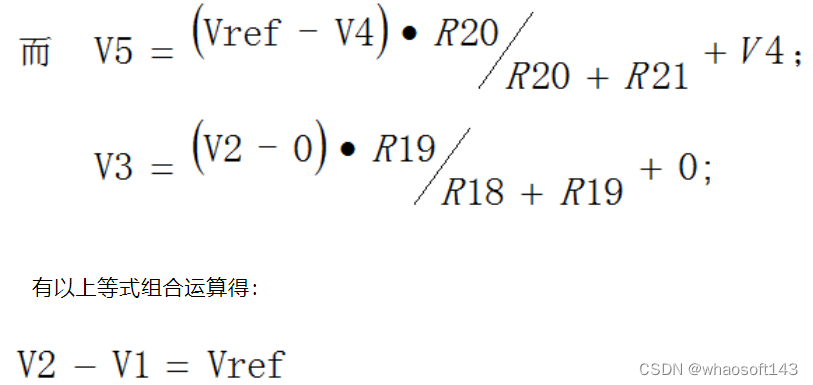

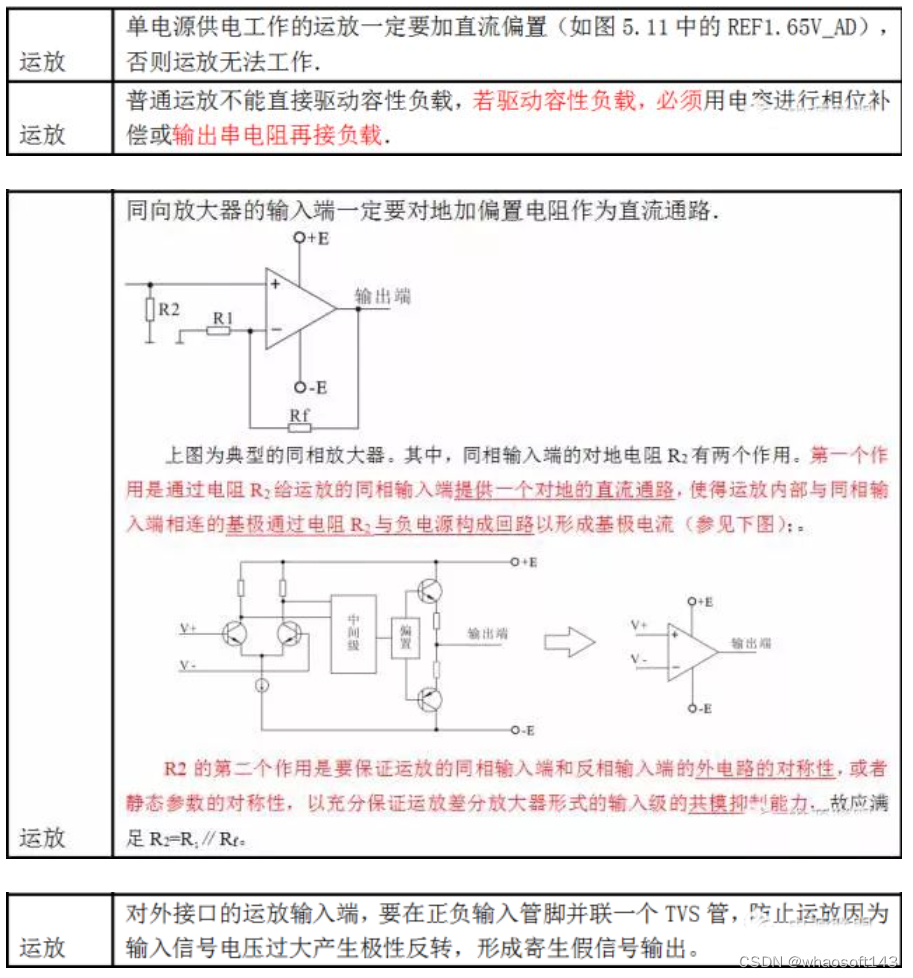

如图所示,恒流原理分析过程如下:

U5B(上图中下边的运放)为电压跟随器,故V1=V4。

由运算放大器的虚短原理,对于运放U4A(上图中上边的运放)有:V3=V5。

当参考电压Vref固定为1.8V时,电阻R30为3.6,电流恒定输出0.5mA。

当参考电压Vref固定为1.8V时,电阻R30为3.6,电流恒定输出0.5mA。

该恒流源电路可以设计出其他电流的恒流源,其基本思路就是:所有的电阻都需要采用高精度电阻,且阻值一致,用输入的参考电压(用专门的参考电压芯片)比上阻值,就是获得的输出电流。

但在实际使用中,为了保护恒流源电路,一般会在输出端串一只二极管和一只电阻,这样做的好处第一是防止外界的干扰会进入恒流源电路,导致恒流源电路的损坏,二是可以防止外界负载短路时,不至于对恒流源电路造成损坏。

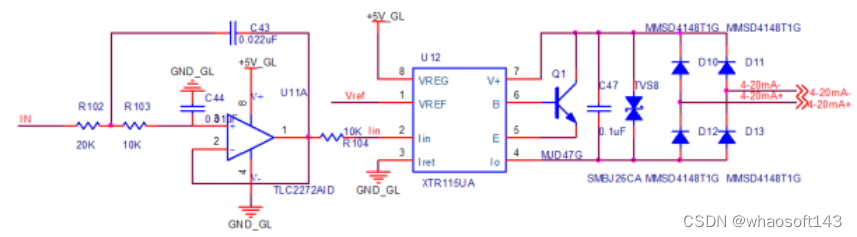

在整流电路中的应用

整流电路

上述电路是一个整流电路,将输入的一定频率的脉冲整流成固定的电平电压,再用此电压控制4-20mA电流的输出电流。该电路功能类似一些DAC功能的接口。

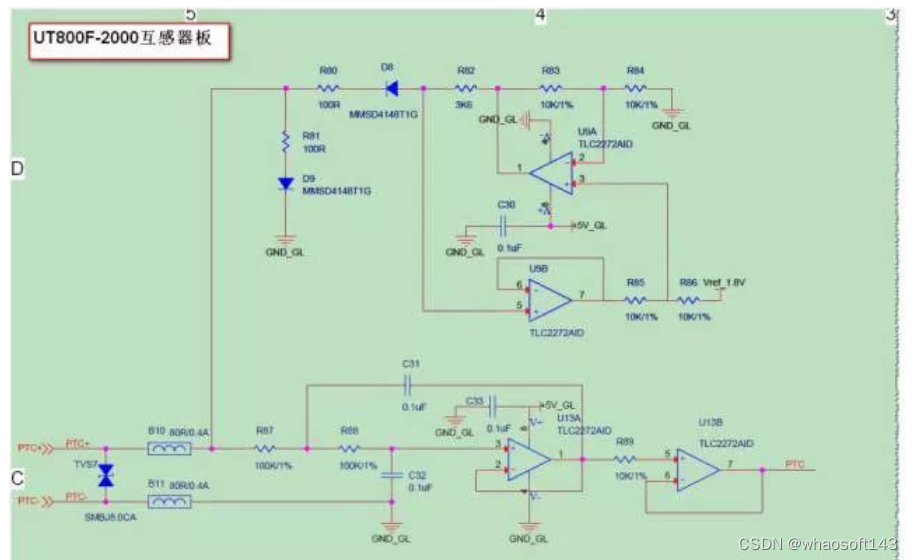

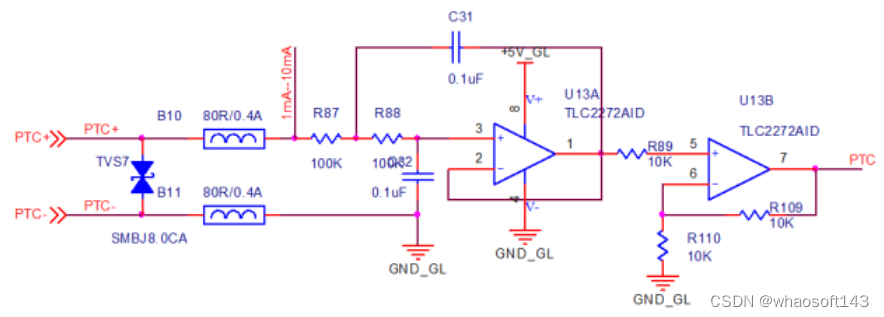

热电阻测量电路

上图的电路是典型的热电阻/电偶的测量电路,其测量思路为:将1-10mA的恒流源加于负载,将会在负载上产生一定的电压,将该电压进行有源滤波处理,处理后在进行信号的调整(信号放大或衰减),最后将信号送入ADC接口。

该电路应用时,要注意在输入端施加保护,可以并TVS,但要注意节电容对测量精度的影响,当然,如果在一些低成本场合,上述电路图可简化为如下电路。

电压跟随器

在运放的使用中,电压跟随器是一种常见的应用,该电路的好处是:一是减小负载对信号源的影响;二是提高信号带负载的能力。

上图是运用运放实现了电阻分压的功能,首先用电阻获得需要输出的电压,然后用运放对该电压进行跟随,提高其输出能力。

上图是运用运放实现了电阻分压的功能,首先用电阻获得需要输出的电压,然后用运放对该电压进行跟随,提高其输出能力。

单电源的应用

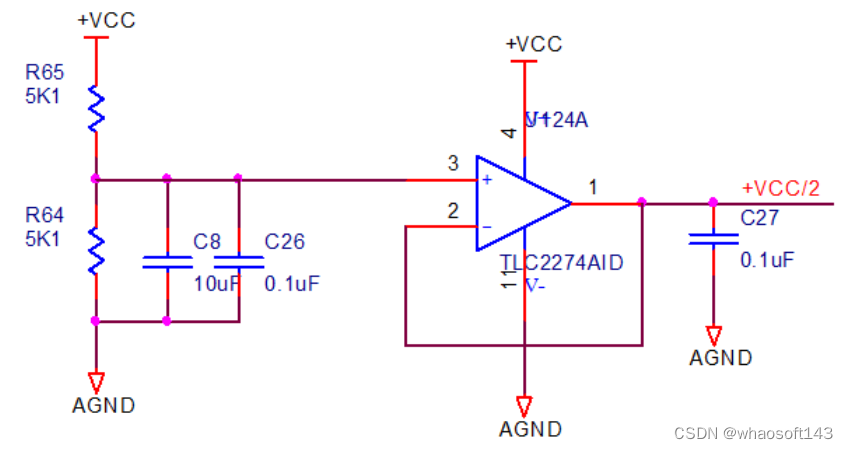

在运放的实际使用,我们一般为了保持运放的频率特性,一般都采用双电源供电,但有的时候在实际使用,我们只有单电源的情况,也能实现运放的正常工作。

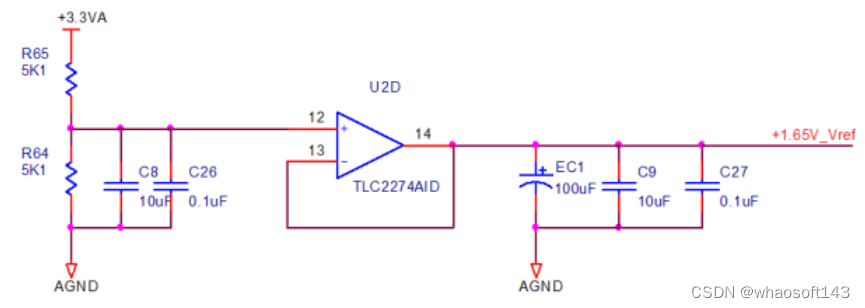

首先我们运用运放跟随电路,实现一个VCC/2的分压,电路如下。

当然,如果在要求不是很高的场合,我们可以直接电阻分压,获得+VCC/2,但由于电阻分压的特性所在,其动态的响应速度会非常慢,请谨慎使用。

当然,如果在要求不是很高的场合,我们可以直接电阻分压,获得+VCC/2,但由于电阻分压的特性所在,其动态的响应速度会非常慢,请谨慎使用。

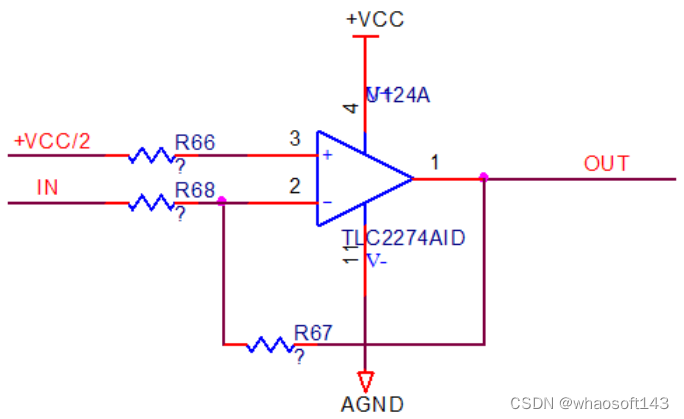

获得+VCC/2后,我们可以用单电源实现信号放大功能,如下图:

该电路中 R66=R67//R68, 信号的输出增益G=-R67/R68 。

该电路中 R66=R67//R68, 信号的输出增益G=-R67/R68 。

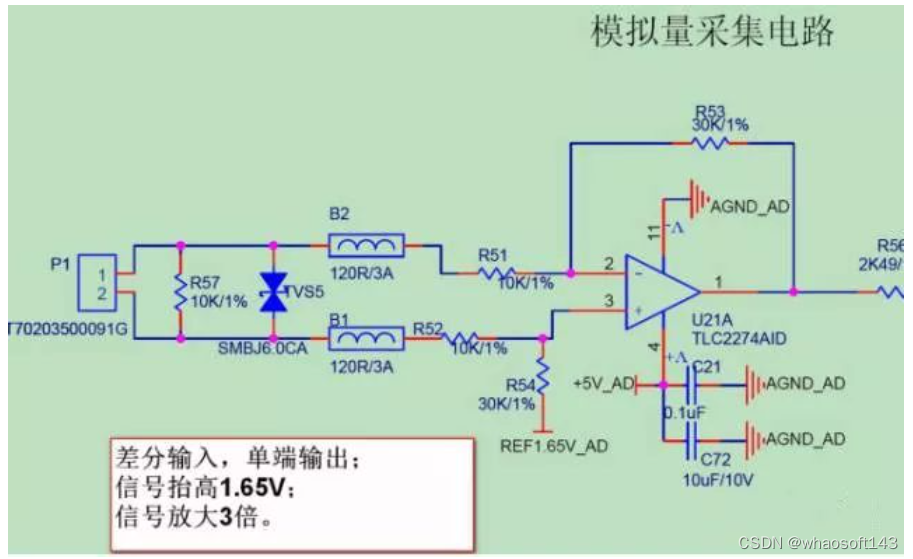

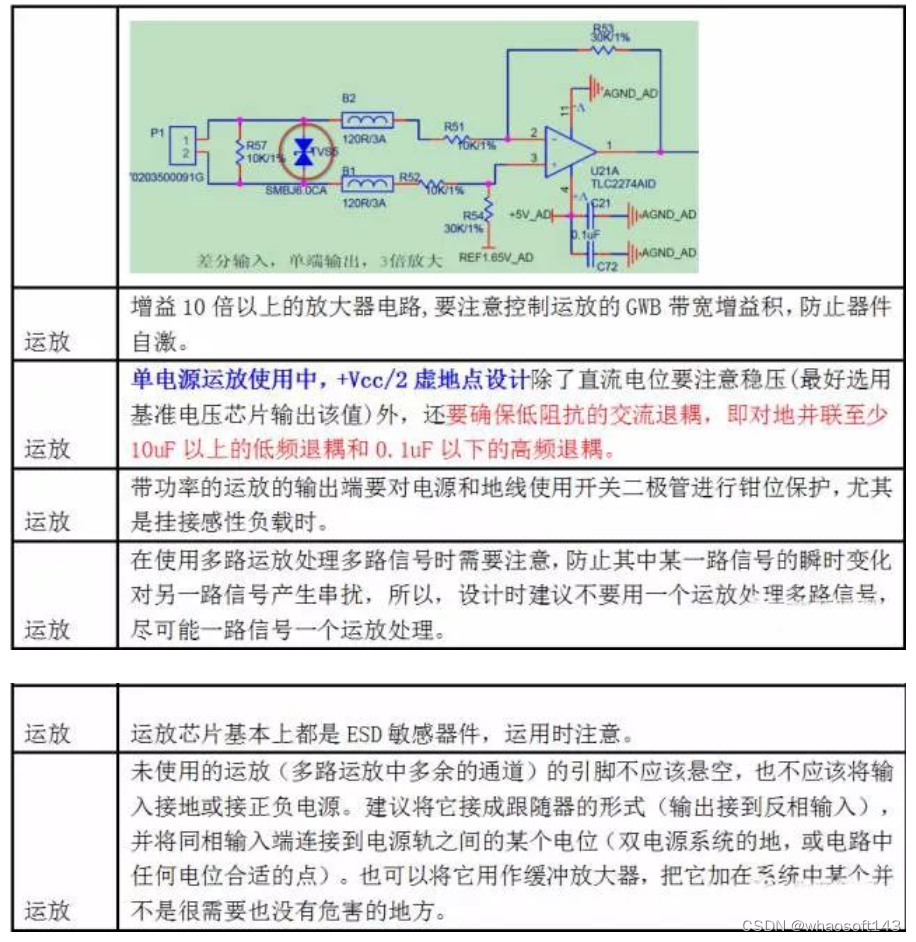

具体应用如下图:运放为单+5V_AD供电,AD芯片的电压是3.3V(基准电压芯片REF3033得到),该3.3V再电阻分压和经过运放跟随后得到1.65V,给到运放的同相输入端。

附:运放的应用要点

四、画好原理图的技巧

不光是代码有可读性的说法,原理图也有。很多时候原理图不仅仅是给自己看的,也会给其它人看,如果可读性差,会带来一系列沟通问题。所以,要养成良好习惯,做个规范的原理图。

此外,一个优秀的原理图,还会考虑可测试性、可维修性、BOM表归一化等。

1 分模块

如上图所示,用线把整张原理图划分好区域,和各个区域写上功能说明,如:电源、STM32等。

这样让人更清晰、更快速地理解整个原理图,调试、维修的时候也很容易根据问题来查找电路。

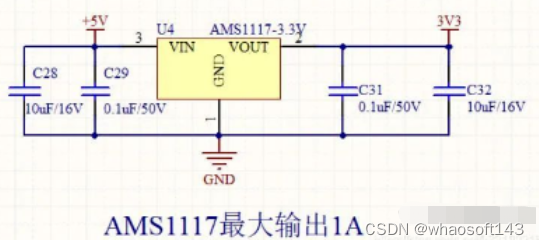

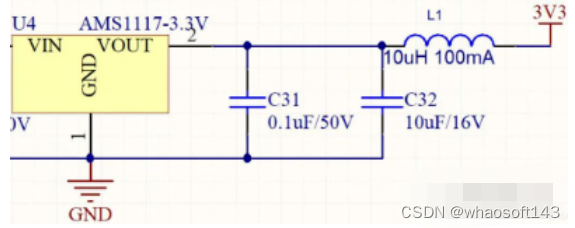

2 标注关键参数

如上图,标注了最大输出电流,这样可以方便别人修改电路的时候,知道电源能不能带得起负载。

也可以写其它参数,如:输入电压范围,适用的温度范围,甚至是数字电路中的真值表等。

3 电阻/电容/电感/磁珠的注释

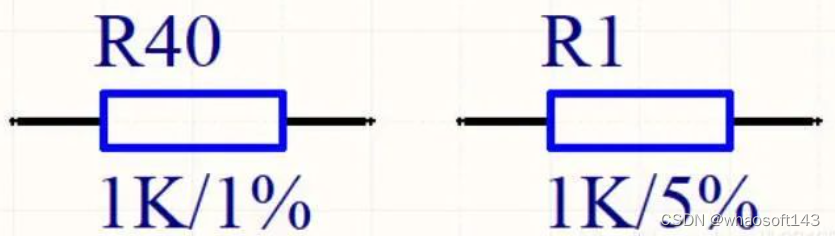

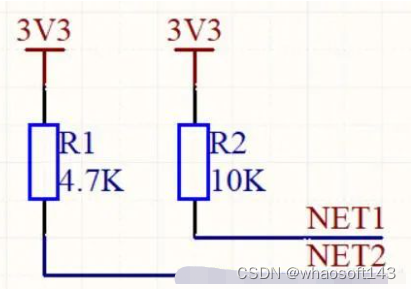

电阻

如上图所示,每个电阻都写上阻值、精度。针对大功率电阻,也可以写上功率,要视具体情况灵活变通。

一般对于开关电源上的采样电阻以及运放电路上的电阻得用1%精度,上下拉电阻可以使用5%精度。

注意:这里的阻值不建议写成102,要直接写成1K。尽量不要让别人去做这个换算,或者人家也不会算。

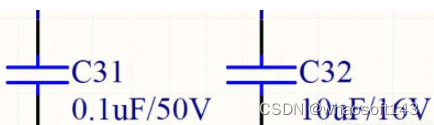

电容

如上图所示,每个电容都写上了容值和耐压。针对高精度电容,也可以写上精度,或者是材质。

如:瓷片电容的材质有X7R、Y5V、NP0等。

注意:这里的容值不建议写成105,要直接写成1uF。

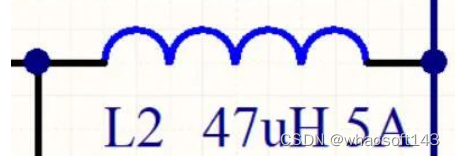

电感

如上图所示,每个电感都写上电感值和饱和电流。

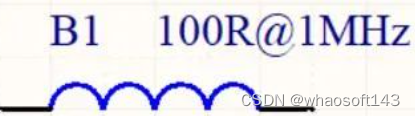

磁珠

如上图所示,每个磁珠都写上阻值和对应的频率。

其它元件

其它元件也是和电阻、电容等类似,如:晶振8MHz 50ppm等,要举一反三。

4 可维修性

如上图所示,增加L1电感,以便维修时可以断开,更容易排查故障。这里可以使用电感、磁珠或者0R电阻,视具体情况而定。

但是也有特殊情况,如果负载特别大,需要的串入的元件功率很大,成本增加太多,也是划不来的,这时,可以不加。

如果后面接的是QFP64封装之类芯片,功率又比较小,可以串入元件,因为QFP焊接不良的情况会比较多。

5 BOM表归一化

BOM表就是物料清单,尽量让物料的种类少一些,可以让采购员减少工作量,也会在生产上减少很多问题。

这里有两个上拉电阻,一个4.7K,一个10K,如果这个阻值影响不大的话,可以把它们都合并为10K。

去耦电容也是雷同的操作,要举一反三。

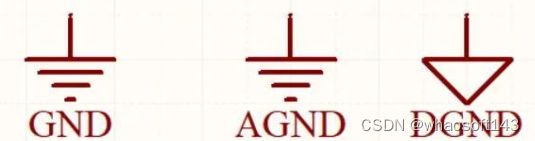

6 电源和地的符号

如上图所示。对于双电源系统来说,要在电源符号上写上正负号,单电源系统可以只写正号。

但是千万不要用VCC,不然别人看的时候还要观察一下是几V供电的。

如上图所示,只有一个地平面,则用GND。有数字地和模拟地,则用AGND、DGND。

也有一些系统还有视频地、音频地等,也要用不同的符号。

注意:不要把GND这些网络名给隐藏掉了,会容易出问题。

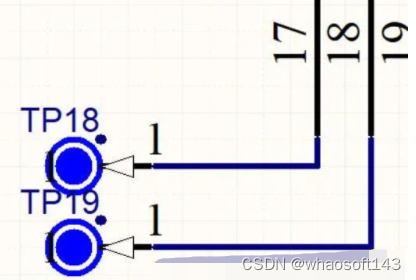

7 测试点

如上图所示,增加了测试点。测试点也就是一个圆形的pad,裸铜的。

在一些QFP、BGA、QFN封装的芯片,有的引脚很难用示波器测量,这时可以增加测试点,方便操作。

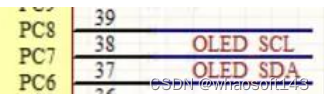

8 网络标号

如上图所示,PC7、PC6是接OLED12864的IIC接口。这里的网络标号增加OLED前缀,以减少网络标号的冲突,也增加了可读性。同理,接温度传感器的网络可以写DS18B20_DATA,网络标号上增加了元件名。其它的芯片也是一样的操作。

所有的网络标号均使用大写字母。

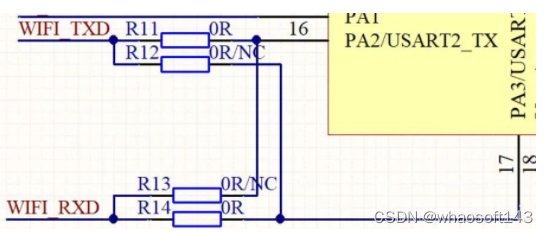

9 容错性/兼容性

在设计初期或是不经意,或是工期太赶,就没有那么多时间去研究电路上的接法是否正确。

这时可以使用一些预留的电路,来提高整板的容错性。

如上图所示,假设工程师还不确定是RX对TX还是RX对TX时,可以使用四个电阻来实现这两种接法。(NC为不接)

焊上R11和R14,不焊R12和R13时,是RX对RX,TX对TX的接法。

不焊R11和R14,焊上R12和R13时,是RX对TX,TX对RX的接法。

当调试通过后,再把这四个电阻去掉,并连上正确的接法。这样既能保证工期,又不会出错。

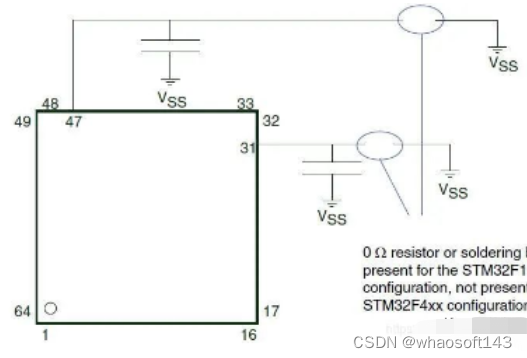

如果一个板子,不太确定用STM32的F103还是F407,此时,可以做成兼容设计。

如上图所示,圆圈中可放置0R电阻,使用F103时,把0R焊上,电容不焊。使用F407时,把电容焊上,0R不焊。

当然,也可以预留其它电路,要举一反三。

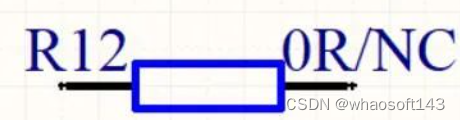

10 NC、NF

原理图上常常出现NC和NF两种字符,如下图所示,是不接、不焊的意思。

NC=Not connect 不接。

NF=Not Fix 不安装。

当然,NC也可以表示为normal close常闭,在继电器、接触器上用的多。

要视具体情况来辨认。

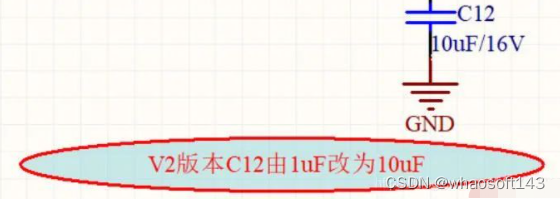

11 版本变更

很多时候一个电路不是一版就成功的。它会经历很多版本,每个版本都有变更的地方。这时要明确地标注出来。

如上图所示,明确地指出,V2版本把C12改成10uF,以便万一出问题,容易追溯。

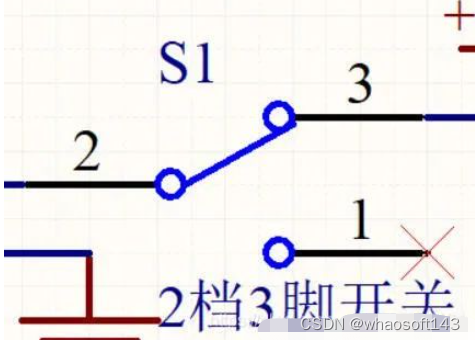

12 悬空引脚

悬空引脚也要画上X。

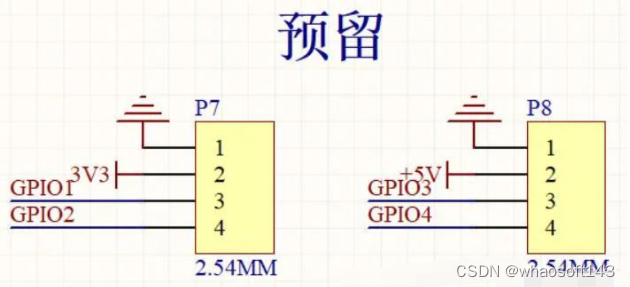

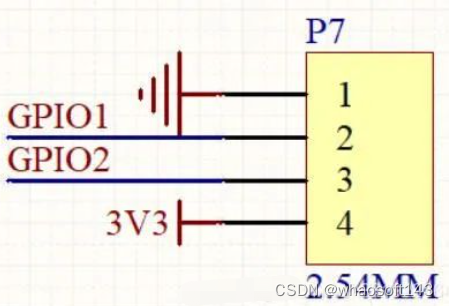

13 可扩展性

很多时候,需求是不断变化的。如果仅仅针对当前需求来设计,一旦将来有改动,又要重新打板。

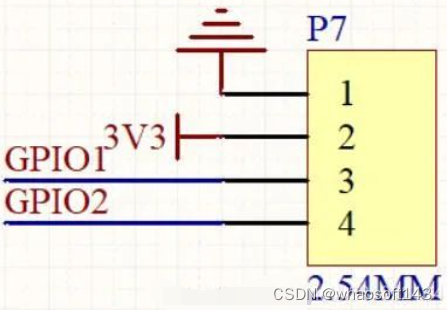

所以,很有必要增加一些预留的引脚、电路,以便快速验证整板的功能是否满足新需求。如下图所示,预留了一些IO口。

14 防呆

有一些接口是不防呆的,也就是存在两种或多种接法。

如上图所示,4P杜邦线(合在一起,没有分开的),有两种接法:

-

红黑白黄

-

黄白黑红

然后,该座子在原理图上是上图所示的定义,那么会有一种接法导致电源接反,可能会烧坏元件。

如果原理图是设计成这样,则不会烧坏元件,因为3.3V电源也就加在GPIO口上而已。

要做防呆,可以使用防呆的座子,如:USB座、航空接口等。

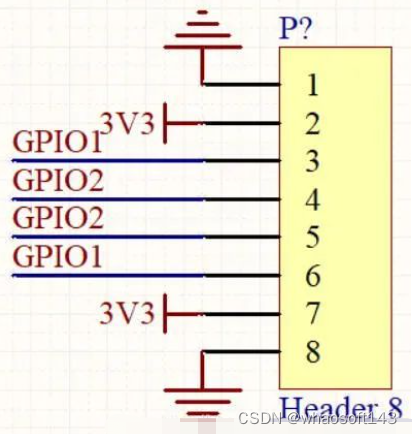

也有另一种方法,对称设计法。

如上图所示,引脚的排列是对称的,也就是无论怎么接,都是没问题的,只是成本会有所增加。

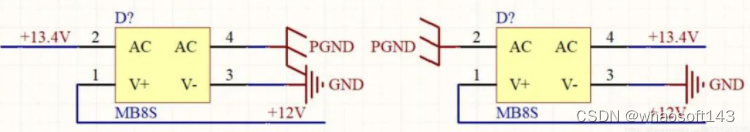

还有一种方法适用于直流电源的接口,一般是门禁系统用的多。

如上图所示,增加一个整流桥,不管+13.4V和PGND怎么接,在1、3引脚上都能产生正确的+12V和GND。

当然,这种方法也要考虑成本和功耗等。

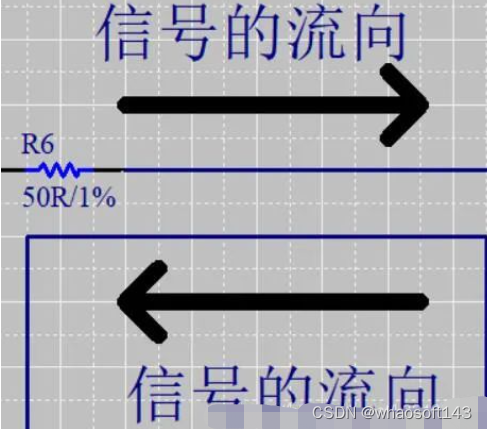

15 信号的流向

一些模拟电路,需要标明信号的流向。

如上图所示,标明了定向耦合器中的信号流向。

16 PCB走线建议

如果PCB不是你画的话,可以在原理图上标明PCB的走线规则或者建议。

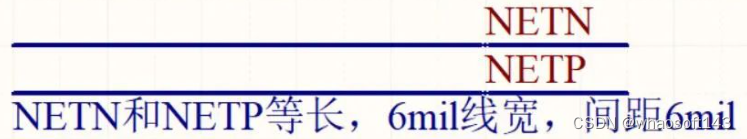

如上图所示,标明了一对差分线在PCB上的处理方法。

17 不使用\表示取反

一旦用了“\”,就有可能被wire挡住,然后看不到,从而导致网络可能连接不正确。

可以考虑用“#”来表示取反。

2381

2381

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?