1 理论学习(废话篇)

ADC 模拟数字转换器(额谈到这个,真的很荣幸在ADI实习的时光,打住不扯了),凡是涉及到模拟信号转数字信号的时候,都会用到ADC。

ADC的种类很多,有积分型,逐次比较型,SAR型等等,各有各的优势和缺点,一般根据实际项目来选择ADC型号。ADC有一个很重要的参数就是位宽,什么8位,12位,16位。这其实就是ADC的分辨率,最小能分辨的输入电压大小。假设ADC的位宽是8位,参考电压为5V,最小分辨率为:1/256*5v=0.0195mv 。

2 实战参考

FPGA高速ADC接口实战——250MSPS采样率ADC9481

2.1 ADC硬件特性分析(瞎抄的)

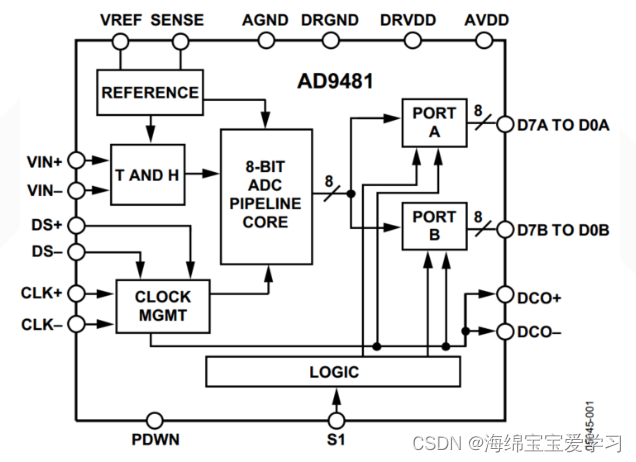

首先必须通过datasheet分析其核心参数、接口定义和时序要求。ADC9481的采样率为250MSPS,精度8bit。其原理结构图如下

主要引脚:

CLK:差分时钟输入,信号频率为250Mhz

VIN:模拟信号输入,范围是1vpp

VREF:电压参考输入输出,这里使用内部固定参考电压模式

SENSE:参考模式选择

D7A~D0A: 通道A的数字信号输出

D7B~D0B:通道B的数字信号输出

DCO: 数字差分时钟信号输出,信号频率为125Mhz

S1:数据格式选择,该接口电压决定数格式是原码还是补码

PDWN:低功耗选通

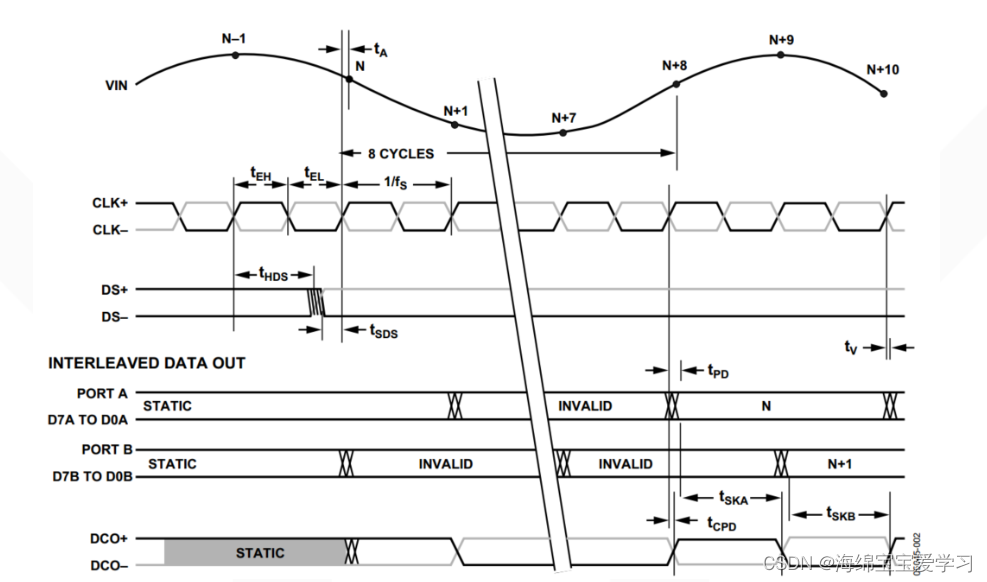

接下来看看接口时序:

2.2 基于FPGA的AD采集

LVDS低电压差分信号,是一种低功耗,低误码率、低串扰和低辐射的差分信号技术。KSPS,采样千次每秒,是转化速率的单位。

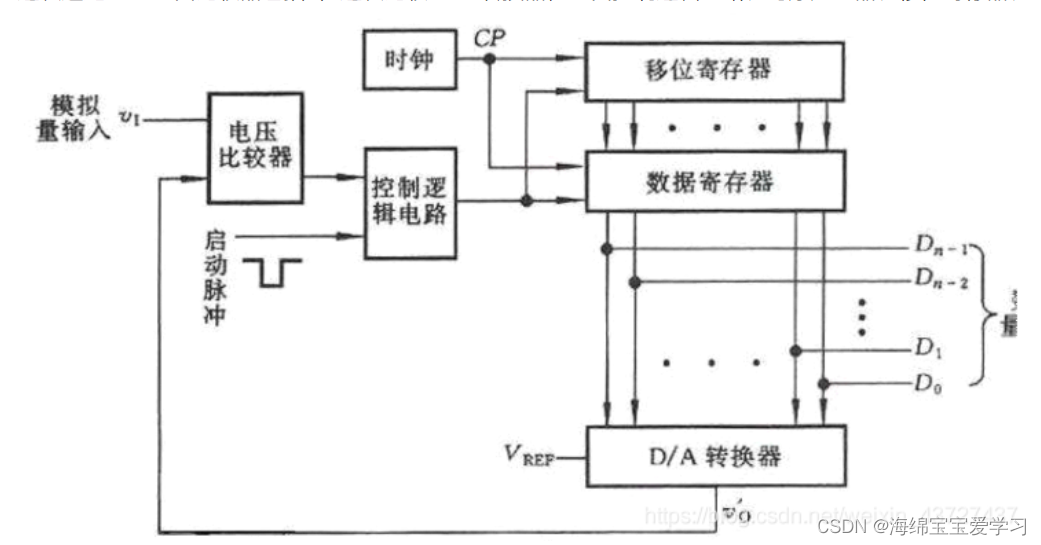

逐次逼近型ADC由比较器包括n位逐次比较型AD转换器,它由控制逻辑电路、时序产生器、移位寄存器、DA转换器及电压比较器组成

逐次逼近转换过程和用天平称重类似,从最重的开始试放与被称物体进行比较,若物体重于砝码,则该砝码保留,否则移去。再加上第二个次重砝码,由物体的重量是否大于砝码的重量决定第二个砝码是否保留。

逐次逼近AD转换器,就是将输入模拟信号与不同的参考电压作多次比较,使转换所得的数字量在数值上逐次逼近模拟量对应值。如上图,它由脉冲启动后,在第一个时钟脉冲作用下,控制电路使时序产生器的最高位置1,其他位置0,其输出的数据寄存器将100.000送到DA转换器,输入电压首先与DA器输出电压 VERF/2 进行比较,如果v1>= (VERF/2),比较器就输出1,否则为0.比较结果存于数据的寄存器的Dn-1位。然后再第二个时钟脉冲CP下,移位寄存器的次高位置1,其他低位置0.如最高位已存1,则此时vo=(3/4)VERF。于是v1再与(3/4)VERF相比较,如v1>=(3/4)VERF,则次高位 Dn-2=0;如最高位为0.,则vo=VERF/4 ,与vo相比较如 v1>= VERF/4,则Dn-2位存1,否则位存0…依次类推,逐次比较得到输出数字量。基准电压VREF。(抄了这么一大段 我好像还没理解,我来理一理)

好吧理解了一点,就这样依次比较!

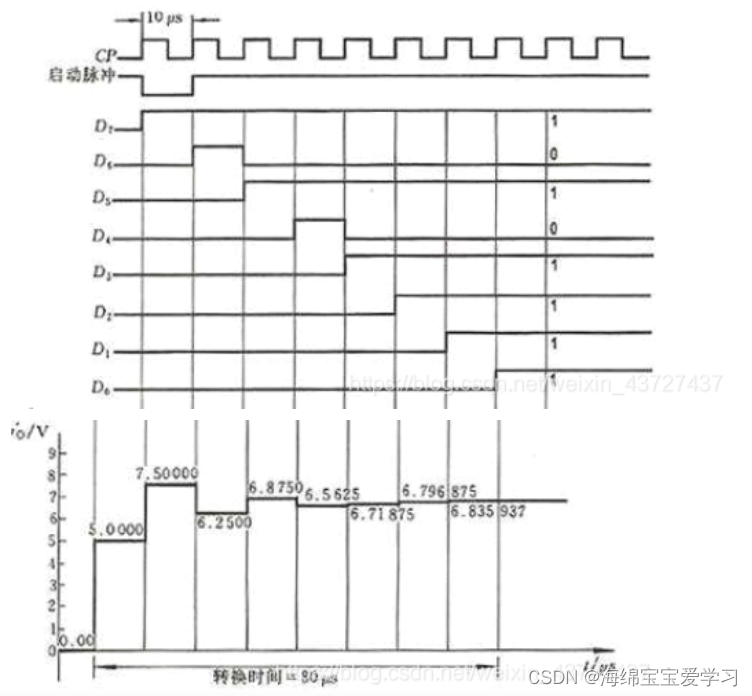

举个例子如下:

电路为8位AD转换器,输入模拟量VA=6.84v,DA转换器基准电压VREF=10v。当启动脉冲低电平到来后转换开始,在第一个CP作用下,数据寄存器将D7-D0=1000000000送入DA转换器,其输出电压vo=5v(这个0.5 怎么算出来的?),vA与vo比较,vA大于vo存1;第二个CP到来的时候,寄存器输出D7-D0=11000000,vo为7.5v,vA再与7.5v比较,因为小于7.5,所以D6存0;输入第三个CP时,D7~D0=10100000,vo=6.25v;vA再与v0进行比较,如此重复下去。经8个时钟周期,转换结束。由图中v0的波形可见,在逐次比较过程中,与输出数字量对应的模拟电压v0逐渐逼近vA值,最后得到AD转换器转换结果D7-D0为10101111。该数字量所对应的模拟电压为6.83v,与实际输入的模拟电压6.84的相对误差仅仅为0.06%。

2.2.1 AD7982

本实验打算采用AD7982这个数据采集设备,是一个12位高速,低功耗、8通道逐次逼近型ADC。采用单电源工作,电源电压为2.7v到5.25v,最高吞吐率可以达到1Msps。内置低噪声、宽带宽采样保持放大器,可以处理8Mhz以上的输入频率。

通过配置控制寄存器,器件的模拟输入范围可以在0到REFin或0v到2REFin间选择,可采用标准二进制或者二进制补码输出编码。AD7928具有八个通道序列器的单端模拟输入,可以通过预先编程选择通道转换顺序。

参考:https://blog.csdn.net/weixin_43727437/article/details/103349387

1485

1485

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?