SPI EEPROM

最近项目接触到SPI EEPROM这款存储器件,打算记录一下,下面内容大部分是数据手册的内容,其中夹杂着部分自己的理解,各位看官如在实际操作中发现不妥,请以英文手册为准。EEPROM一般都是小容量的存储设备,今天介绍的SPI接口的EEPROM,是美国微芯科技(MicroChip)的25系列产品,容量范围从1kbits到1Mbits不等,通常情况下用来保存一些程序参数。

| 型号 | 容量(bits) | 组织结构 | VCC范围 | 最大速度(MHz) | 页大小(Bytes) | 温度范围 | 封装 |

|---|---|---|---|---|---|---|---|

| 25LC010A | 1K | 128X8 | 2.5-5.5V | 10 | 16 | I,E | P,MS,SN,ST,MC,OT |

| 25AA010A | 1K | 128X8 | 1.8-5.5V | 10 | 16 | I | P,MS,SN,ST,MC,OT |

| 25LC020A | 2K | 256X8 | 2.5-5.5V | 10 | 16 | I,E | P,MS,SN,ST,MC,OT |

| 25AA020A | 2K | 256X8 | 1.8-5.5V | 10 | 16 | I | P,MS,SN,ST,MC,OT |

| 25LC040A | 4K | 512X8 | 2.5-5.5V | 10 | 16 | I,E | P,MS,SN,ST,MC,OT |

| 25AA040A | 4K | 512X8 | 1.8-5.5V | 10 | 16 | I | P,MS,SN,ST,MC,OT |

| 25LC080A | 8K | 1024X8 | 2.5-5.5V | 10 | 16 | I,E | P,MS,SN,ST |

| 25AA080A | 8K | 1024X8 | 1.8-5.5V | 10 | 16 | I | P,MS,SN,ST |

| 25LC080B | 8K | 1024X8 | 2.5-5.5V | 10 | 32 | I,E | P,MS,SN,ST |

| 25LC160A | 16K | 2048X8 | 2.5-5.5V | 10 | 16 | I,E | P,MS,SN,ST |

| 25AA160A | 16K | 2048X8 | 1.8-5.5V | 10 | 16 | I | P,MS,SN,ST |

| 25LC160B | 16K | 2048X8 | 2.5-5.5V | 10 | 32 | I,E | P,MS,SN,ST |

| 25AA160B | 16K | 2048X8 | 1.8-5.5V | 10 | 32 | I | P,MS,SN,ST |

| 25LC320A | 32K | 4096X8 | 2.5-5.5V | 10 | 32 | I,E | P,MS,SN,ST |

| 25LC320A | 32K | 4096X8 | 1.8-5.5V | 10 | 32 | I | P,MS,SN,ST |

| 25LC640A | 64K | 8192X8 | 2.5-5.5V | 10 | 32 | I,E | P,MS,SN,ST |

| 25AA640A | 64K | 8192X8 | 1.8-5.5V | 10 | 32 | I | P,MS,SN,ST |

| 25LC128 | 128K | 16384X8 | 2.5-5.5V | 10 | 64 | I,E | P,SN,SM,ST,MF |

| 25AA128 | 128K | 16384X8 | 1.8-5.5V | 10 | 64 | I | P,SN,SM,ST,MF |

| 25LC256 | 256K | 32768X8 | 2.5-5.5V | 10 | 64 | I,E | P,SN,SM,ST,MF |

| 25AA256 | 256K | 32768X8 | 1.8-5.5V | 10 | 64 | I | P,SN,SM,ST,MF |

| 25LC512 | 512K | 65536X8 | 2.5-5.5V | 20 | 128 | I,E | P,SM,MF |

| 25AA512 | 512K | 65536X8 | 1.8-5.5V | 20 | 128 | I, | P,SM,MF |

| 25LC1024 | 1024K | 131072 X8 | 2.5-5.5V | 20 | 256 | I,E | P,SM,MF |

| 25AA1024 | 1024K | 131072 X8 | 1.8-5.5V | 20 | 256 | I | P,SM,MF |

特点

-

最大时钟速度

-10MHz(1K~256K) -20Mhz(512K~1M) -

以字节为单位的写操作和以页为单位的写操作

-

低功耗的CMOS技术

-典型的写操作电流:5mA -典型的读操作电流:5mA @10MHz 7mA@20MHz -

典型的待机电流:1uA

-

写周期时间:最长5ms

最长6ms (25XX1024)

-

自同步的擦除操作与写操作

-

擦除功能(512K~1M)

-页擦除:最长6ms -扇区擦除:最长15ms -芯片擦除:最长15ms -

内置写保护

-上电/掉电数据保护电路 -写使能锁存 -写保护引脚 -

块/扇区写保护

-没保护,1/4保护,1/2保护或者全保护

-

顺序读

-

高可靠性

-

数据保存期:>200年

-ESD保护:>4000V -耐久性:> 1M次的擦除/写 -8引脚和6引脚的标准封装 -

支持的温度范围:

-工业(I):-40°C至85°C -汽车(E):-40°C至125°C

| 名称 | 功能 |

|---|---|

| CS | 芯片选择 |

| SO | 串行数据输出 |

| WP | 写保护 |

| VSS | 地 |

| SI | 串行数据输入 |

| SCK | 串行时钟输入 |

| HOLD | 控制输入 |

| VCC | 电源电压 |

简介

微芯科技公司支持与串行外围设备接口(SPI)兼容的串行总线体系结构,并且该系列低电压串行电可擦除EEROMs包含从1Kbits到1Mbits不同容量段。支持以字节和页为单位的功能操作,但高容量的512Kbit和1Mbit产品也支持扇区和芯片层次的功能操作,这两种功能操作通常与基于闪存的产品有关联。

总线信号包括一根时钟输入(SCK)信号以及独立的数据输入(SI)和数据输出(SO)信号,可以通过片选(CS)输入信号来控制设备的访问。

可以通过控制脚(HOLD)暂停对设备的访问,当设备处于暂停状态时,除了片选脚,所有输入脚上的传输都会被忽略,这让主机可以处理更高优先级的中断。

该系列SPI产品提供标准的8脚PDIP和SOIC封装,也提供更多更先进的封装,比如8脚TSSOP,MSOP,2X3 DFN,5X6DFN封装和6脚的SOT-23封装,所有封装都进行无锡(哑光锡)处理,符合RoHS标准。

1 功能介绍

1.1 操作原则

25系列串行EEPROM被设计成可以直接连接串行外设接口(SPI),现今流行的微处理器都有该接口,微芯的PIC微处理器也有该接口。那些没有内置SPI接口的微处理器也可以通过使用分散的IO脚来模拟SPI协议达到正确写数据的目的。

该系列的EEPROM内部都有一个8bit的指令寄存器。可以通过SI引脚访问器件,数据会在SCK的上升沿锁存,在整个操作过程中,CS脚必须拉低并且HOLD脚必须拉高。

表2-1包含了一系列的可能的指令字节和操作格式,所有指令,地址,数据在传输过程中,都是先传输高有效位,后传输低有效位。

CS拉低后,数据(SI)会在第一个SCK的上升沿采样,如果时钟线跟其它外设共用,(为避免受到干扰)用户可以控制HOLD输入生效,使EEPROM处于‘保持’模式,之后释放HOLD脚,将恢复到HOLD生效前的那个状态点。

表1-1 指令集

| 指令名称 | 指令格式 | 简介 |

|---|---|---|

| 所有容量段都有的指令 | ||

| READ | 0000 0011 | 从存储阵列的指定地址开始读取数据 |

| WRITE | 0000 0010 | 往存储阵列的指定地址开始写数据 |

| WREN | 0000 0110 | 设置写使能锁存位(使能写操作) |

| WRDI | 0000 0100 | 复位写使能锁存位(失能写操作) |

| RDSR | 0000 0101 | 读状态寄存器 |

| WRSR | 0000 0001 | 写状态寄存器 |

| 只有25XX512 和 25XX1024才有的指令 | ||

| PE | 0100 0010 | 页擦除--擦除存储阵列中的一页 |

| SE | 1101 1000 | 扇区擦除--擦除存储阵列中的一个扇区 |

| CE | 1100 0111 | 芯片擦除--擦除存储阵列中的所有扇区 |

| RDID | 1010 1011 | 从深度睡眠中恢复和读取电子签名 |

| DPD | 1011 1001 | 进入深度睡眠模式 |

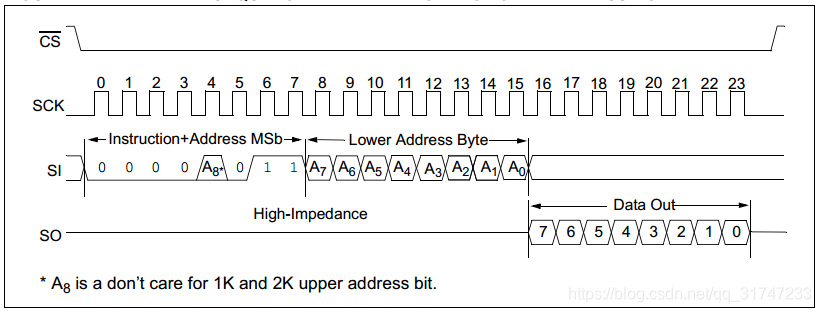

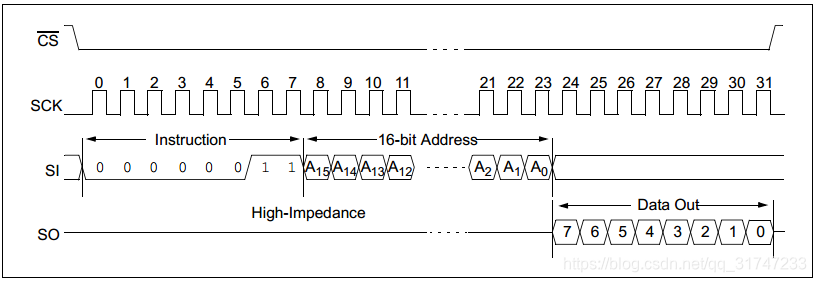

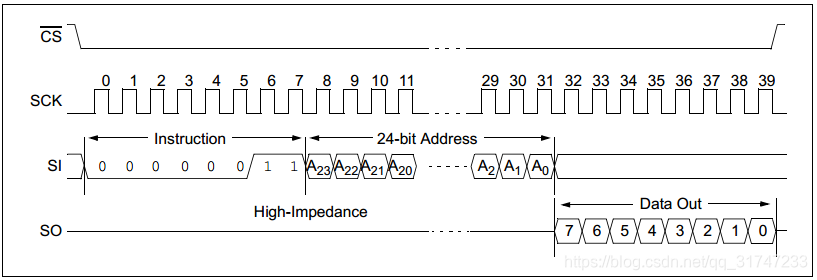

1.2 读序列

先将CS脚拉低选中器件,然后将8bit的READ指令发送给EEPROM,指令后面跟着地址,正确发送READ指令和地址后,对应地址上的数据将通过SO脚输出,如果继续提供时钟脉冲,下一个地址的数据将会顺序输出。每输出1byte数据,器件内部的地址指针都会自动递增,当达到最高地址后,地址计数器将恢复成00000h,这将使器件无限循环读。CS拉高后,读操作将终止。

表1-2 读/写序列寻址

| 容量 | 寻址所需bit数 | 最大地址 | 页大小 |

|---|---|---|---|

| 1K | 7 | 007F | 16 Bytes |

| 2K | 8 | 00FF | 16 Bytes |

| 4K | 9 | 01FF | 16 Bytes |

| 8K | 10 | 03FF | 16或32 Bytes |

| 16K | 11 | 07FF | 16或32 Bytes |

| 32K | 12 | 0FFF | 32 Bytes |

| 64K | 13 | 1FFF | 32 Bytes |

| 128K | 14 | 3FFF | 64 Bytes |

| 256K | 15 | 7FFF | 64 Bytes |

| 512K | 16 | FFFF | 128 Bytes |

| 1024K | 167 | 1FFFF | 256 Bytes |

| 注意:版本A - 16Bytes 版本B - 32Bytes | |||

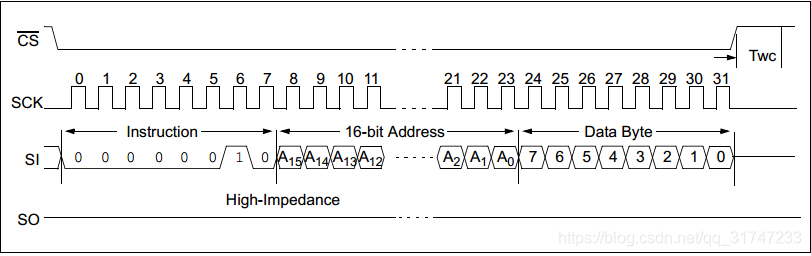

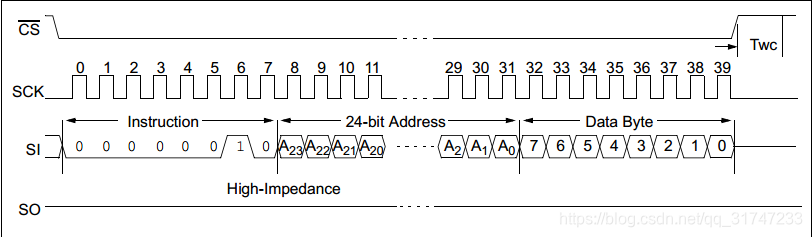

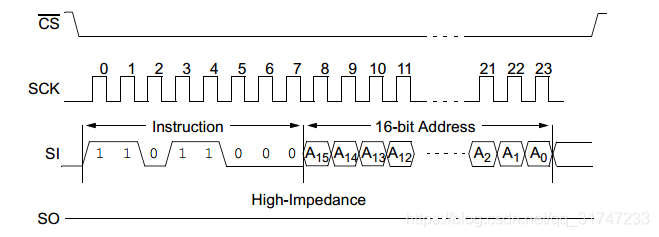

8bit或者9bit寻址的读时序

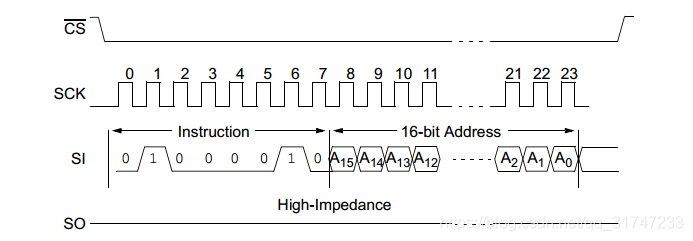

16bit寻址的读时序

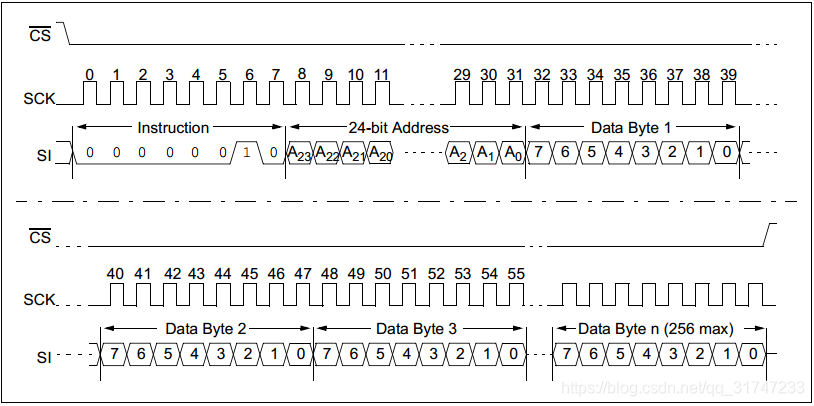

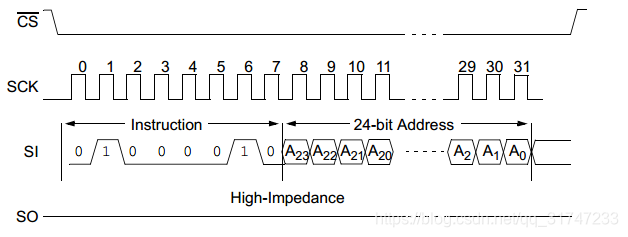

24bit寻址的读时序

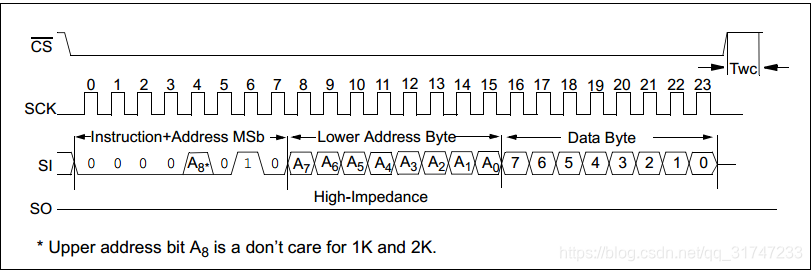

1.3 写序列

在尝试往EEPROM中写数据之前,必须发送WREN指令设置写使能锁存位。CS拉低,然后随着时钟输出正确的指令给EEPROM,在8 bits指令传输完成后,必须拉高CS才能置上写使能锁存位。如果在发送WREN指令后,CS没有拉高,然后立即发起写操作,数据将不会写入存储阵列,因为此时写使能锁存位并没有被正确置上。

一个写序列包含一个自动的同步擦除周期,所以在写命令之前并不需要擦除。

一旦写使能锁存位置上了,用户可以继续拉低,然后发送WRITE指令,地址以及要写的数据。需要的话,可以在一个写周期内将1页数据写进设备,不同容量段,1页的大小从16Bytes到256Bytes不等,唯一的限制就是,所有的数据要写进同一个页。前面的表格展示了页大小的信息

对于25XX512和25XX1024,无论是否要写满整个页,都会对整个页进行刷新,所以这类器件的耐久性取决于每个页。

| 注意:不管实际上有多少数量的数据要写,页写操作仅限于在一个物理页内写数据。物理页的边界起始于页缓存大小(页大小)的整数倍位置,结束于页大小整数倍-1的位置。如果一个页写命令尝试越界写数据,那么数据会环绕到当前页的起始位置(将覆盖之前写下的数据),而不会像预期那样写入到下一个物理页。所以对应用软件来说,避免页写操作的越界就显得尤为重要 |

|---|

为了确保数据确实写进存储阵列,当第n byte数据的最低有效位(D0)传送完毕,CS必须将拉高。如果在任意节点拉高CS,写操作将不能完成。当写操作正在进行时,可以读状态寄存器来检查WIP和WEL位。处于写周期时,不可能从存储整列中进行读数据。当写周期结束,写使能锁存位将复位。

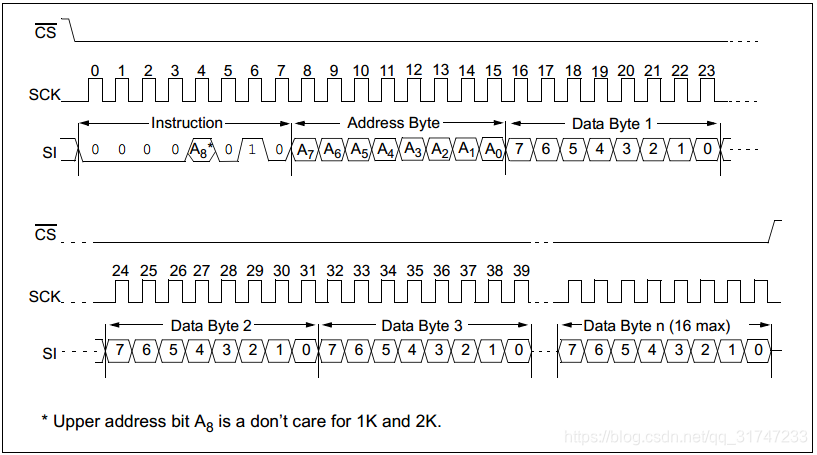

8bit或者9bit寻址的写时序

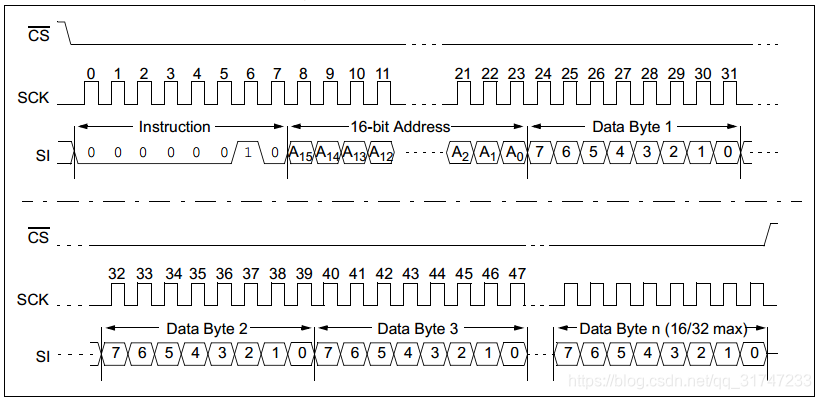

16bit寻址的写时序

24bit寻址的写时序

8bit或者9bit寻址的页写时序

16bit寻址的页写时序

24bit寻址的页写时序

1.4 写使能和写失能

EEPROM包含一个写使能锁存位。在任何写操作内部执行完成前,该锁存位都必须置上。WREN指令可以置上该锁存位,WRDI指令可以复位该锁存位。

以下列出的是写使能锁存位被复位的情况:

- 上电

- WRDI指令成功执行

- WRSR指令成功执行

- WRITE指令成功执行

- WP脚被拉低时(仅限于1K,2K,4K)

25XX512和25XX1024才有的指令也有复位锁存位的情况: - PE指令成功执行

- SE指令成功执行

- CE指令成功执行

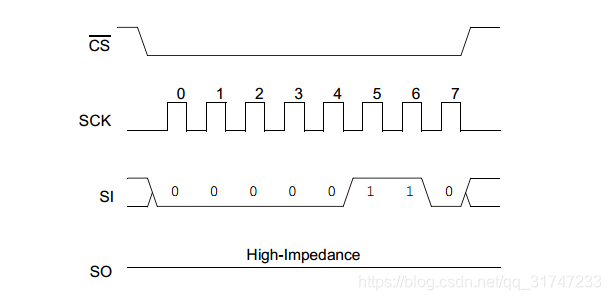

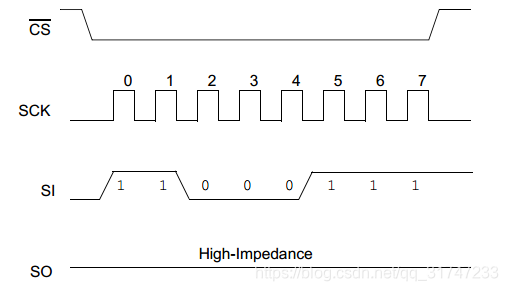

写使能指令时序

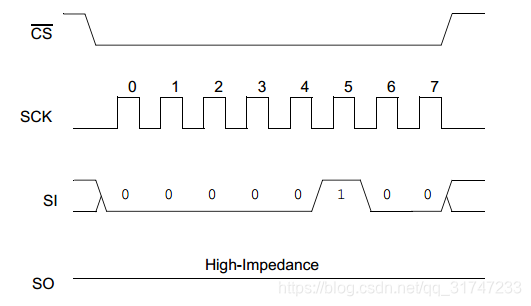

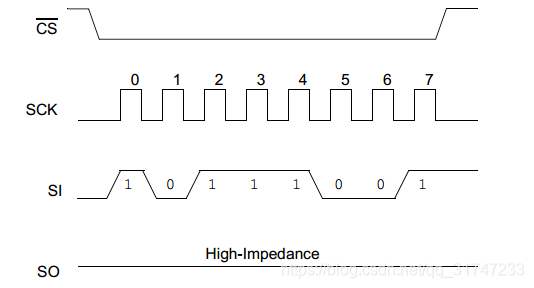

写失能指令时序

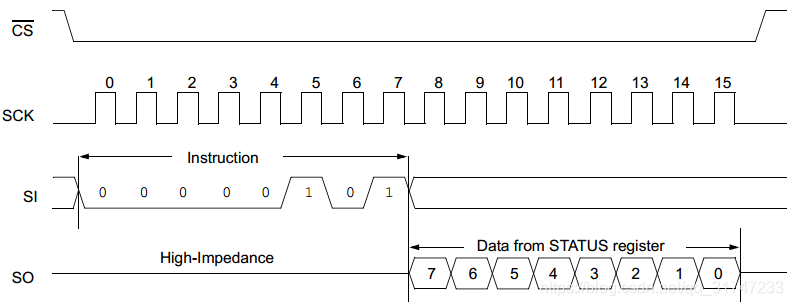

1.5 读状态寄存器指令

读状态寄存器指令(RDSR)提供访问状态寄存器的方式,可以在任意时点读取状态寄存器,即使处于写周期也一样可以,下表展示了状态寄存器每一位的情况。

状态寄存器

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| 可写可读 | -- | -- | -- | 可写可读 | 可写可读 | 只读 | 只读 |

| WPEN | X | X | X | BP1 | BP0 | WEL | WIP |

| 注意:WPEN位在25XX010A,25XX020A,以及25XX040A上无效 | |||||||

WEL位展示了当前写使能锁存位的状态,该位是只读位,当该位置1时,允许将数据写入存储阵列,当该位为0时,禁止写数据。不管状态寄存器上的WPEN位是什么情况,都可以通过WREN指令和WRDI指令来更改WEL位的值。

BP0和BP1位表明当前哪些块处于写保护状态。用户可以通过发送WRSR指令来设置这些位,这些位是非易失性的。

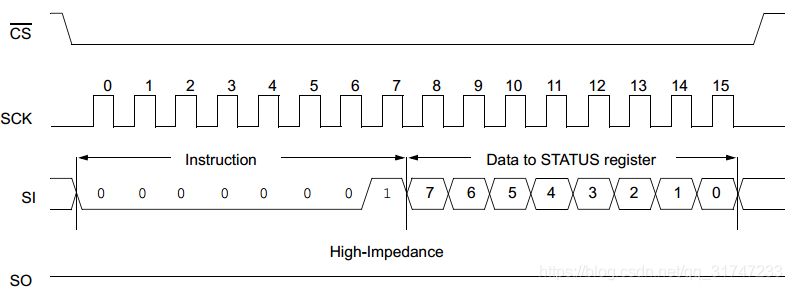

读状态寄存器时序

1.6 写状态寄存器指令

写状态寄存器指令允许用户写状态寄存器中的非易失位,用户可以通过写入适当的值使存储阵列处于四种不同水平的写保护状态之一,存储阵列被分割成四个部分,用户可以令一部分,两部分或者四部分处于写保护,也可以选择全部都没有写保护。表1-4展示了各部分的控制情况。对于8Kbits以及更高容量的EEPROM,WPEN位是非易失性位,该位可作为WP引脚的使能位,WP脚与WPEN位组合形成可编程的硬件写保护功能,当WP为低并且WPEN为1时,硬件写保护生效,当WP为高或者WPEN为0时,硬件写保护失效。当芯片处于硬件写保护时,状态寄存器上的非易失性位无法修改。

阵列保护

| BP1 | BP0 | 被保护的阵列 | 没被保护的阵列 |

|---|---|---|---|

| 0 | 0 | 没有 | 全部(扇区0,1,2,3) |

| 0 | 1 | 高1/4地址(扇区3) | 低3/4地址(扇区0,1,2) |

| 1 | 0 | 高1/2地址(扇区2,3) | 低1/2地址(扇区0,1) |

| 0 | 0 | 全部(扇区0,1,2,3) | 没有 |

阵列保护地址

| 容量 | 高1/4 (扇区 3 ) | 高1/2 (扇区2,3 ) | 所有扇区 |

|---|---|---|---|

| 1K | 60h-7Fh | 40h-7Fh | 00h-7Fh |

| 2K | C0h-FFh | 80h-FFh | 00h-FFh |

| 4K | 180h-1FFh | 100h-1FFh | 000h-1FFh |

| 8K | 300h-3FFh | 200h-3FFh | 000h-3FFh |

| 16K | 600h-7FFh | 400h-7FFh | 000h-7FFh |

| 32K | C00h-FFFh | 800h-FFFh | 000h-FFFh |

| 64K | 1800h-1FFFh | 1000h-1FFFh | 0000h-1FFFh |

| 128K | 3000h-3FFFh | 2000h-3FFFh | 0000h-3FFFh |

| 256K | 6000h-7FFFh | 4000h-7FFFh | 0000h-7FFFh |

| 512K | C000h-FFFFh | 8000h-FFFFh | 0000h-FFFFh |

| 1024K | 18000h-1FFFFh | 10000h-1FFFFh | 00000h-1FFFFh |

写状态寄存器时序

1.7 数据保护

已实施以下措施防止意外写入存储阵列:

- 上电复位写使能锁存位;

- 设置写使能锁存位必须发送WREN指令;

- 在字节写,页写,写状态寄存器之后,写使能锁存位都会复位;

- 在给内部写周期适当的时钟周期后,CS必须拉高。

- 内部写周期期间,访问存储阵列将被忽略

写保护功能表

| WEL (SR bit 1) | WPEN (SR bit 7)* | WP (pin 3) | 保护块 | 非保护块 | 状态寄存器 |

|---|---|---|---|---|---|

| 1 | X | X | 保护 | 保护 | 保护 |

| 1 | 0 | X | 保护 | 可写 | 可写 |

| 1 | 1 | 0 | 保护 | 可写 | 保护 |

| 1 | 1 | 1 | 保护 | 可写 | 可写 |

| X = 不需要考虑 * = WPEN 在24XX010A/020A/040A上无效 | |||||

1.8 上电状态

以下情况EEPROM将开机:

- 器件处于低功耗待机模式(CS=1);

- 写使能锁存位被复位;

- SO处于高阻态;

- CS由高拉低进入活跃态。

1.9 页擦除

页擦除是闪存特有的功能,现在只有512kbit和1024kbit容量的EEPROM才有这个功能,该功能是对给定的页的所有比特进行擦除(所有比特都变为1),在执行页擦除之前必须发送WREN指令(拉低CS,然后开始随时钟输出指令,当8bit指令传输完毕,拉高CS使写使能锁存位被置上),要执行页擦除功能,首先要拉低CS,然后发送指令码,指令码后面跟着2字节或者3字节的地址,页内的任何一个地址都是有效的擦除地址。

当地址的最后1bit发送出去后,必须将CS拉高,否则不会执行擦除命令,一旦CS拉高,自同步的页擦除就开始了,可以通过读取状态寄存器的WIP位来判断擦除是否完成。

如果页擦除命令所给的地址是受保护的块(BP1,BP0决定)的地址,则命令序列将终止并且不会有擦除发生。

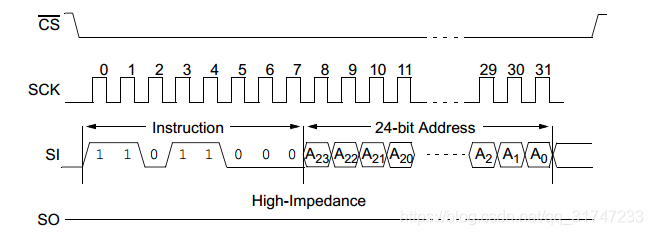

24bit寻址页擦除序列

16bit寻址页擦除序列

1.10 扇区擦除

扇区擦除是闪存特有的功能,现在只有512kbit和1024kbit容量的EEPROM才有这个功能,该功能是对给定的扇区的所有比特进行擦除(所有比特都变为1),在执行扇区擦除之前必须发送WREN指令(拉低CS,然后开始随时钟输出指令,当8bit指令传输完毕,拉高CS使写使能锁存位被置上),要执行扇区擦除功能,首先要拉低CS,然后发送指令码,指令码后面跟着2字节或者3字节的地址,扇区内的任何一个地址都是有效的擦除地址。

当地址的最后1bit发送出去后,必须将CS拉高,否则不会执行擦除命令,一旦CS拉高,自同步的扇区擦除就开始了,可以通过读取状态寄存器的WIP位来判断擦除是否完成。

如果扇区擦除命令所给的地址是受保护的块(BP1,BP0决定)的地址,则命令序列将终止并且不会有擦除发生。

24bit寻址扇区擦除序列

16bit寻址扇区擦除序列

1.11 芯片擦除

芯片擦除命令会擦除所有的比特(所有比特都变为1),执行芯片擦除之前必须发送WREN指令(拉低CS,然后开始随时钟输出指令,当8bit指令传输完毕,拉高CS使写使能锁存位被置上),要执行芯片擦除功能,先拉低CS,然后发送指令码,当指令的最后1bit发送出去后,必须将CS拉高,否则不会执行擦除命令,一旦CS拉高,自同步的芯片擦除就开始了,可以通过读取状态寄存器的WIP位来判断擦除是否完成。

如果有设置保护块(BP1,BO0决定),那么芯片擦除命令将被器件忽略。

芯片擦除序列

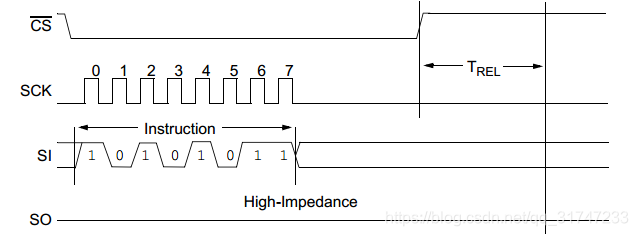

1.12 深度睡眠模式

深度睡眠模式是25XX512和25XX1024才有的功能,可以使设备进入低功耗状态。当设备处于低功耗模式时,不会响应任何的读写命令,所以可以把这当成是额外的软件写保护功能。

要执行深度睡眠功能,先拉低CS,然后发送指令码,再拉高CS。如果8bit指令码发送完后没有拉高CS,则设备不会进入深度睡眠模式,一旦拉高CS,在经过一段延时(TDP)后,会稳定在低功耗状态下。

在深度睡眠模式下,除了RDID指令,其它任何指令都会被忽略,RDID指令会将设备从深度睡眠模式下唤醒,并且会输出电子签名(ID),一段时间(TREL)后,设备将进入待机模式。

设备掉电后,会自动从深度睡眠模式中释放,再重新上电后,将直接进入待机模式。

深度睡眠序列

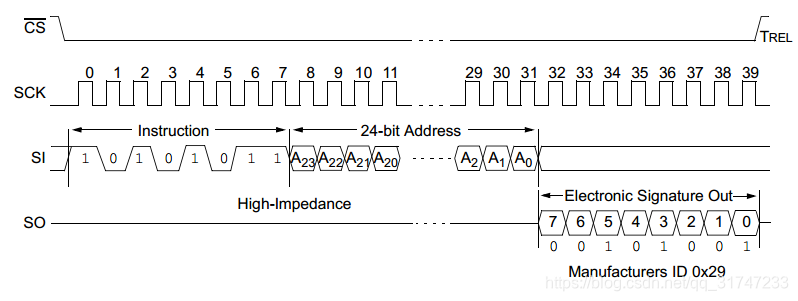

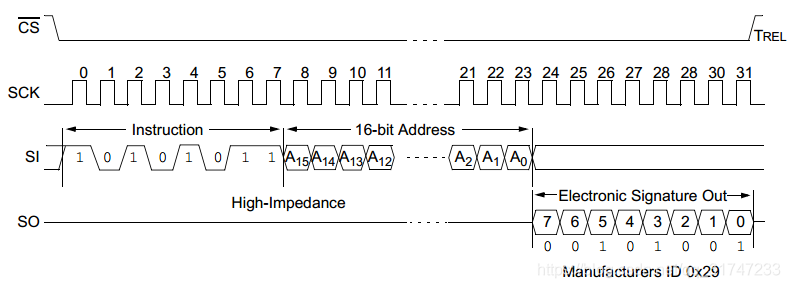

1.13 从深度睡眠中唤醒并读取电子签名

在深度睡眠模式下,除了RDID指令,其它任何指令都会被忽略,该指令在设备没有进入深度睡眠模式下也可以使用,可以在没有擦除,写数据,写状态寄存器命令正在执行的情况下读取电子签名。要执行RDID功能,先拉低CS,然后发送指令码,指令码后面跟着24bits的虚拟地址(25XX1024)或者16bits的虚拟地址(25XX512),当最后1bit虚拟地址发送完后,SO引脚将会输出8bit的电子签名,当电子签名的最后1bit传送出来后,可以拉高CS结束此次命令序列,之后设备将进入待机状态,等待下一次的片选及指令。如果在电子签名输出完成后还继续提供时钟脉冲,则将继续输出签名,直到拉高CS结束命令序列。

如果在发送RDID指令后,不等设备输出电子签名就拉高CS,依旧能保证设备从深度睡眠模式中唤醒过来,然而要进入待机模式还需要等待TREL时间。

24bit寻址RDID指令时序

16bit寻址RDID指令时序

仅从深度睡眠唤醒序列

2163

2163

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?