文章仅为个人理解,学习记录,不具备任何权威性,转载请注明出处,悉知。

电快速瞬变脉冲群 这个拗口的难以记住的名字代表什么意思?

就是往你的电源线信号线里加一段高频的杂波,打的电源瑟瑟发抖,打的信号面目全非,他妈都不认识了,何况是CPU呢。

这高频杂波吧,进入你的电源线和信号线以后,你要是不管教管教,他能上天,通过辐射发射耦合到pcb里任何一个信号上,使你的大脑(cpu)神经错乱,彻底崩溃。

EMC整改三要素:屏蔽,滤波,接地。

EMC整改需要了解:源,干扰途径,敏感设备。

所以EFT整改也围绕以上几点进行,解决这些该死的干扰。

如果想要战胜一个人就要去了解他。孙子兵法云,知己知彼,百战不殆。

那我们也要彻彻底底的了解 EFT,才能战胜他。

翻看EMC族谱(GBT17626),GBT17626.4 对EFT的介绍是应有尽有。

一 . EFT的身世(干扰源)。

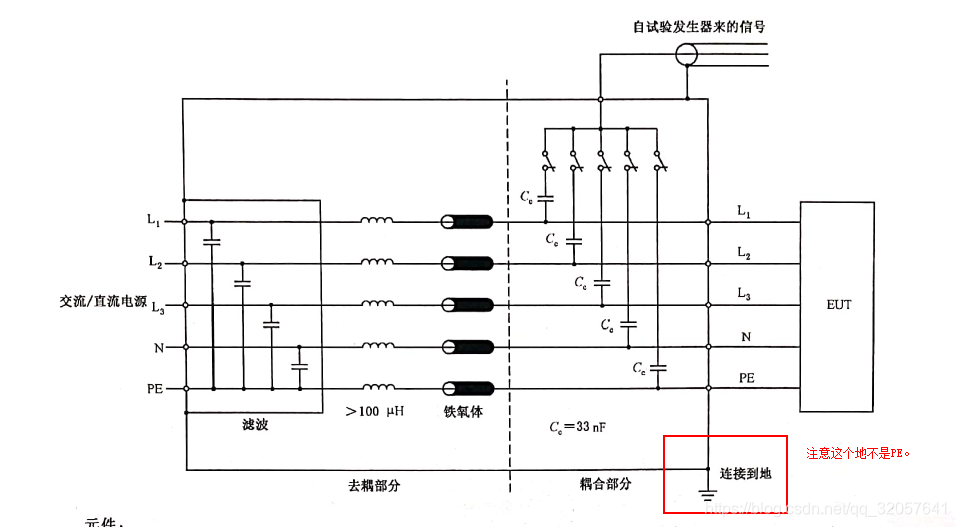

1.EFT干扰信号通过耦合/去耦网络中33NF的电容耦合到主电源上的。(红框标出需特别注意!!!)

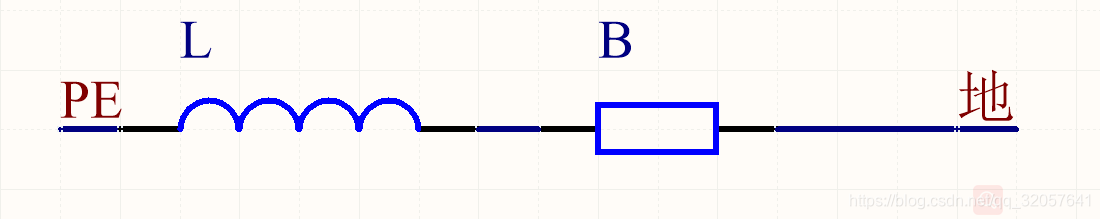

亲测 用万用表去测量EFT设备时发现输出PE和大地是连在一起的呀,PE就是大地?用简单示意图描述下

L和铁氧体构成去耦网络,所以用万用表的直流来测量时,确实导通,但对于高频信号来说PE不是地。

2.对于信号线或控制电缆通过容性耦合夹施加干扰,其等效电容为50pF~200pF。

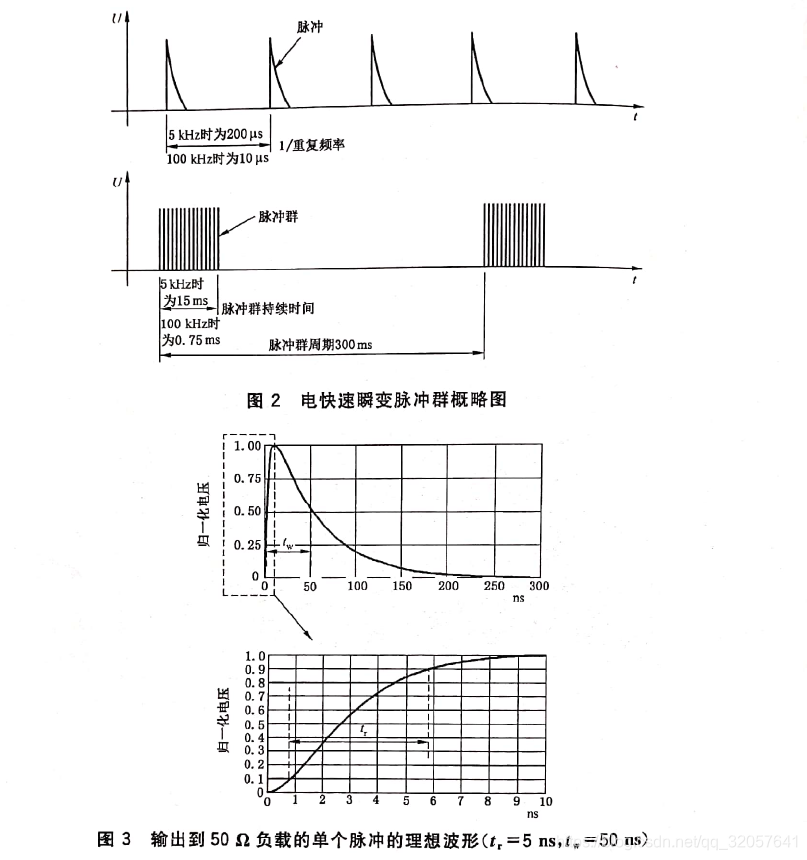

施加脉冲信号上图,通过傅里叶变换它的频谱是从5kHz(100kHz)~100MHz 的离散谱线。

负载阻抗50Ω时,对于33nF 的电容,下限截止频率为100kHz,也就是说电源端耦合EFT 脉冲的频谱范围为100kHz~100MHz;对于200pF 的电容,下限截止频率为15MHz。

二,干扰途径

a, 通过耦合单元进入电源线和控制线。

b,高频干扰通过电源线和信号线缆耦合附近的信号线缆上。

c,通过线缆辐射进设备。

三,敏感设备

我们通常关心的是PCBA的功能,所以PCBA所有的易受干扰的电子器件及信号线电源线都是我们要保护的对象。

摸清楚EFT的特性后,我们开始整改。

四,屏蔽

1.针对干扰途径1,对用信号线和电源线我们要采用屏蔽线。

2.针对干扰途径2,各信号线分开布线,减少耦合。

3.针对干扰途径3和敏感设备分析,对于PCBA上敏感器件及电路用屏蔽罩屏蔽,MCU DDR等,信号线控制线要隔离后进入PCB。

五,滤波

1,由干扰源可知,干扰信号为共模信号,去选用共模滤波器,滤波频率需覆盖干扰信号频率。

2,针对干扰途径3和敏感设备分析,滤波器最好放在线束设备的入口,滤除进入设备的电缆干扰型号,减少辐射信号。

3,对于电源和信号线电路,需要增加共模电感,Y电容,TVS和压敏电阻等防护器件。

六 接地

1.金属外壳器件,需将滤波器外壳与金属外壳相连,Y电容等需接到金属外壳,若金属外壳有接地柱,可通过接地柱直接泄放,若没有接地柱,可通过金属外壳和参考地之间形成的电容泄放。

2.非金属外壳,若设备有接地点,滤波器外壳及Y电容等需连接接地点通过接地点泄放,若无接地点,必要时需增加一块铁板,将滤波器和Y电容等该铁板连接,通过铁板与参考地之间形成的电容泄放。

FET测试设置说明:

针对交流电源输入端口设置说明:

1,根据实验等级设置电压峰值,比如±2KV,也可设置区间比如±500-±2KV,步进1%等。

2,干扰时间通常是1个极性1min。

3,设置耦合回路,可单独,可同时,也可组合。举个例子说明下:LNPE三个电源线,单独是:同一时间段只对LNPE其中一根线施加干扰,同时是,对其中两个同时施加干扰,组合是将单独和同时两种模式下所有情况都测试。

4,设置频率:5KHZ和100KHZ,根据需求设置。

关于结果判定ABCD等级不作详细说明,根据客户或标准要求。

总结:

EMC设计与整改是一个系统性工程,从测试项目来说ESD EFT SURGE RE CE RS CS等都是联系在一块的,需要综合考虑和平衡。

从原理图设计 PCB LAYOUT 软件设计到外围保护器件安装,线束布线等各方面都会影响EMC性能,也许综合考虑。

硬件电路设计从开始到结束始终有两个基本点需要把握,一是性能,二是成本,性能达到了,项目经理就要拿着一个计算器跟在你后面了,~~你的滤波器太贵,你的防雷器也太贵了,线束能不能不用屏蔽线呀太贵了,PCBA成本太高了要降本~~ ,所以我认为成本才是EMC设计最大的难题?。

本文深入解析电快速瞬变脉冲群(EFT)干扰源、传播路径及敏感设备,阐述EMC设计中屏蔽、滤波与接地的重要性,并提供整改策略。涵盖EFT测试设置与结果判定,强调EMC设计的系统性。

本文深入解析电快速瞬变脉冲群(EFT)干扰源、传播路径及敏感设备,阐述EMC设计中屏蔽、滤波与接地的重要性,并提供整改策略。涵盖EFT测试设置与结果判定,强调EMC设计的系统性。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?