Altera - Quartus II食用方法

- @ 代码 => 模块原理图

- 开发板 - EP4CE10

- FPGA简介

- Quartus II

- SignalTap II(信号窃听)

- Modelsim仿真环境搭建——业界公认仿真最优秀

- Verilog简介

- Verilog基础语法

- Verilog程序框架

- Verilog高级知识点

- 有限状态机Finite State Machine

@ 代码 => 模块原理图

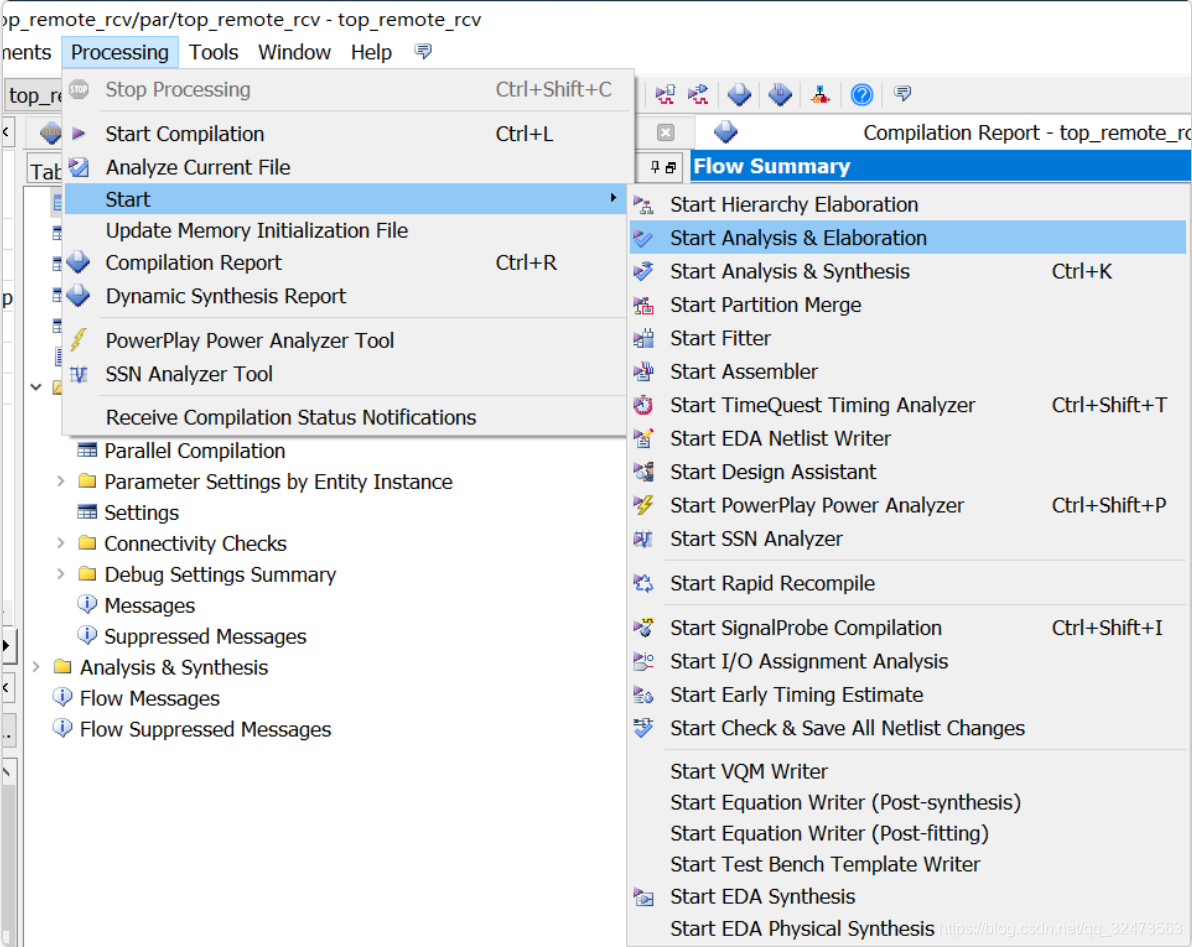

[1/2]Processing => Start => Start Analysis & Elaboration

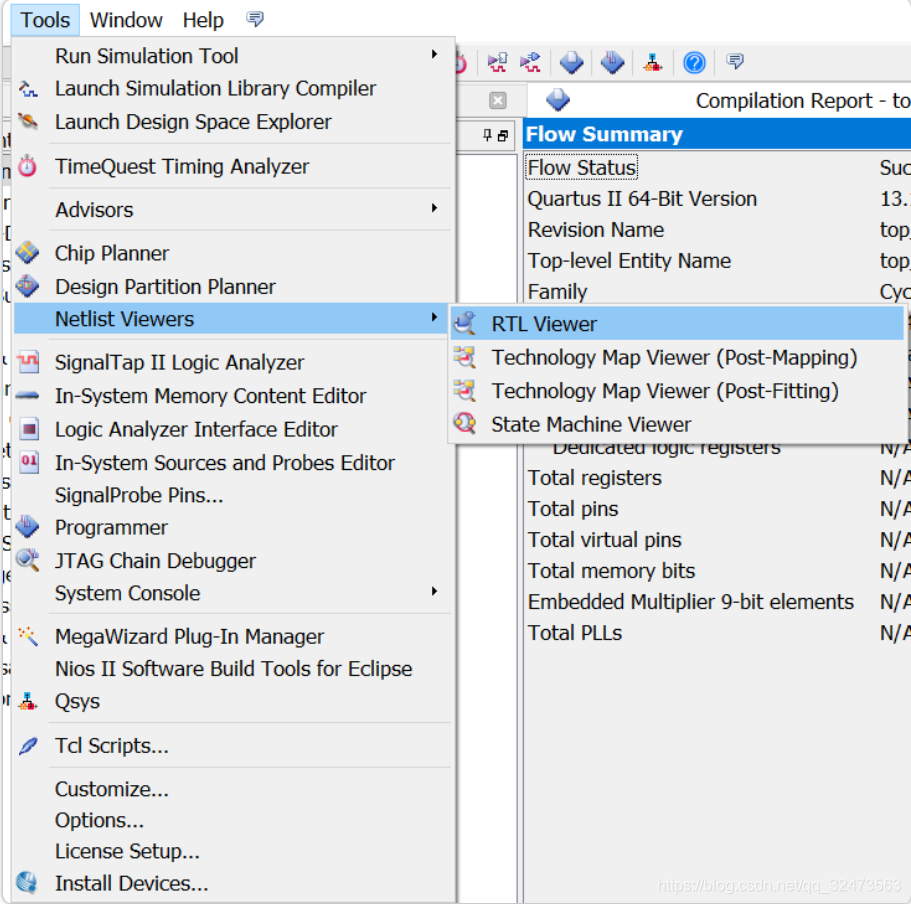

[2/2] Tools => Netlist Viewers => RTL Viewers

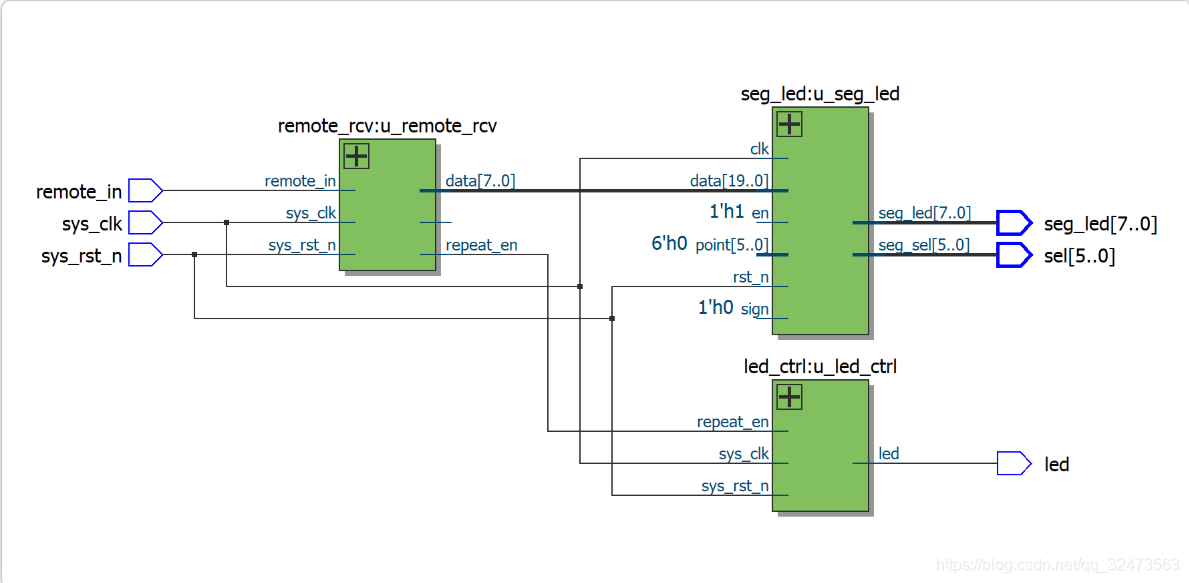

[效果] 模块原理图

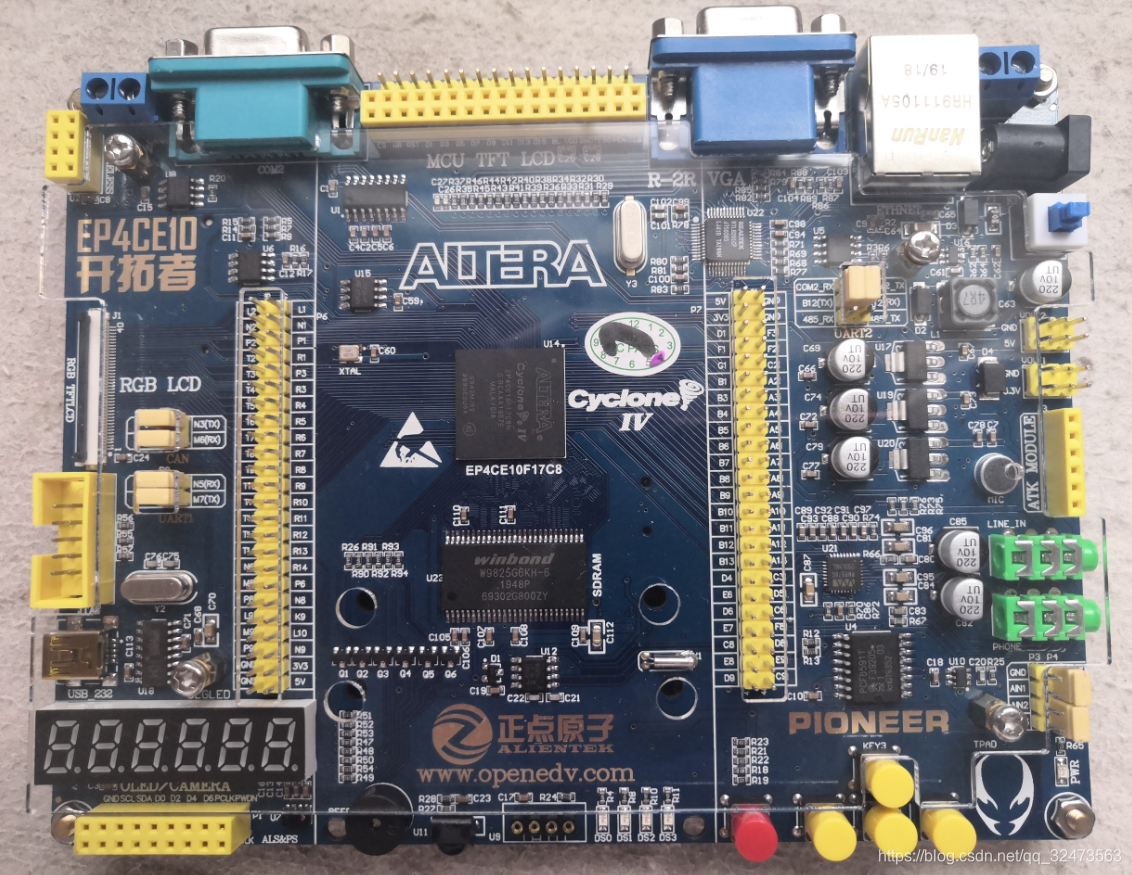

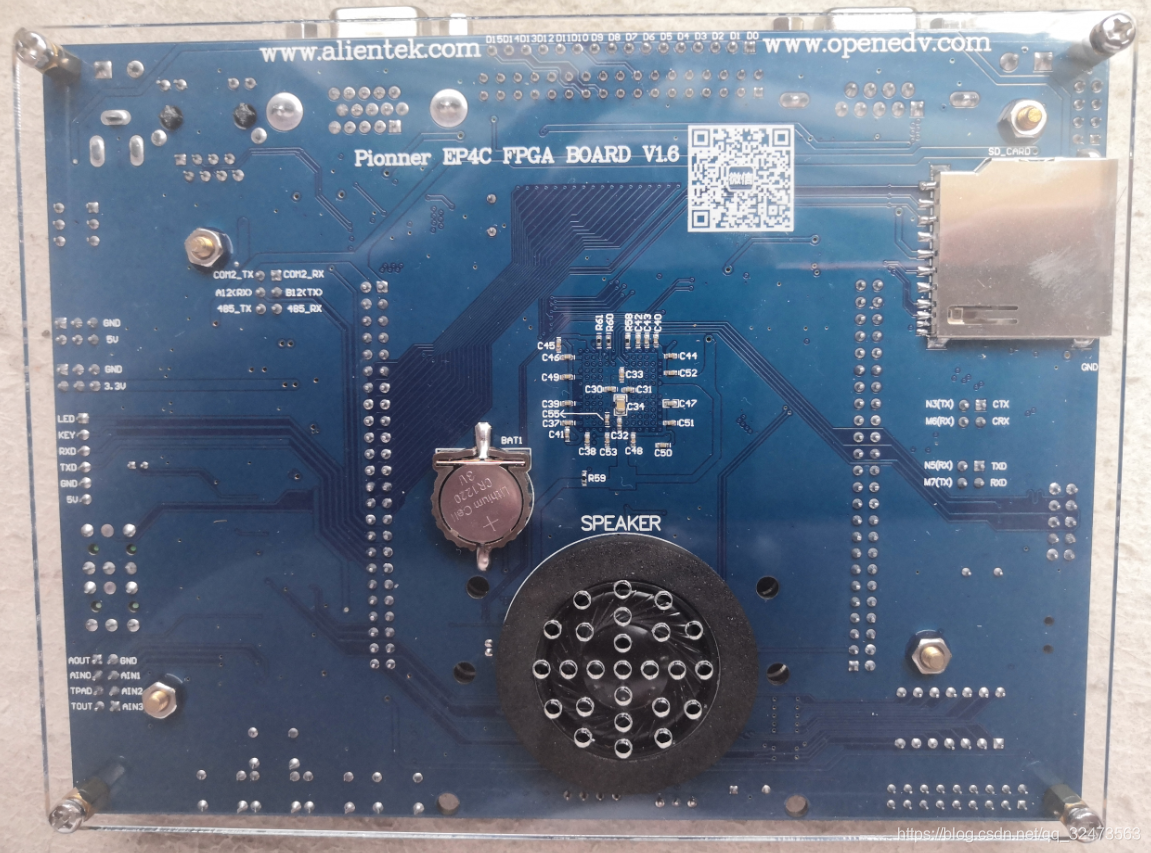

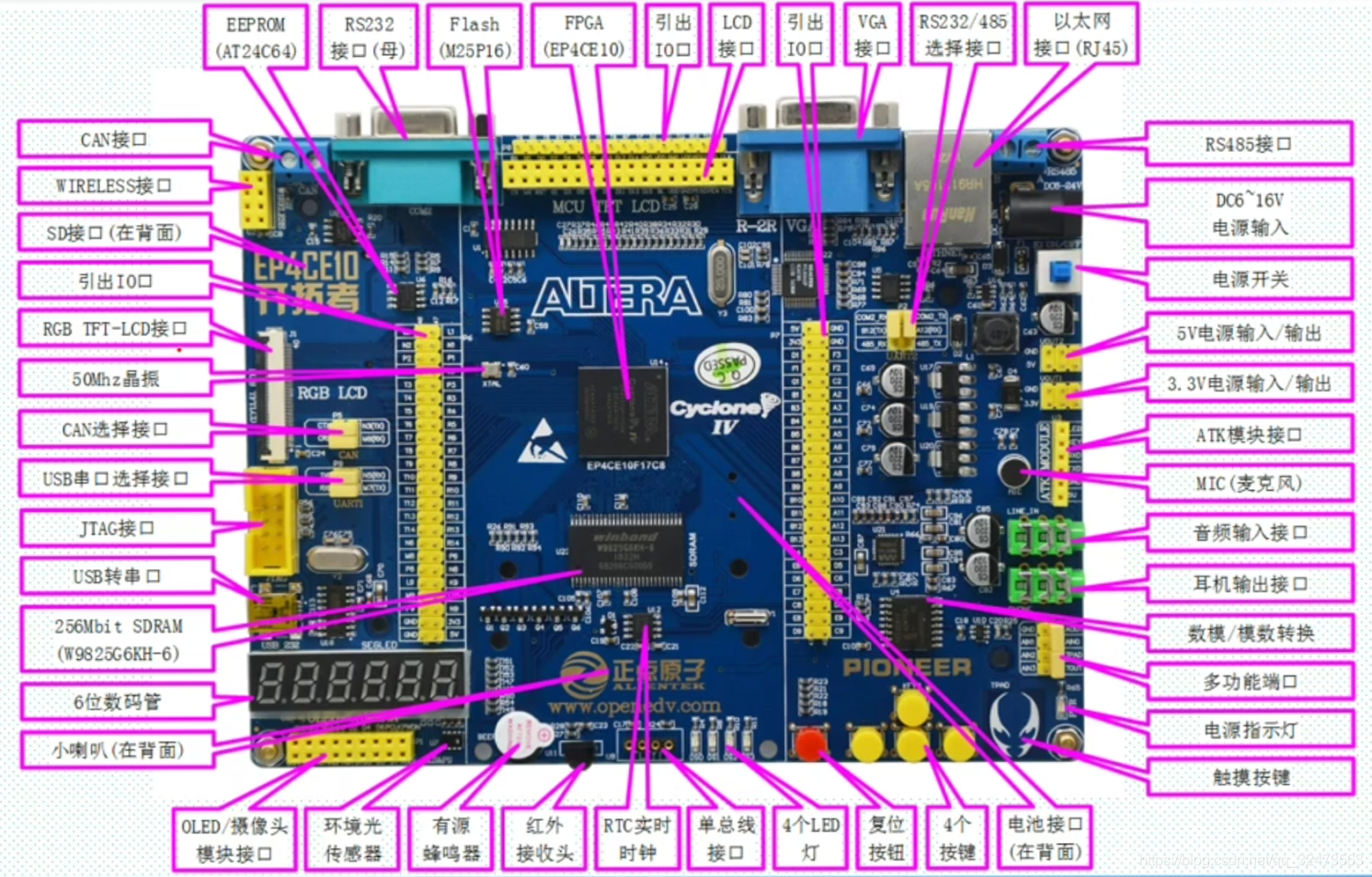

开发板 - EP4CE10

开发板综合测试

FPGA-test

FPGA简介

- FPGA(Field Programmable Gate Array)现场可编程门阵列。

- 半定制电路

ZYNQ:FPGA + ARM

FPGA & ARM

| 单片机 | FPGA |

|---|---|

| 哈佛总线结构、冯诺依曼结构 | 查找表 |

| 串行执行 | 并行执行 |

| 软件范畴 | 硬件范畴 |

| C、汇编编程 | Verilog HDL、VHDL硬件描述语言编程 |

FPGA制造商

- Xilinx(赛灵思):发明FPGA 50%

- Altera(阿尔特拉),现已被Intel收购 40%

- Lattice(莱迪思)

- Microsemi(美高森美)

FPGA优势

- 运行速度快

- 引脚多(数百上千),适合大规模系统设计

- 并行执行,效率高

- 包含大量IP核,方便开发

- 设计灵活

FPGA应用领域

- 通信领域

- 算法实现

- 嵌入式

- 5G无线、自动驾驶、人工智能、云计算

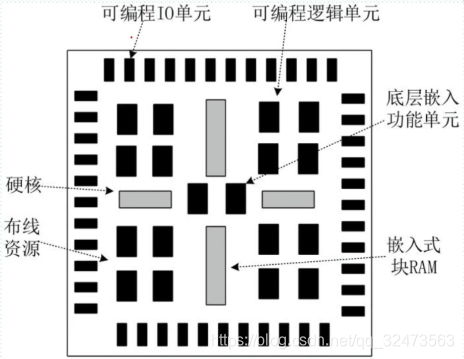

FPGA内部结构

- **可编程IO单元:**可编程IO、上下拉电阻、驱动电流大小

- **可编程逻辑单元:**查找表(LUT)、寄存器

- **底层嵌入式功能:**锁相环、DSP、。。。

- **块RAM:**存储器、RAM、ROM

- **布线资源:**影响驱动能力、传输速度

- 硬核:

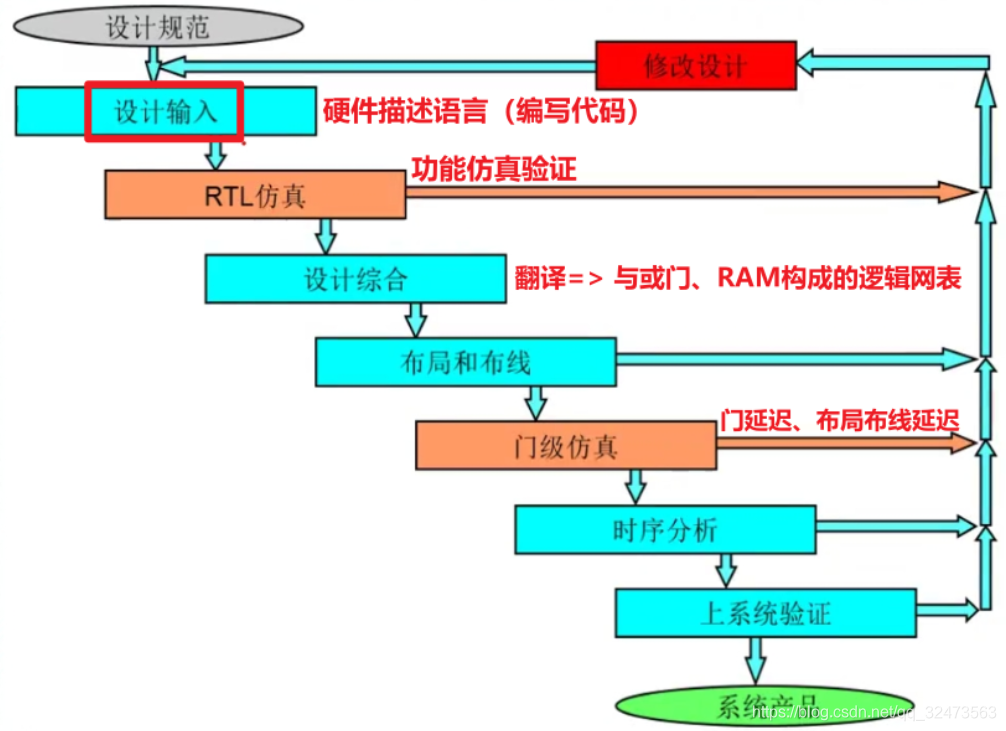

FPGA开发流程

- 设计输入最重要。

Quartus II

- Quartus II 是Altera公司为FPGA/CPLD芯片设计的集成开发软件。

- 输入形式:原理图、VHDL、Verilog、HDL。

- 包含PFGA完整实际流程:设计输入、综合适配、仿真、下载。

开发流程

工程路径 =>打开软件 =>新建工程 =>设计输入 =>配置工程 =>分析综合 =>分配引脚 =>编译工程sof =>下载程序

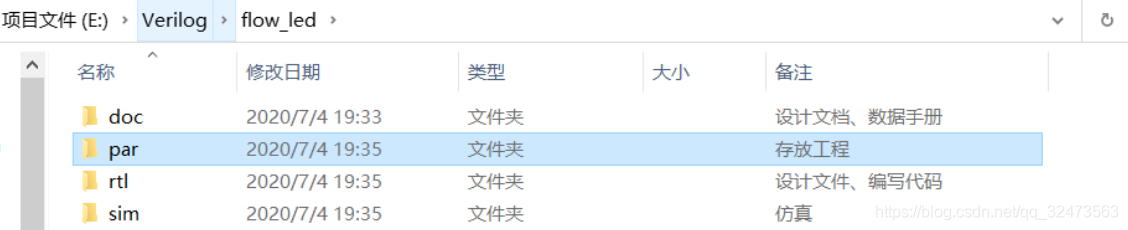

0、工程路径

1、打开软件

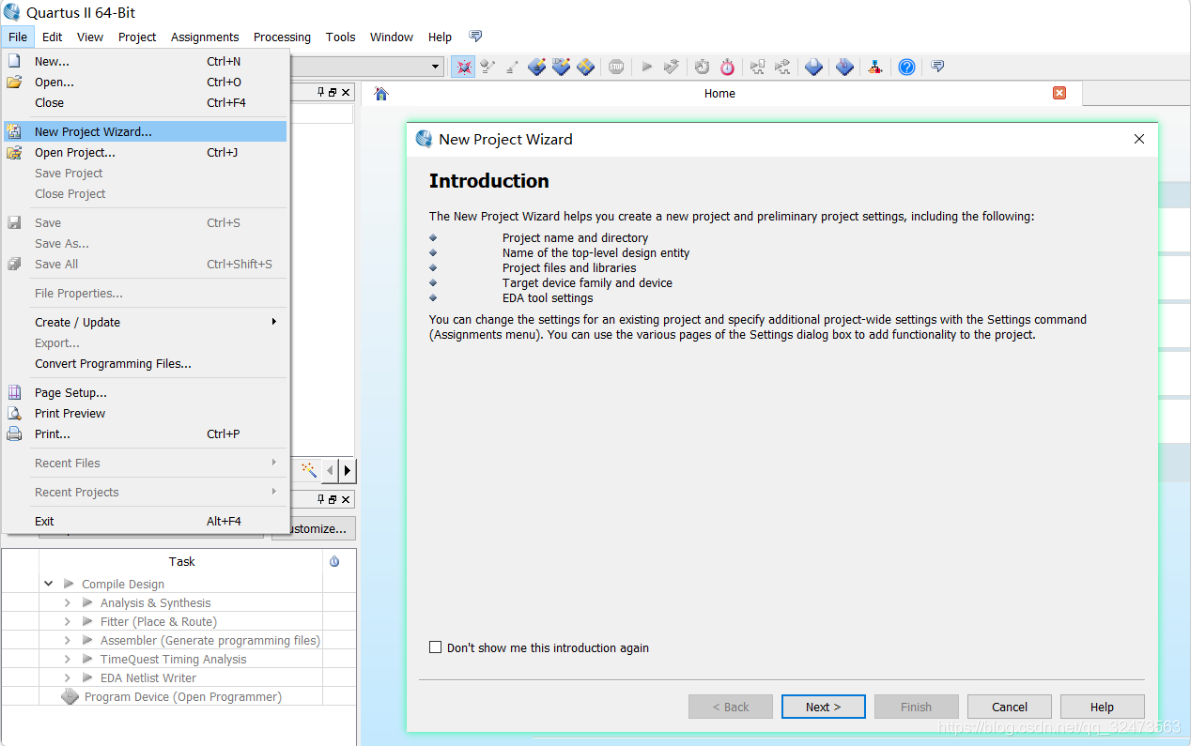

2、新建工程

1/5 选择路径、工程名

2/5 添加已有的设计文件

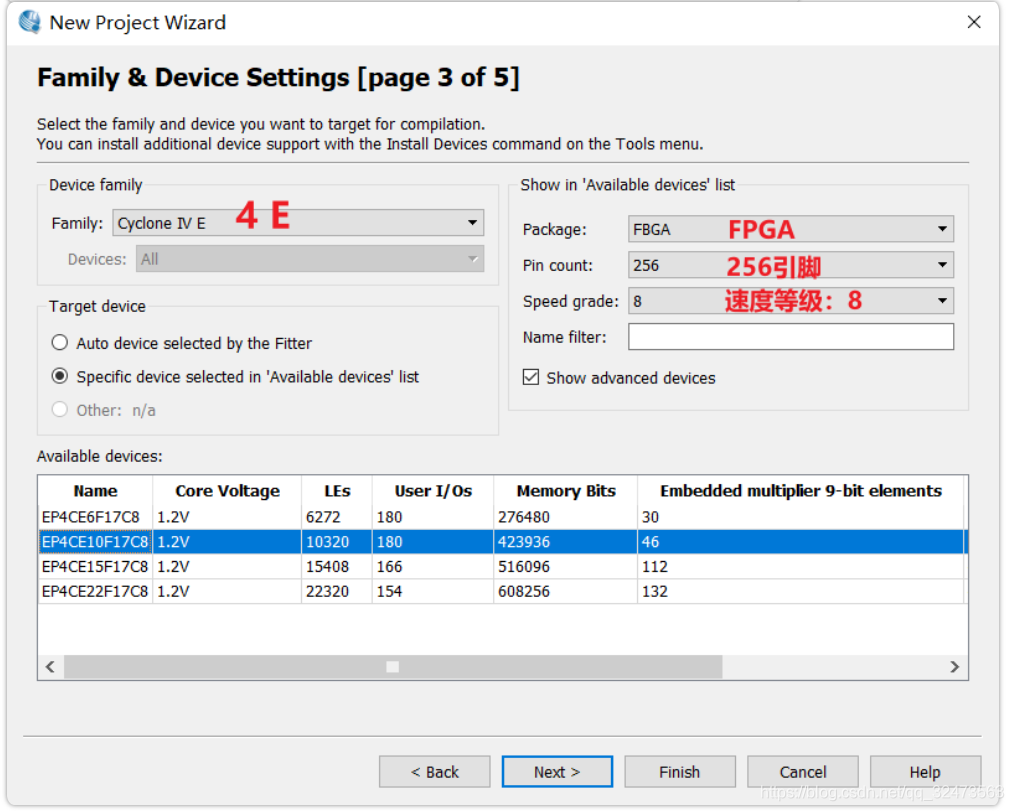

3/5 芯片选型:EP4CE10

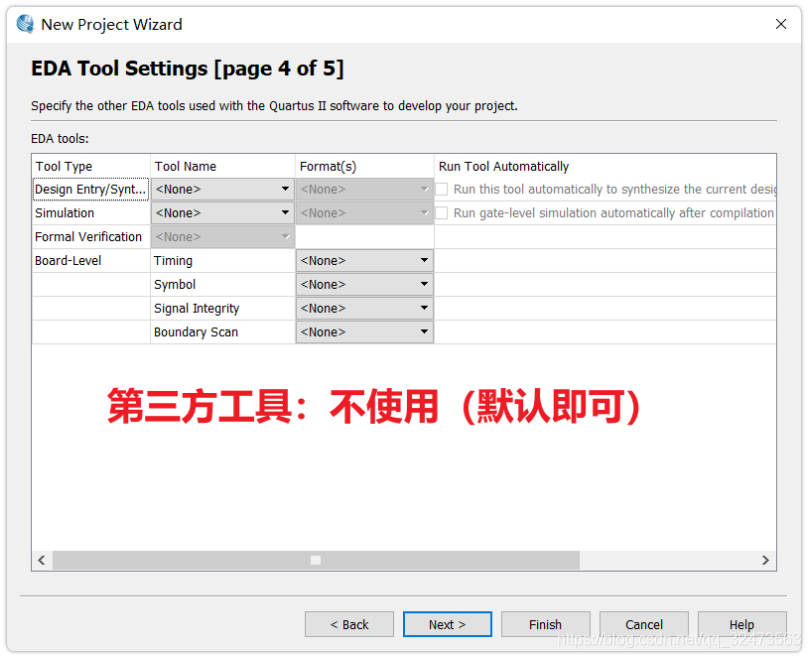

4/5 第三方工具,不使用

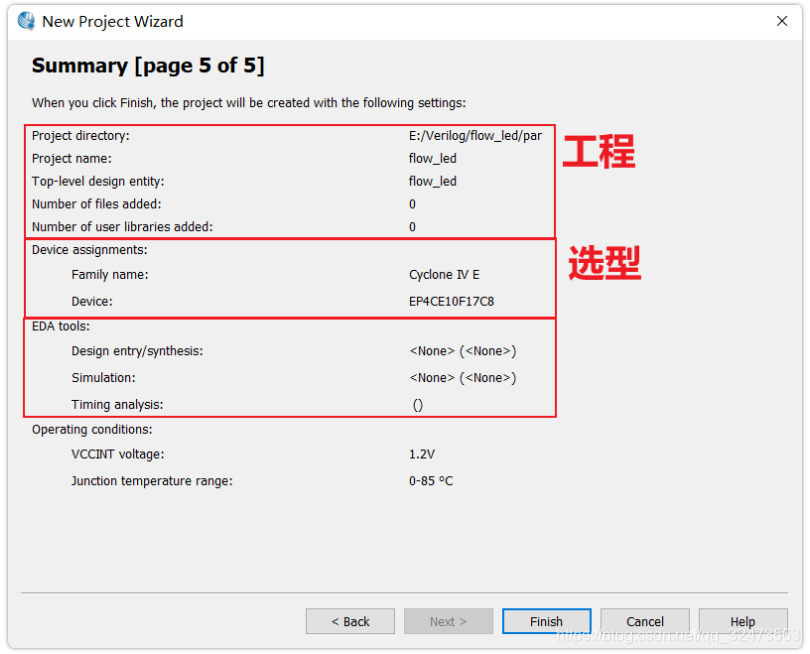

5/5 总结

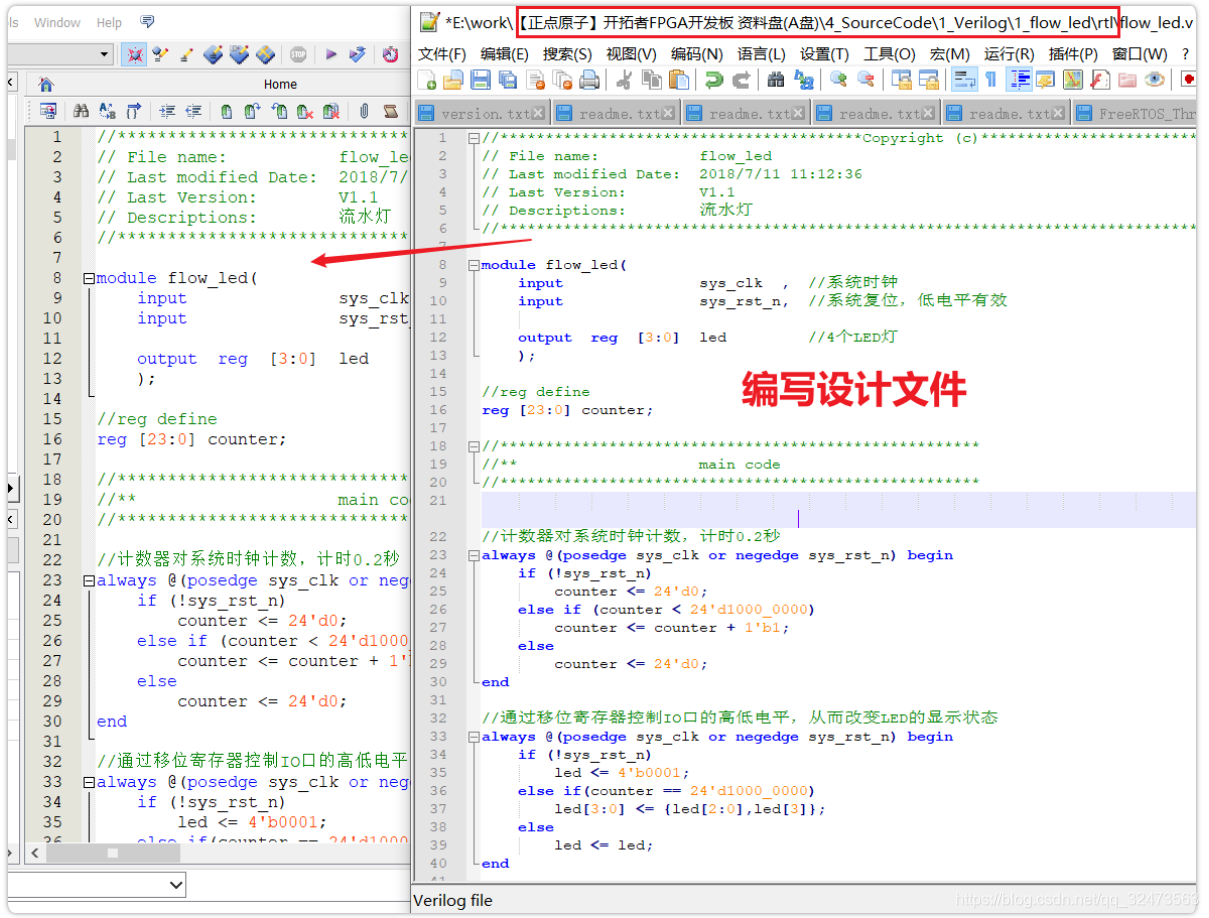

3、设计输入

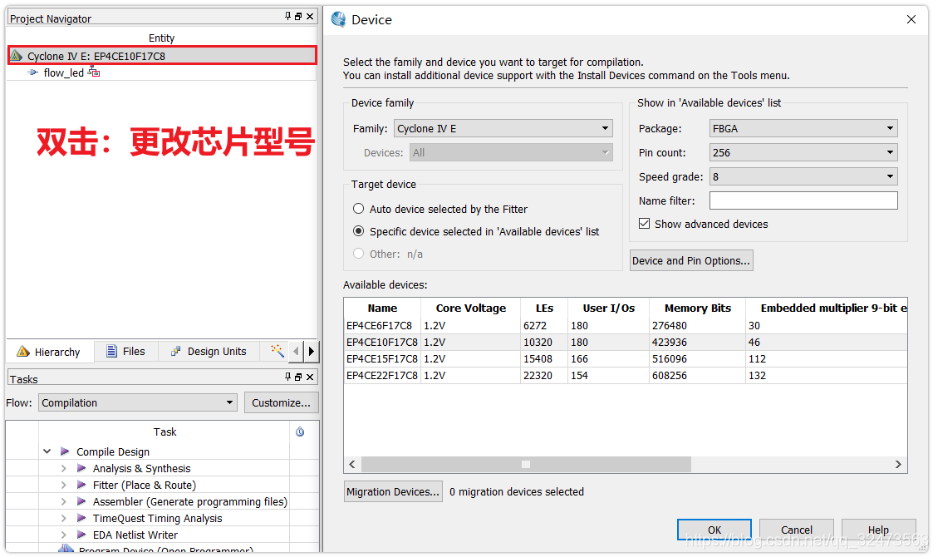

- 双击,可更改芯片型号

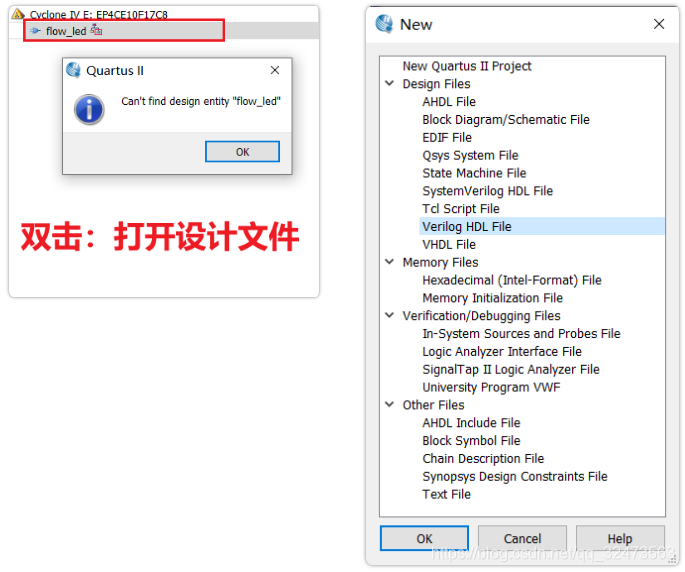

1、双击,无设计文件时:File => New => Verilog HDL File

2、编写设计文件

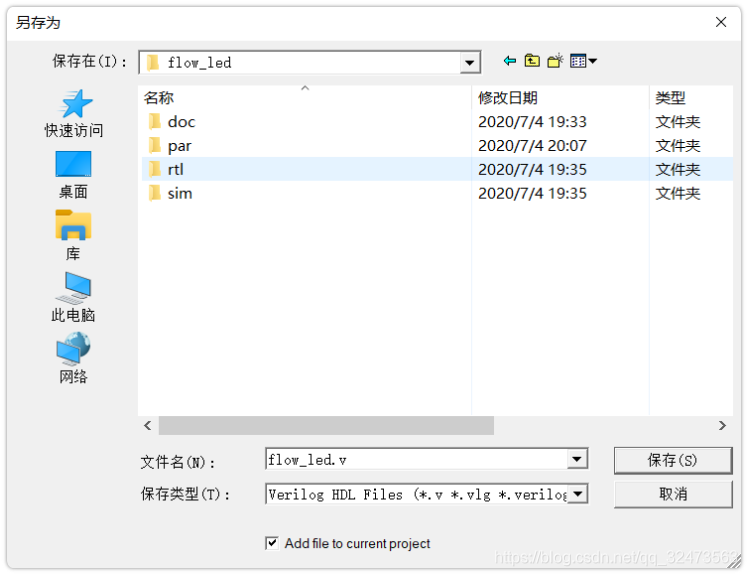

3、保存 设计文件

- 保存到rtl文件夹中;

- 文件名与

module名一致。

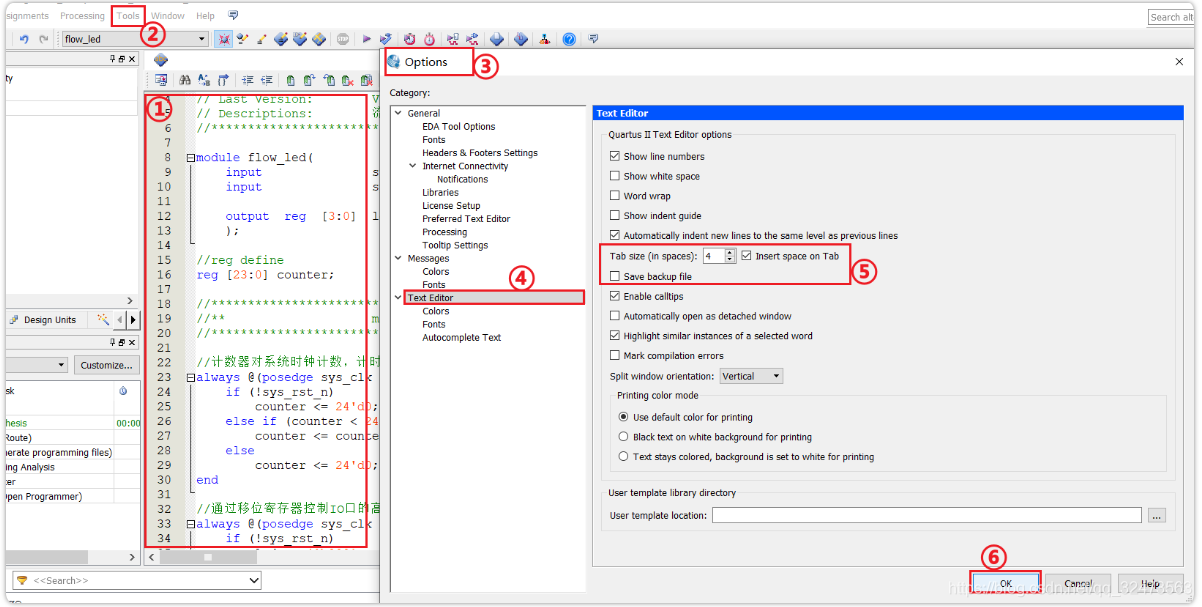

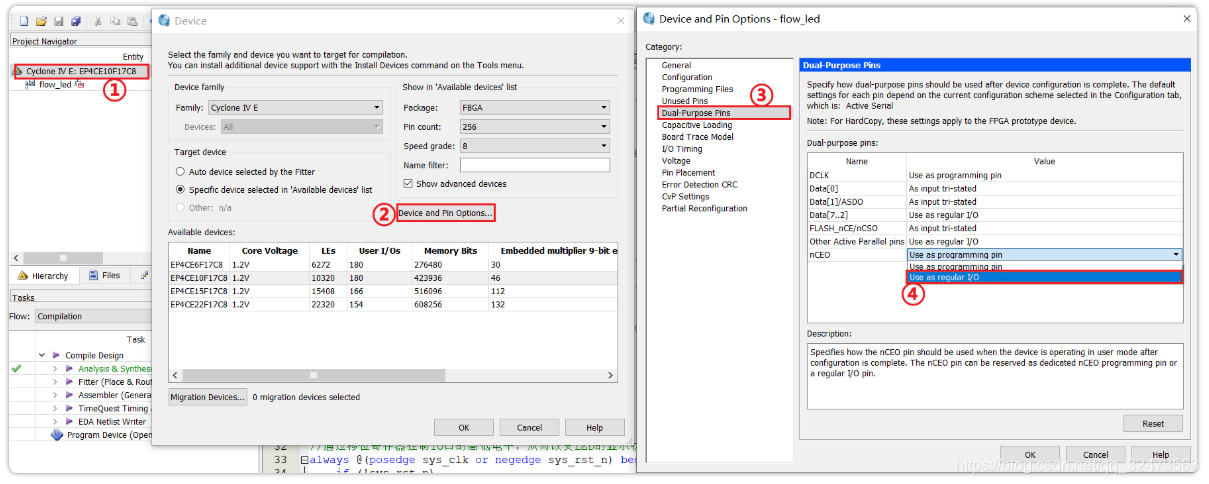

4、配置工程

TAB 配置

双用引脚,改为GPIO功能:

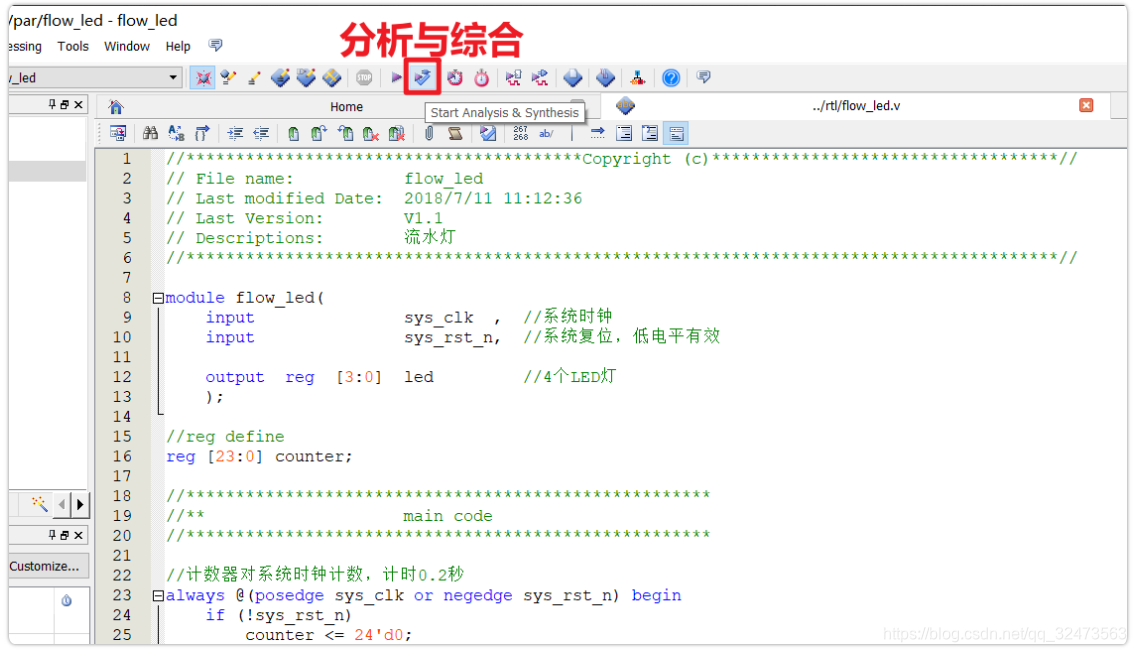

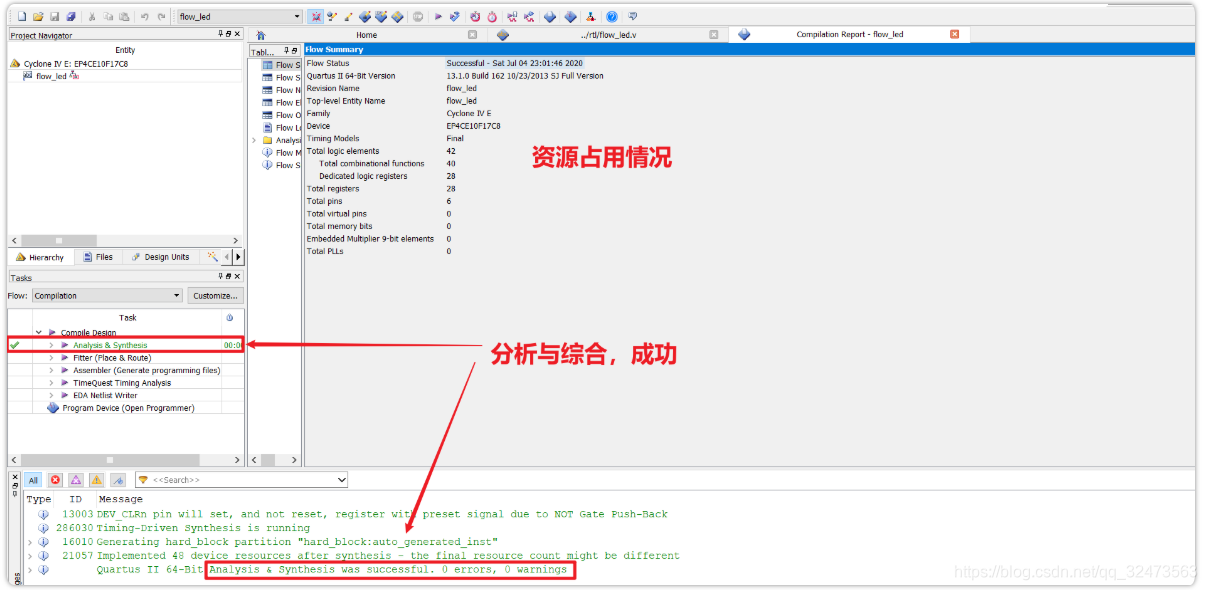

5、分析与综合

- 启动:分析与综合

- 分析与综合结果

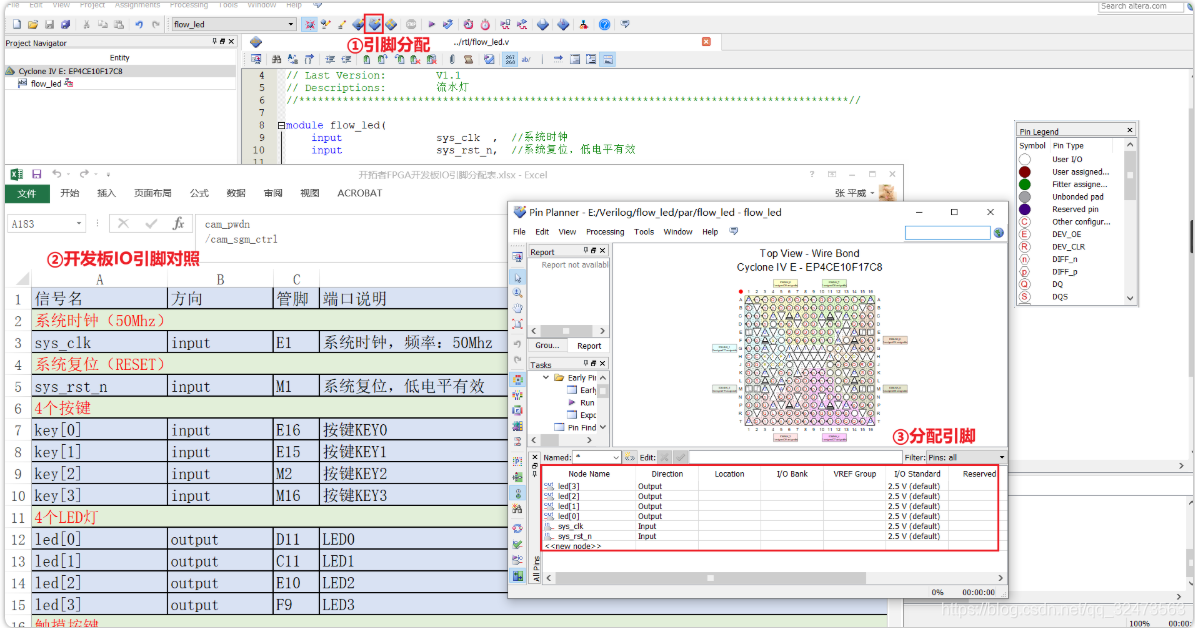

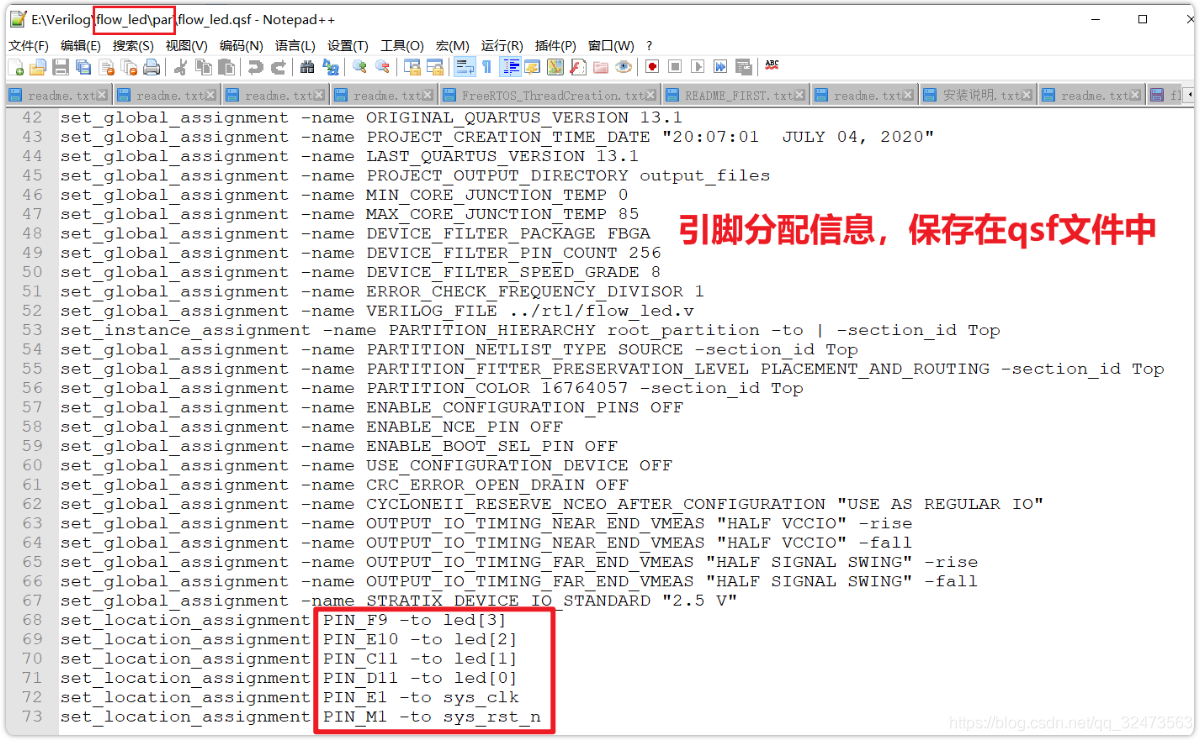

6、引脚分配(Pin Planner)

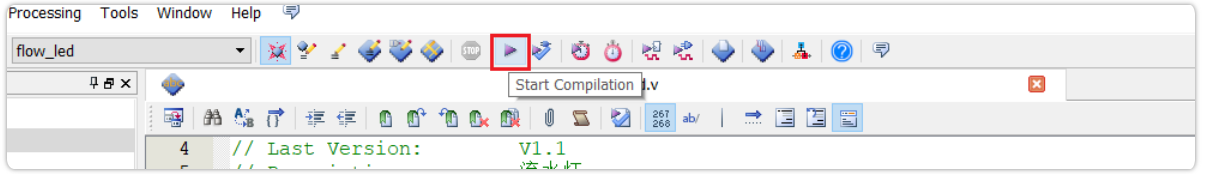

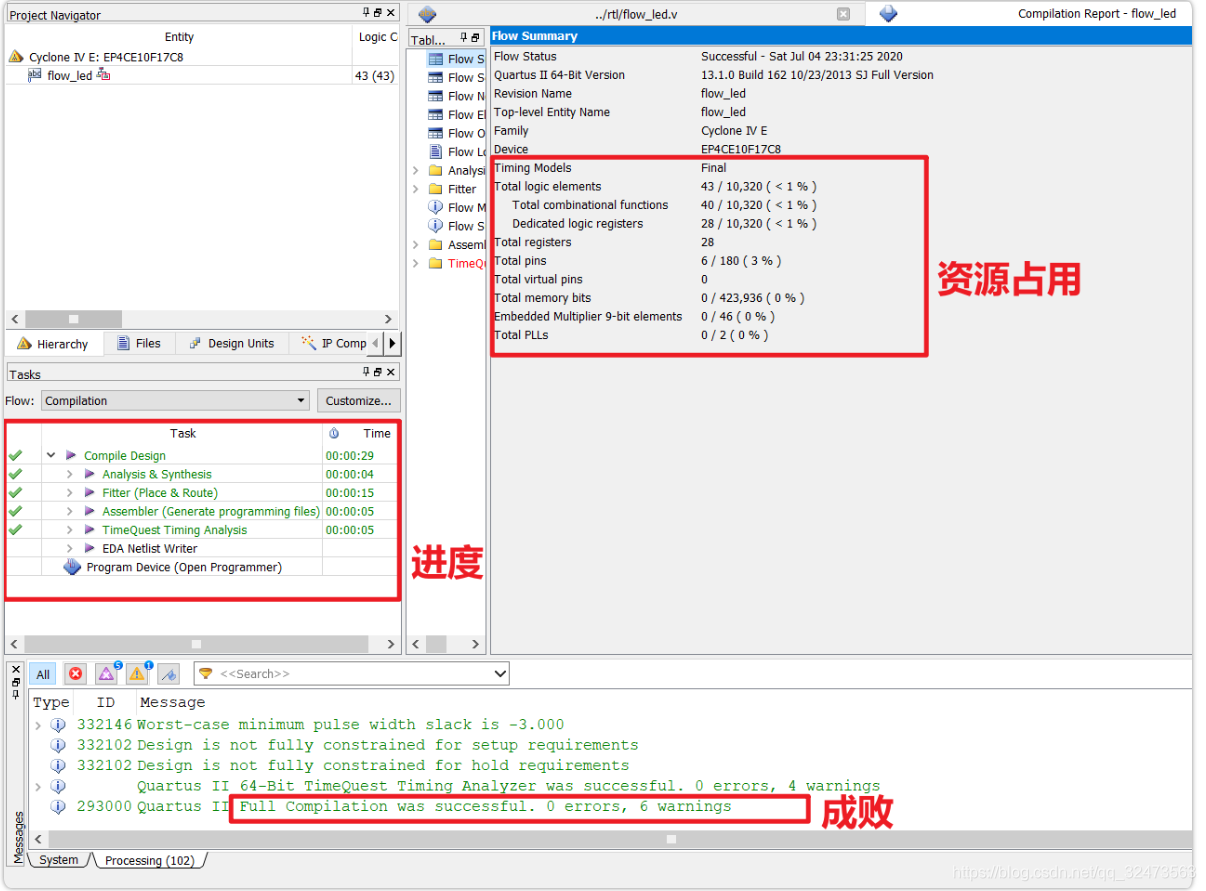

7、编译工程

- 开始编译

- 编译结果

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?