地址编号从80000H到BFFFFH且按字节编址的内存容量为__KB,若用16K×4bit的存储芯片够成该内存 ,共需_ _片。

总内存容量:尾数-首数+1

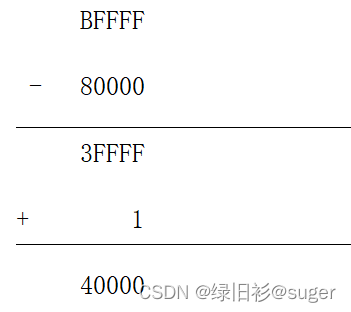

BFFFFH-80000H+1=40000H

B对应十进制的11,F为十六进制的最大数,所以F+1为0,向上进1,3+1=4,所以3FFFF+1=40000

所以从80000H到BFFFFH有40000H个地址单元。

十六进制的40000转换为十进制:

40000H=0×16^ 0+0×16^ 1+0×16^ 2+0×16^ 3+4×16^ 4 =4×16^4 =

2^2×(2 ^4) ^4 = 2^18,即256KB。

若用16K×4bit的存储芯片够成该内存 ,需要(256K×8bit)÷(16K×4bit)=(256X1024X8)/(16X1024X4)=32 片

注:其中256K×8bit 为:1B=8bit 1K=1024 所以 256KB=256 X 1024 X 8

4478

4478

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?