写策略 Writing Policy

缓存的写策略指的是确定何时将数据写入缓存或主存的策略。

写命中 Write Hit

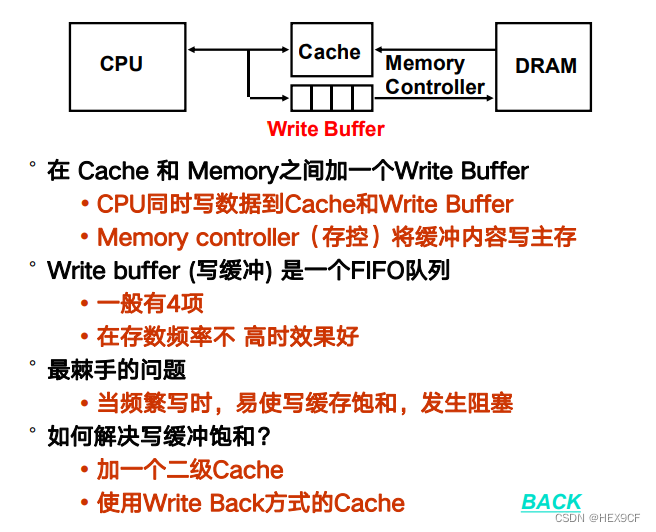

全写法 Write Through

在全写法策略中,每次发生写操作时都会将数据同时写入缓存和主存。这样可以保证数据的一致性,但会增加主存的写入操作,降低写入性能。需要设置写缓存(Write Buffer)。

写会法 Write Back

在写回策略中,当缓存中的数据发生变化时,只会在发生替换时才将修改过的数据写回主存,而不会立即将数据写回到主存。这样可以减少对主存的写入次数,提高性能,但可能会导致数据不一致性,因为修改过的数据在缓存中比在主存中更为新,如果系统出现异常情况,可能会导致数据丢失。每个Cache行必须设置一个标志位(脏位),以反映此块是否被CPU修改过。

写不命中 Write Miss

写分配 Write Allocate

写分配指的是当发生缓存写操作时,需要将相应的数据块装入缓存中。写回和写直达策略都可能采用写分配。

非写分配 No-write Allocate

非写分配指的是当发生缓存写操作时,不会将相应的数据块装入缓存,而是直接写入主存。这种策略一般用于写直达策略中。

本文详细解释了缓存的写策略,包括全写法(WriteThrough)确保数据一致性但影响性能,写回策略(WriteBack)提高性能但可能导致数据不一致,以及写不命中和写分配/非写分配的区别。

本文详细解释了缓存的写策略,包括全写法(WriteThrough)确保数据一致性但影响性能,写回策略(WriteBack)提高性能但可能导致数据不一致,以及写不命中和写分配/非写分配的区别。

1543

1543

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?