计算机组成原理 第三章 - Cache写策略

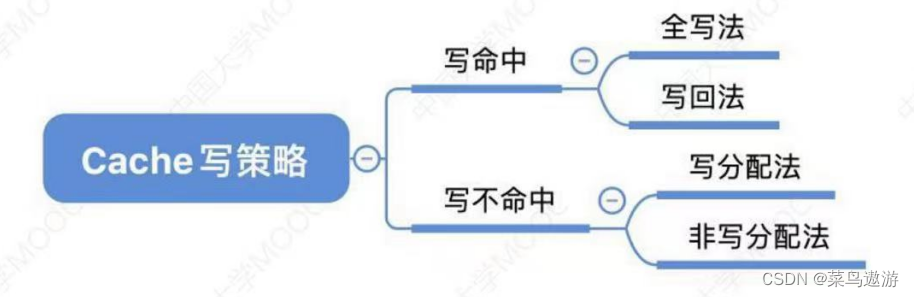

1.思维导图

2.知识图谱

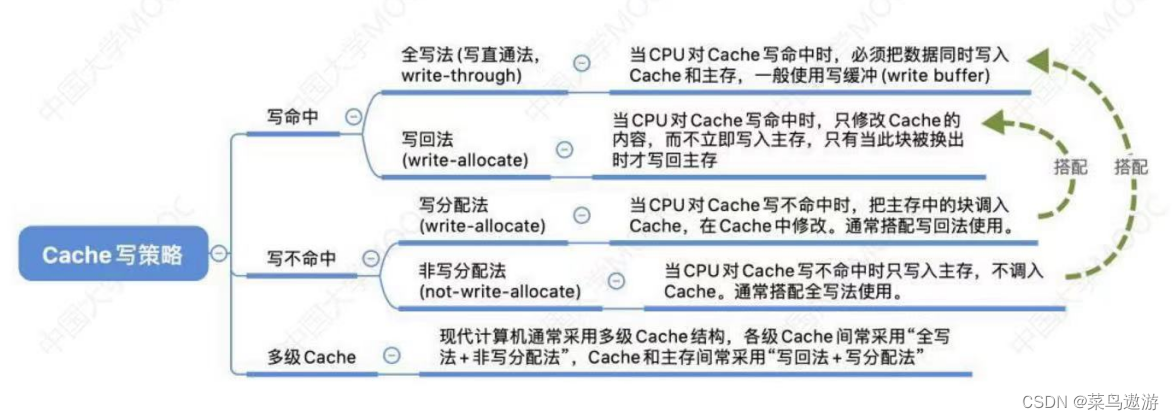

Cache写策略

写命中

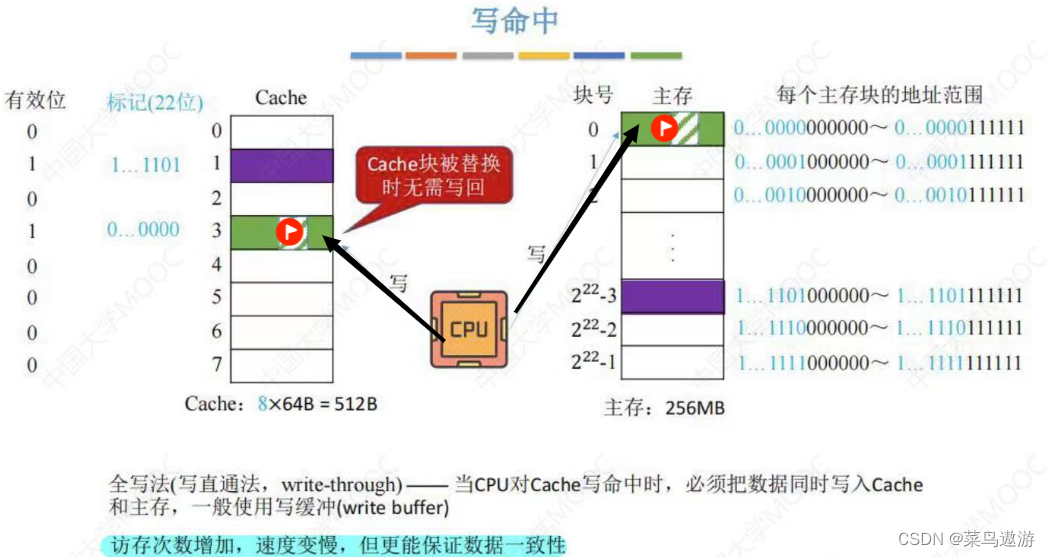

①全写法(直写法)

将数据同时写入Cache和主存,一般使用写缓冲(write buffer)【SRAM实现的 FIFO队列】

优点:保证数据一致性。在写操作不频繁时,效果好。

缺点:访问次数增加,速度变慢。写操作频繁时,易发生写缓冲饱和发生阻塞。

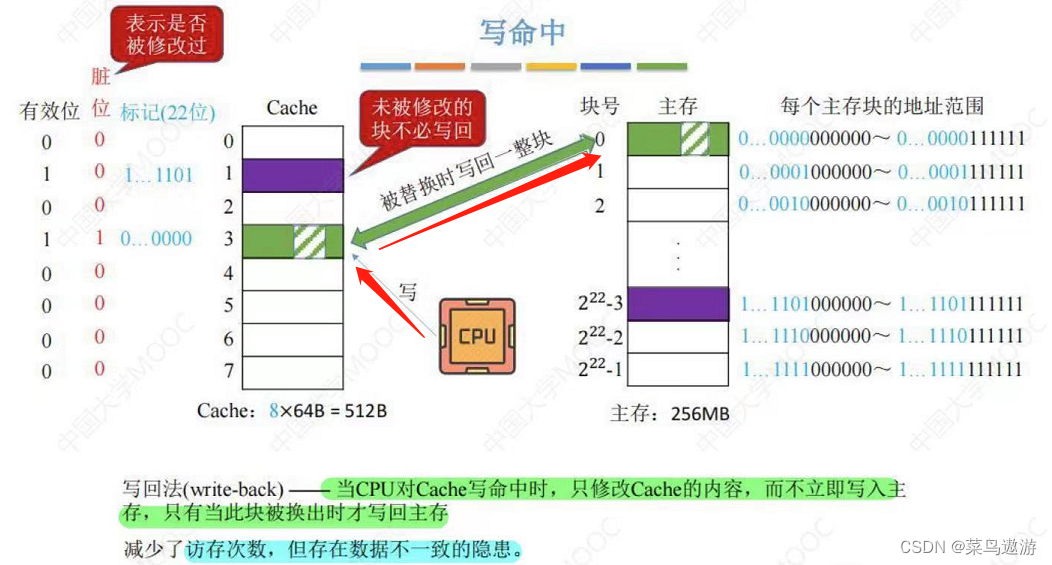

②写回法 (回写法)

先将数据在Cache中修改,等到数据所在块被替回时,通过脏位(为1)写回主存

优点:减少了访问次数。

缺点:存在数据不一致隐患。增加了一位写回判断位(脏位)。

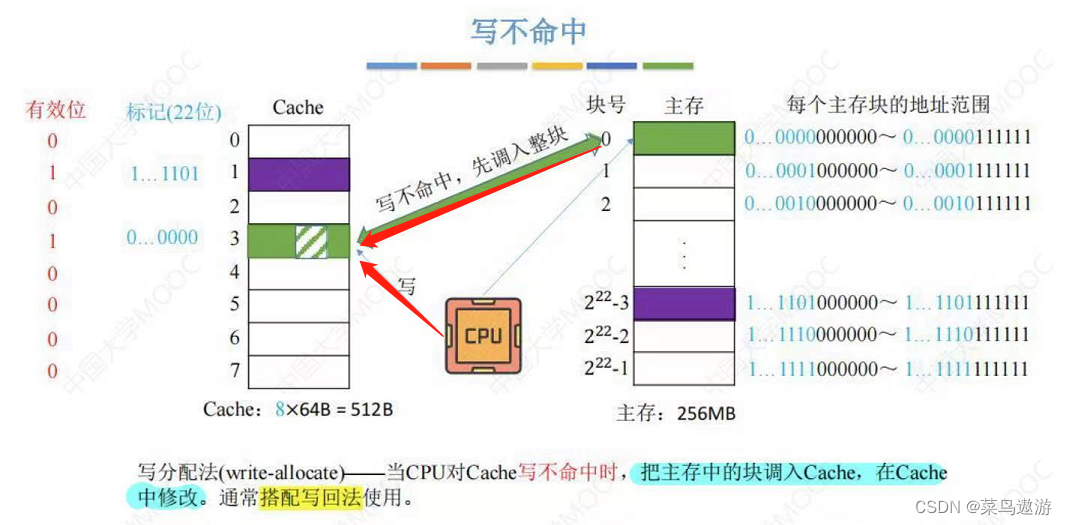

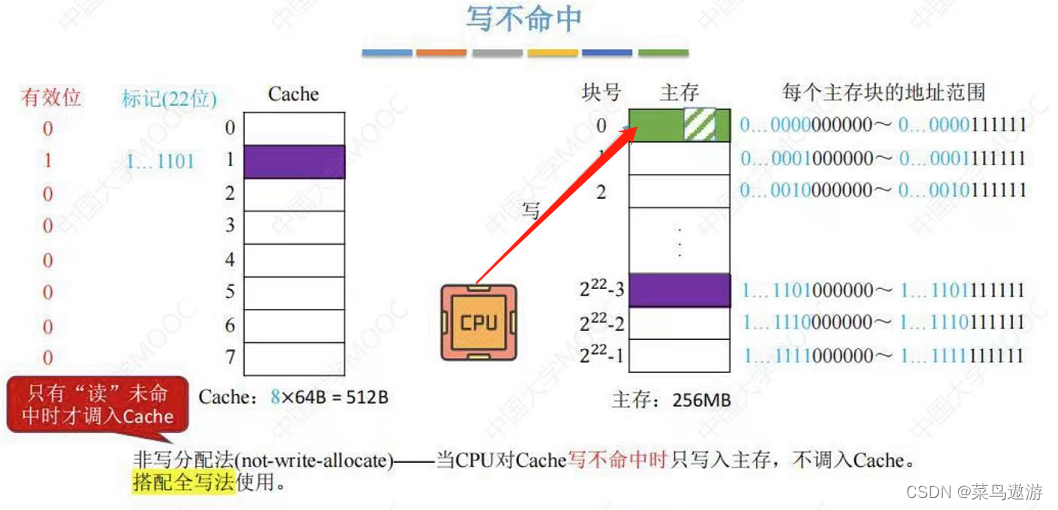

写不命中

①写分配法

写不命中时,把主存中的块调入Cache,在Cache中修改。

搭配写回法使用

②非写分配法

cup在Cache中未命中时,不将主存内容调入Cache,直接修改主存内容。

搭配全写法使用。

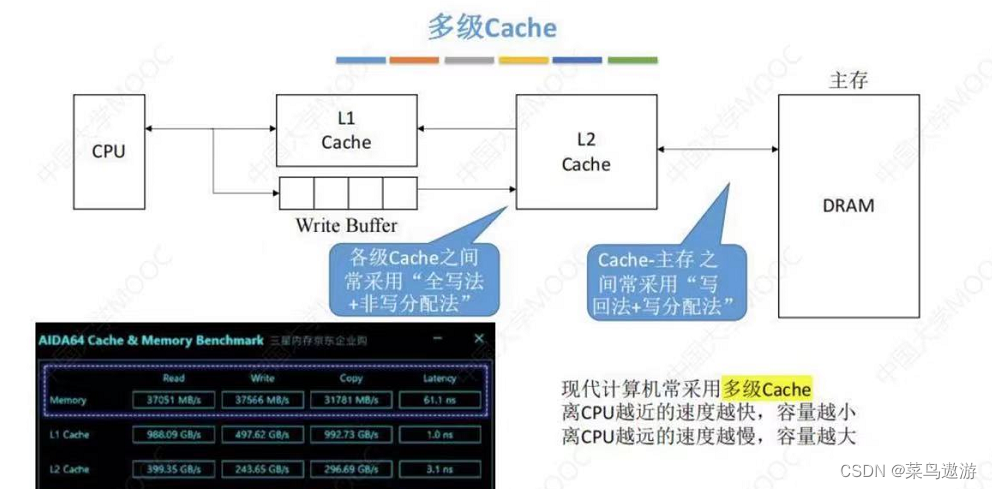

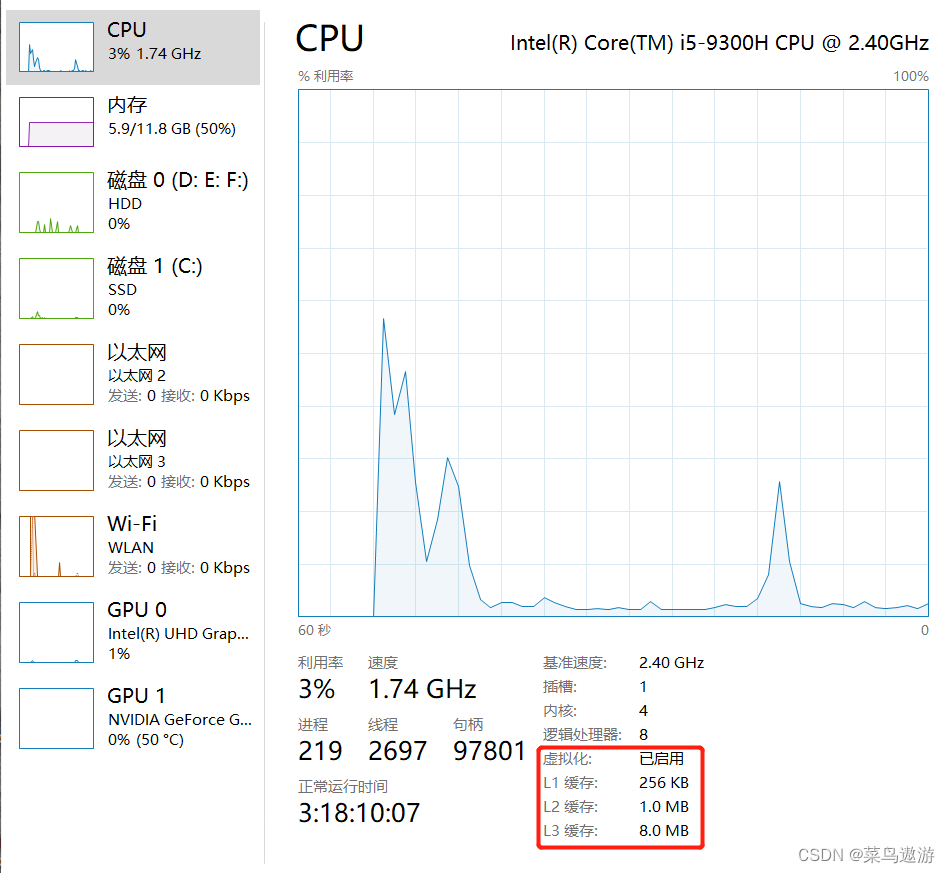

多级Cache

不同Cache的价位,速度也各不相同,通常也采取不同的写策略。

现代处理器系统,L1 Cache 层面, 指令Cache与数据Cache 通常 分离 ,多数情况下L1 指令 Cache 是只读的 。

在L2,L3中一般混合存放。

指令Cache与数据分离(14年真题):

采用指令Cache与数据Cache分离的主要目的:D

A:降低Cache的缺失损失 B:提高Cache的命中率

C:降低CPU平均访问时间 D:减少指令流水线资源冲突

解析:指令Cache与数据Cache分离后,取指和取数分别到不同Cache中寻找,则指令流水线中取值部分和取数可以避免冲突,即减少指令流水线冲突。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?