概述

这篇文章,只要介绍自己设计了一款开发板。只要是两方面:一原厂提供的开发板太贵;二没有自己设计的功能多,所以才自己设计了此款开发板。

此开发板分有两块设计,top_board与bottom_board。这里说明下,原理图尺寸太大截图原因看不清楚正常。第二也半属于商业机密,不完全开放请了解,谢谢。

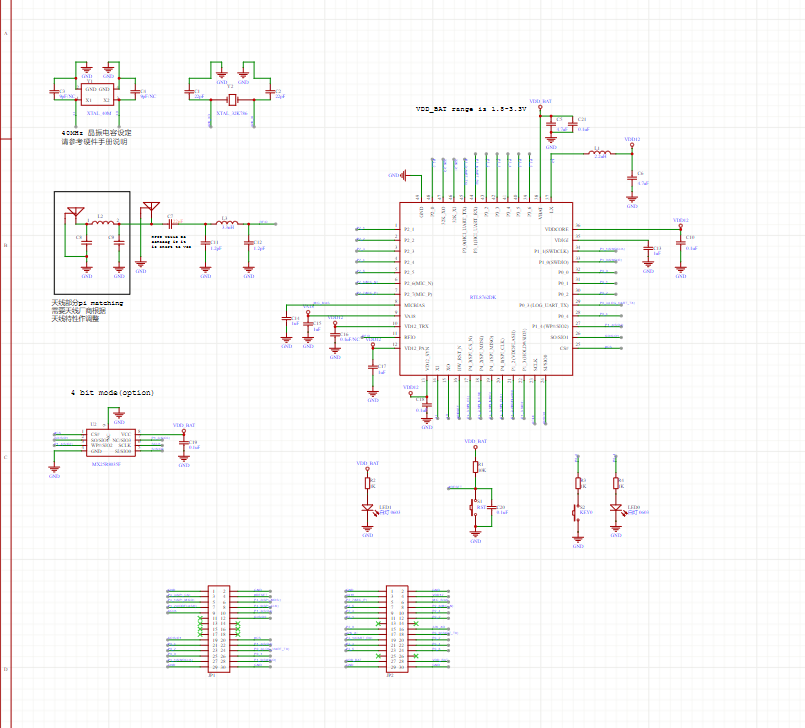

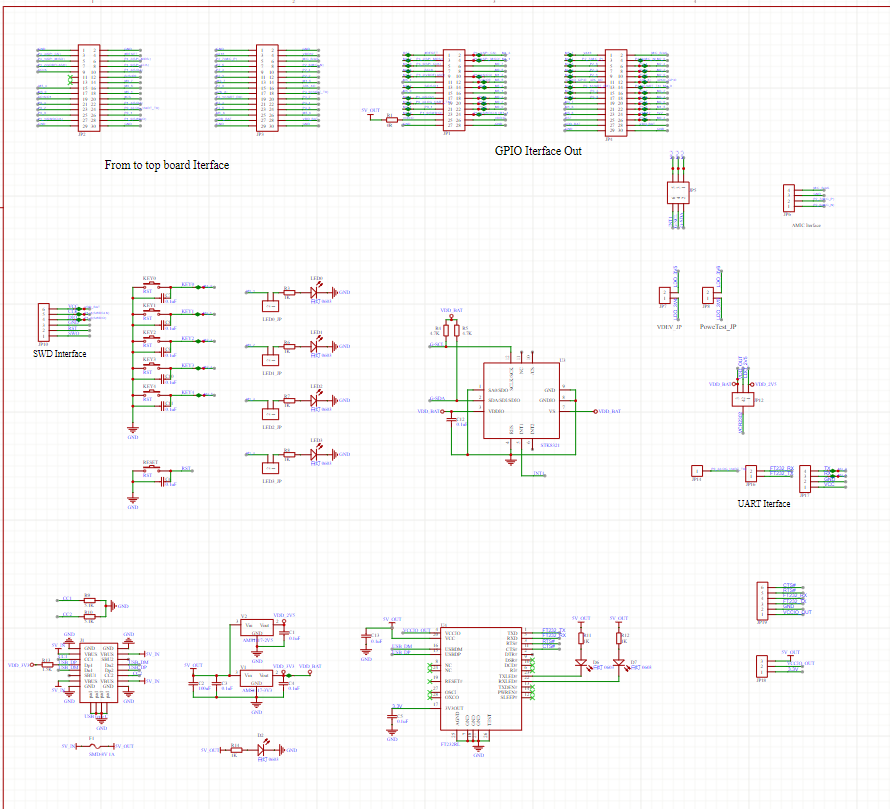

一、原理图

1、top_board

2、bottom_board

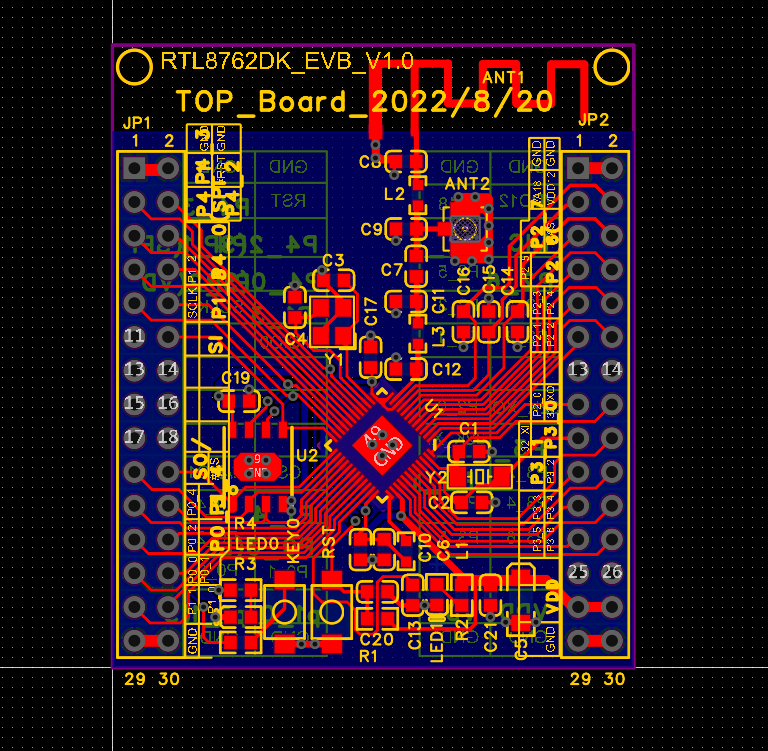

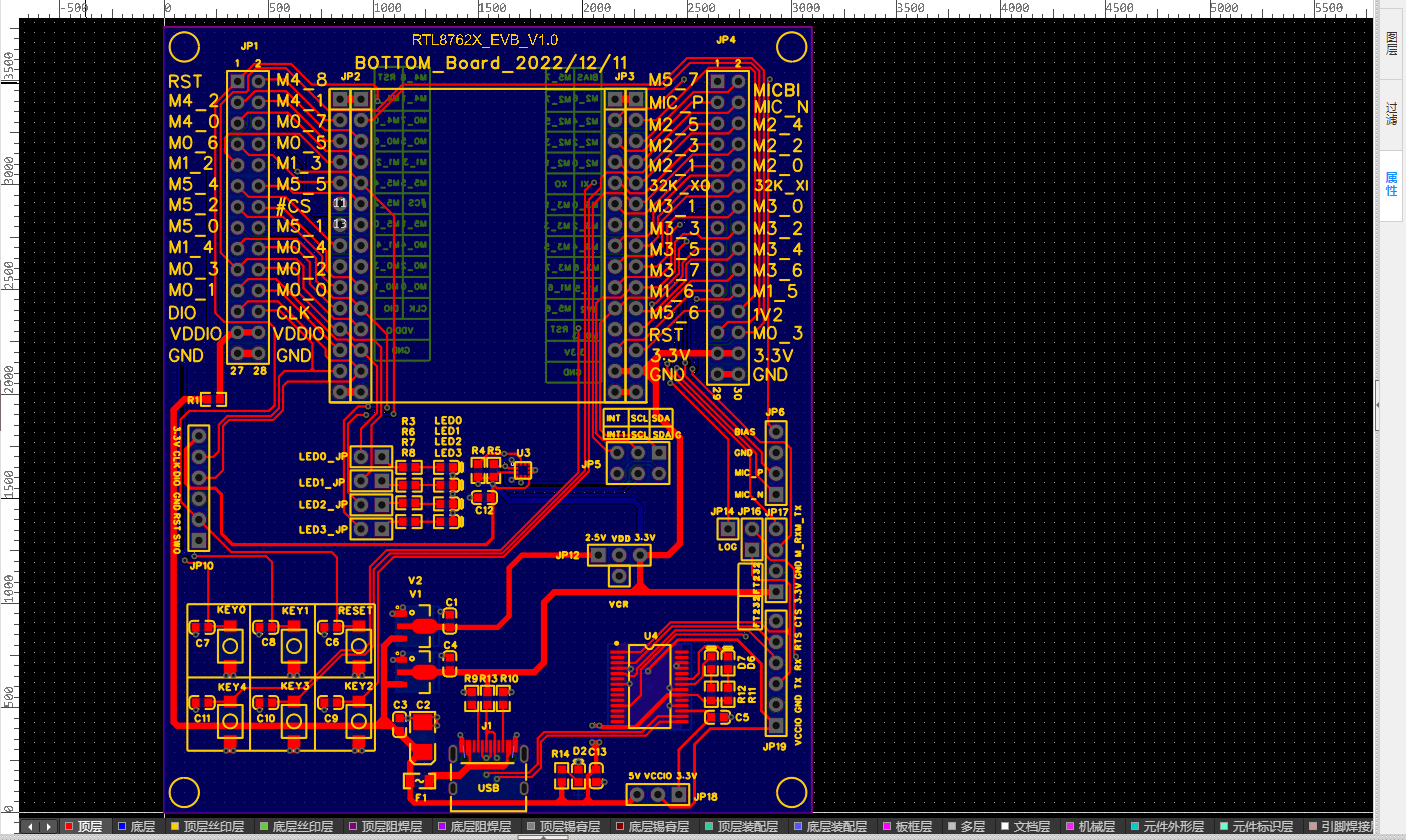

二、PCB

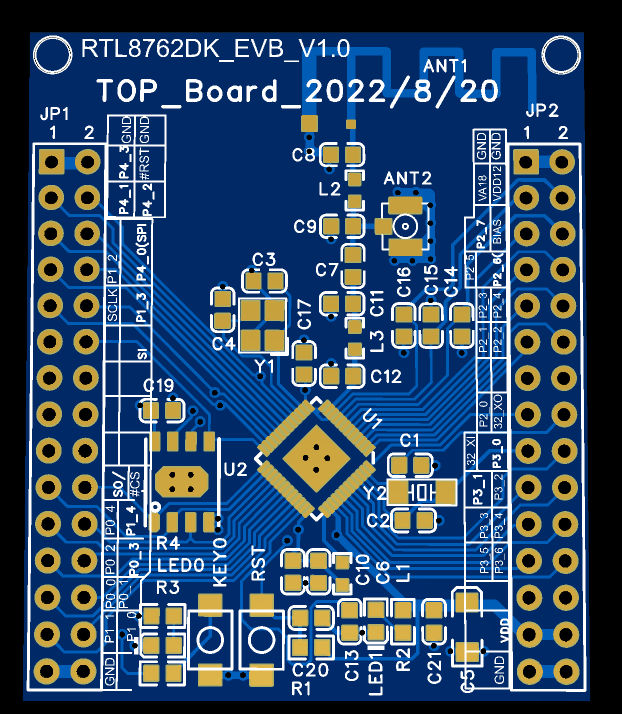

1、top_board

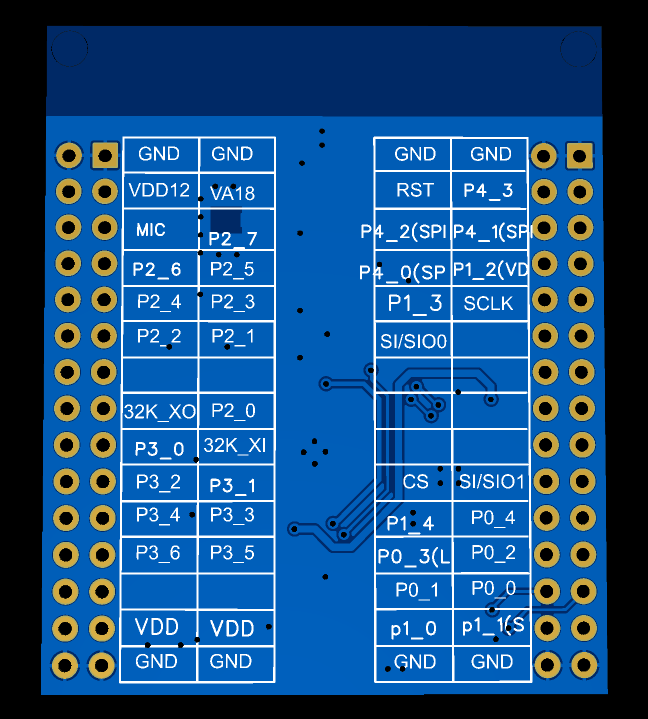

2、bottom_board

三、3D效果图

1、top_board

2、bottom_board

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8712

8712

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?