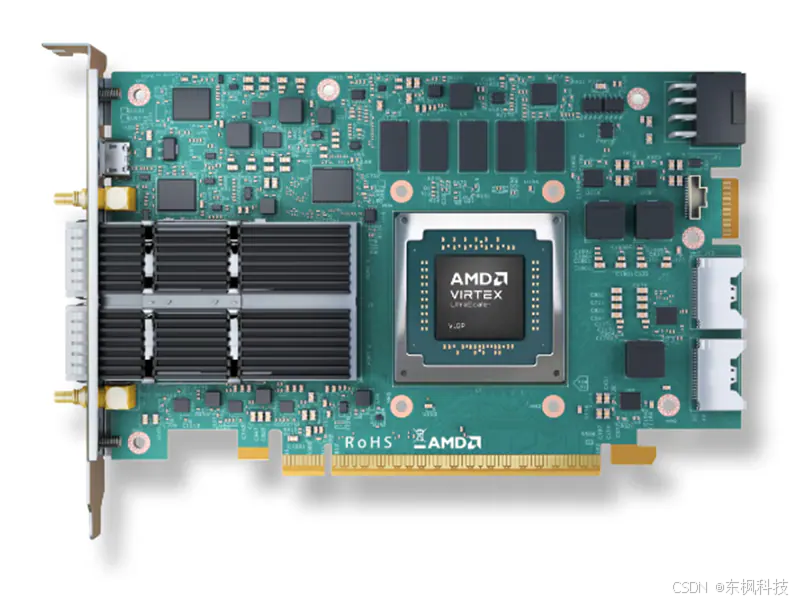

AMD / Xilinx Alveo™ UL3422 加速器

AMD / Xilinx Alveo™ UL3422 加速器提供超低延迟网络和灵活应变的硬件,支持纳秒级交易策略。AMD Virtex™ UltraScale+™ VU2P FPGA 为 AMD / Xilinx Alveo UL3422 加速器提供强大的支持。该加速器采用延迟优化的收发器技术,可实现快速交易执行和网络 I/O 交易延迟。其纤薄的全高半长 (FHHL) 外形尺寸使其能够在各种服务器配置中灵活部署,并支持传统的硬件设计工具、开发框架和生态系统 IP。

特征

- 专为超低延迟 (ULL) 性能而设计

- 定制 FPGA 设备和收发器架构,实现快速交易执行

- 与上一代产品相比,收发器延迟低于 3ns,性能提高 7 倍

- 纤薄外形,经济高效部署

- 针对机架空间、计算密度和电源效率进行了优化

- FHHL 外形尺寸适合多种服务器配置

- 易于开发,快速实现贸易

- 传统 FPGA 流程通过 AMD Vivado™ 工具与参考设计

- 用于支持 AI 的交易算法的开源 PyTorch 开发流程

- 来自生态系统合作伙伴的知识产权和交易开发框架

应用

- 自营交易员

- 做市商

- 对冲基金

- 经纪公司

- 交易所

- 市场数据供应商

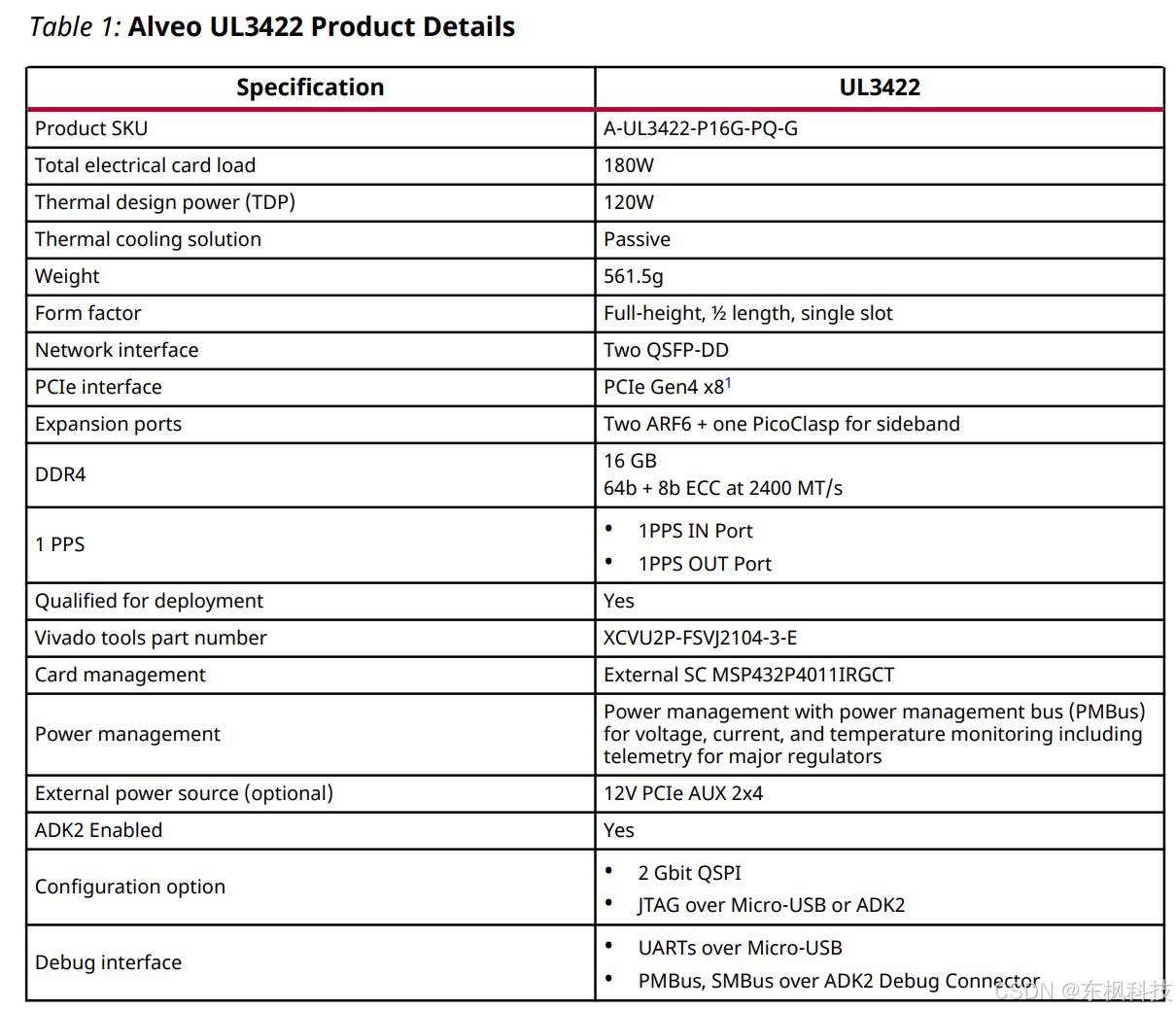

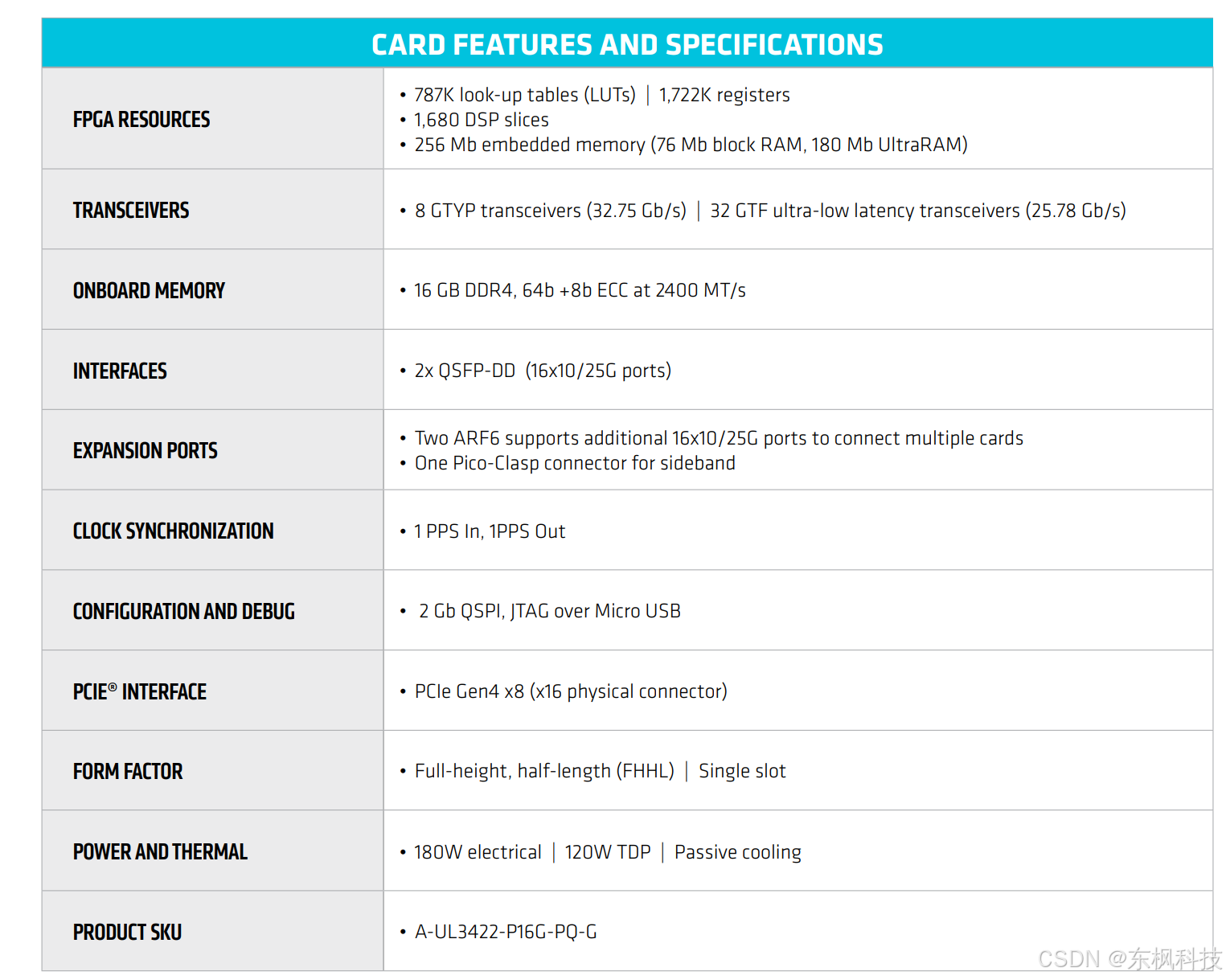

规格

- FPGA资源

787K 个查找表 (LUT)、1,722K 个寄存器

1,680 个 DSP 切片

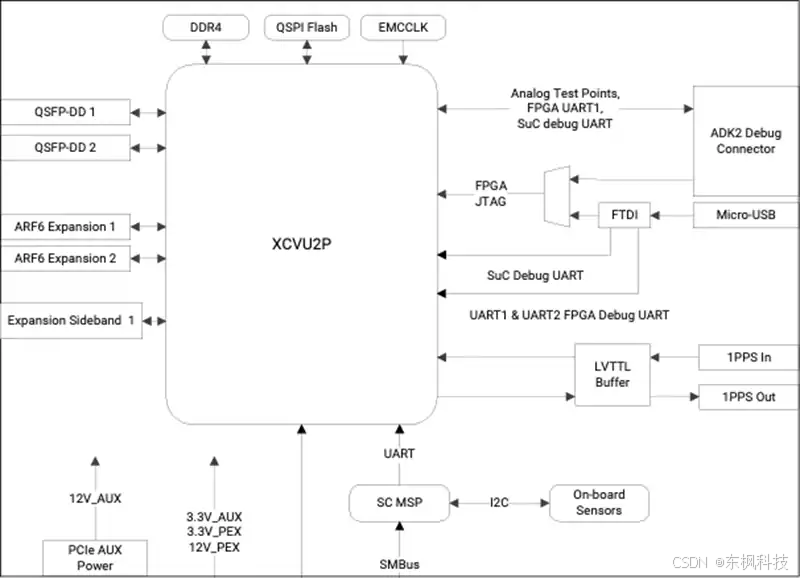

256Mb 嵌入式内存(76Mb 块 RAM、180Mb UltraRAM) - 收发器,8个GTYP收发器(32.75Gb/s),32个GTF超低延迟收发器(25.78Gb/s)

- 板载内存,16GB DDR4,64b +8b ECC,2400MT/s

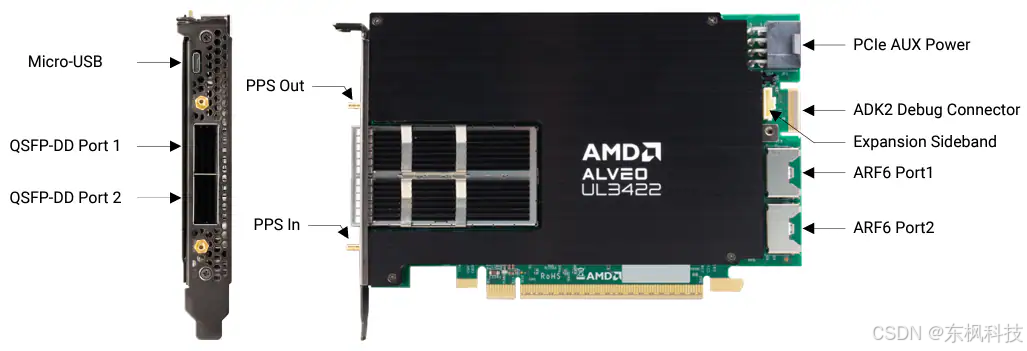

- 2个 QSFP-DD 接口(16个10/25G 端口)

- 同步,1PPS 输入,1PPS 输出

- 配置和调试、2Gb QSPI、通过 Micro USB PCIE® 的 JTAG

- 扩展端口

两个 ARF6 支持额外的 16x10/25G 端口以连接多张卡

一个用于边带 CLOCK 的 Pico-clasp 连接器 - PCIe Gen4 接口 x8(x16 物理连接器)

- 外形尺寸、全高、半长 (FHHL)、单插槽

- 功率和散热:180W 电能,120W TDP,被动冷却

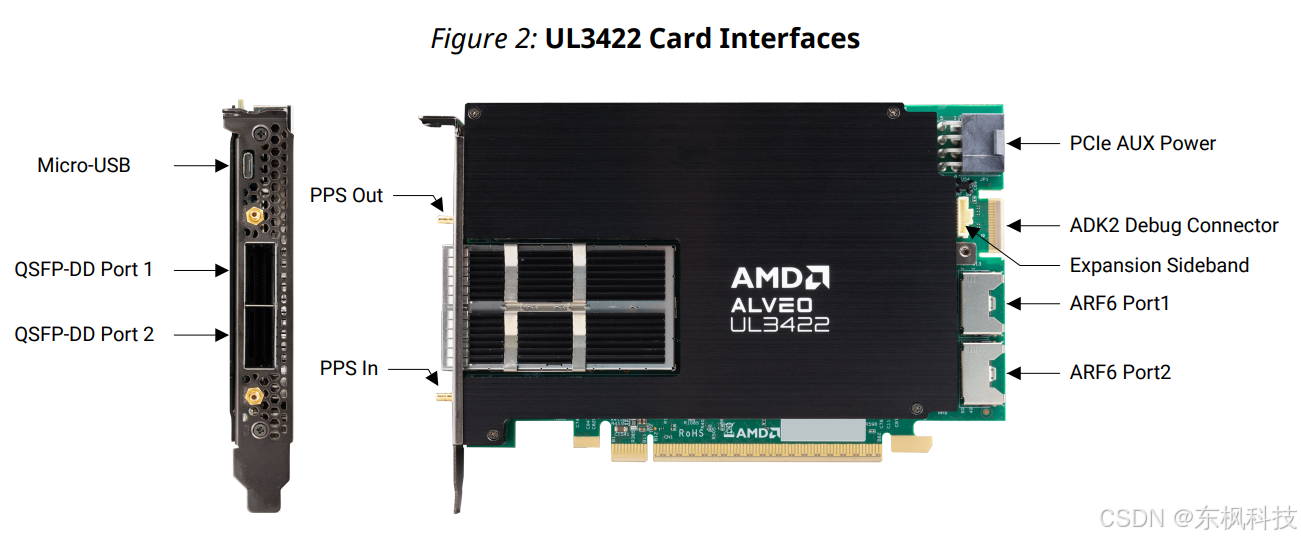

卡接口

框图

参考

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?