1. 背景

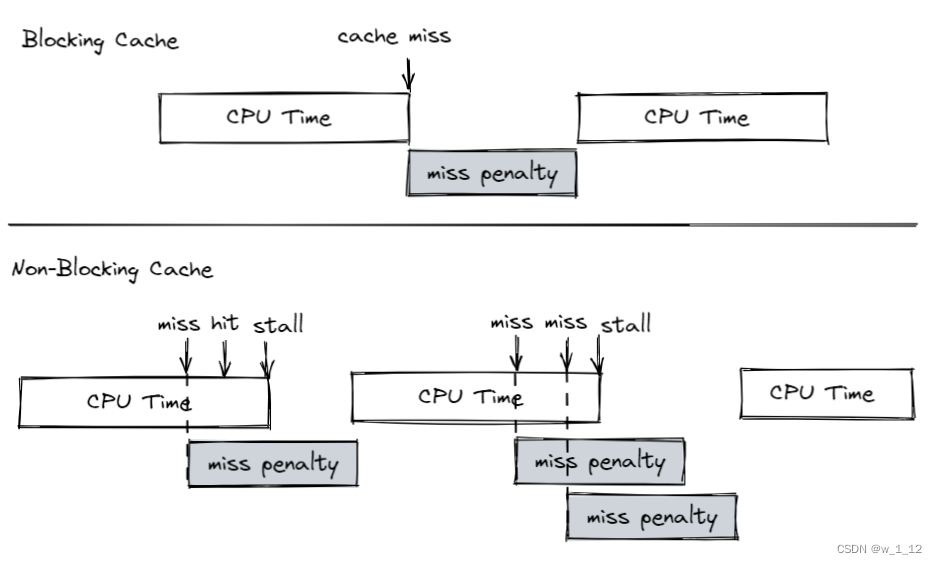

1.1 非阻塞缓存

I-Cache 只需要读取,且取指令要求串行的顺序,因此该结构不能简单地使用非阻塞的方式。

情况分析: 不管是 load 指令还是 store 指令,当发生 D-Cache 缺失时,D-Cache 和物理内存之间都需要交换数据。

发生 D-Cache 缺失后,仍可以执行后面的 load/store 指令;

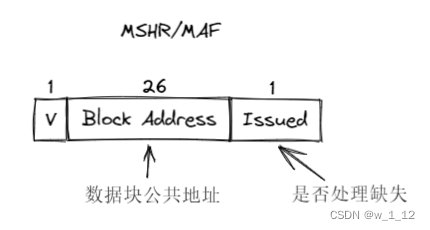

2 MSHR

MSHR(Miss Status Holoding Register)

美国 David Kroft 提出。当采用这种方式后,D-Cache 缺失有可能在不同的层级,因此会导致指令顺序与原始顺序不一样。

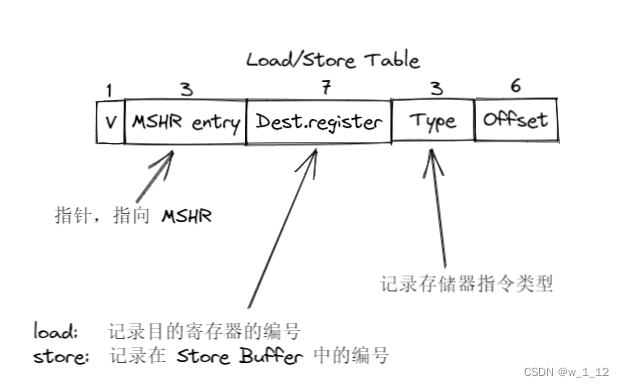

2.1 MSHR的存储方式

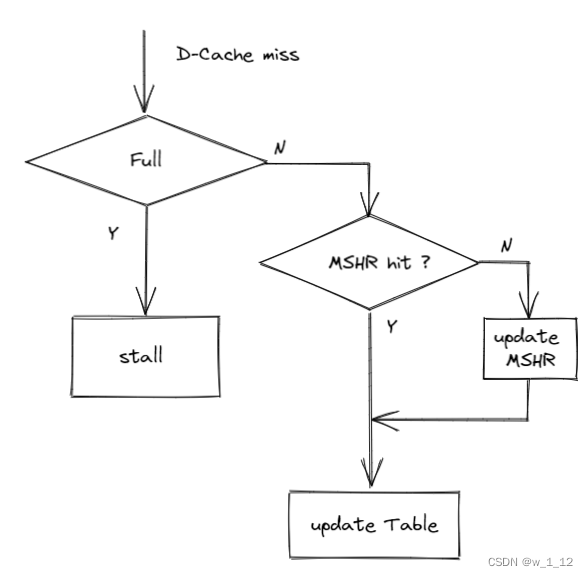

2.2 工作流程

当两个表中某个表满,则需要暂停读取指令,等待处理某个 miss

3 代价

需要比较电路和控制电路,以及 MSHR 存储。

在超标量处理器中,采用了分支预测和乱序执行,会导致D-Cache 确实的概率。

2070

2070

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?