按理说I2C同步时序,SCL高电平和低电平多长时间都应该没问题,为什么这里还要有占空比的参数

其实这个占空比是为了快速传输设计的

做个试验

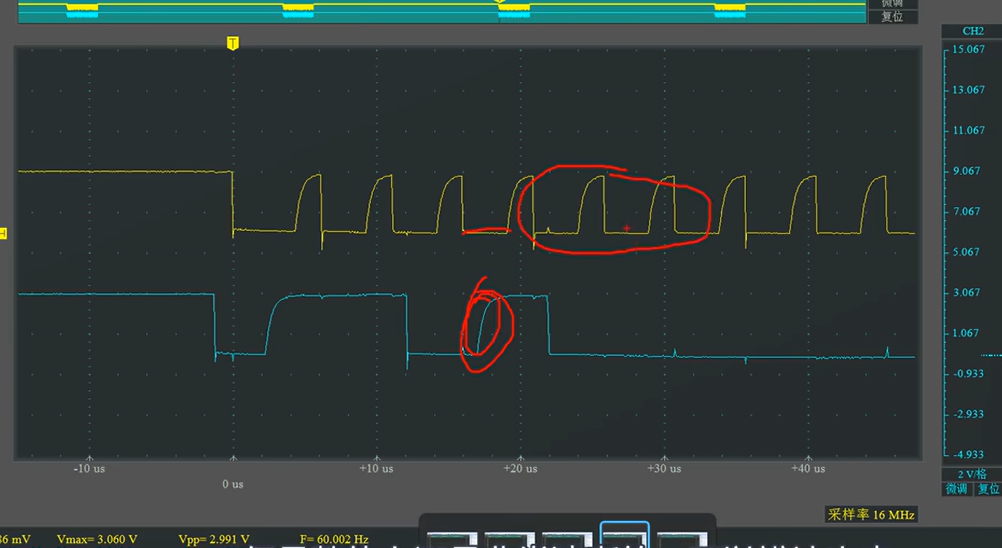

1.首先是50Khz ,上面是SCL,下面是SDA

是11010000,SCL频率50Khz 处于标准速度,低电平比高电平是1:1,也就是50%占空比的方波

2.这个图是100Khz的波形,仍然是标准速度,时钟占空比仍然是1:1

不过有个细节可以观察到SCL和SDA的下降沿,变化是非常快的

上升沿是缓慢上去的,这个原理可以联想到一个比喻就是这个线是通过弹簧默认上拉高电平,当我们输出低电平我们要用下拉,也就是无穷大的力,用力把杆子拽下来,由于拽下来的力非常大,所以下降沿就非常的果断和迅速,但是高电平我们是释放杆子,杆子通过弹簧拉回致高电平,弹簧是个弱上拉,所以这里的上升沿就有一个回弹的过程,波形就会相对缓慢上去

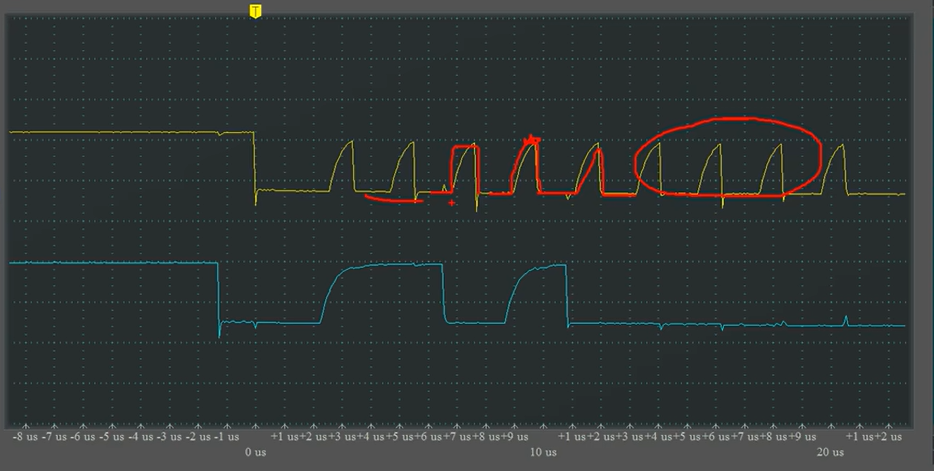

3.下面是101Khz的波形,101khz 进入了快速状态,这时I2C会对SCL占空比进行调节

低电平比高电平由原来的1:1变为大概2:1,如果不给他多分配时间,SDA有可能都来不及进行数据变化

4下图是400KHz波形

可以看出这里时钟的高电平,从这里开始释放SCL,SCL还没完全回弹到高电平,就被立刻拉下来,传输下一个数据了,所以整个SCL波形就变成三角形了,跟我们想象不大一样,我们想的是SCL释放,应该立刻回弹高电平,但是实际会有弯弯的上升,整个弯弯就拖了后腿,限制了I2C总线的最大传输速度

另外这里也可以看到在SCL低电平期间,数据变化也不是完全贴到下降沿,会有一些延时,所以这更有必要在低电平多分配一些时间了

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?