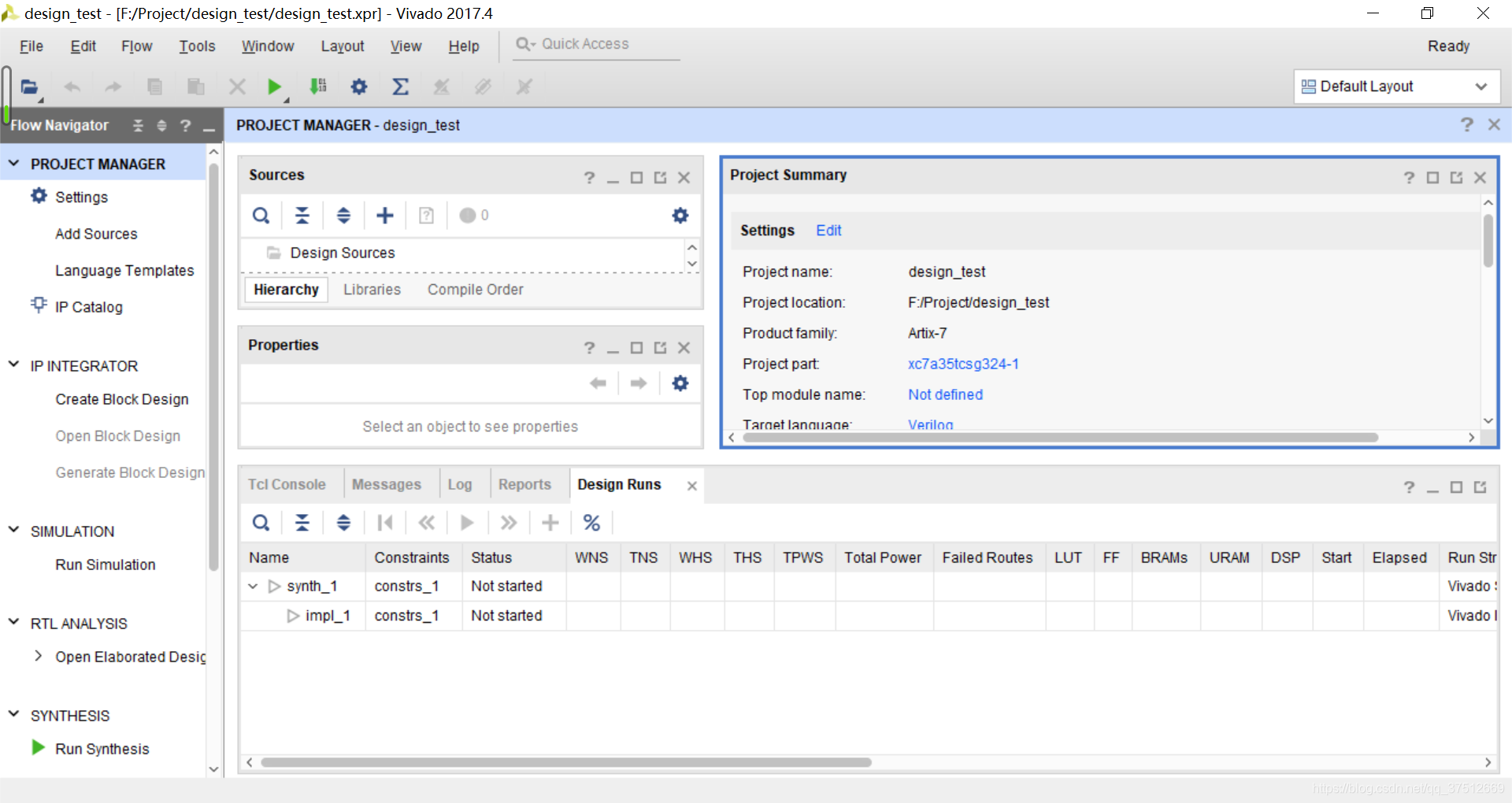

软件:Vivado2017.4 板卡:Ego1 型号:xc7a35tcsg324-1

三、基于Verilog来设计流水灯

1、打开Vivado,创建一个名为design_test的空白工程。

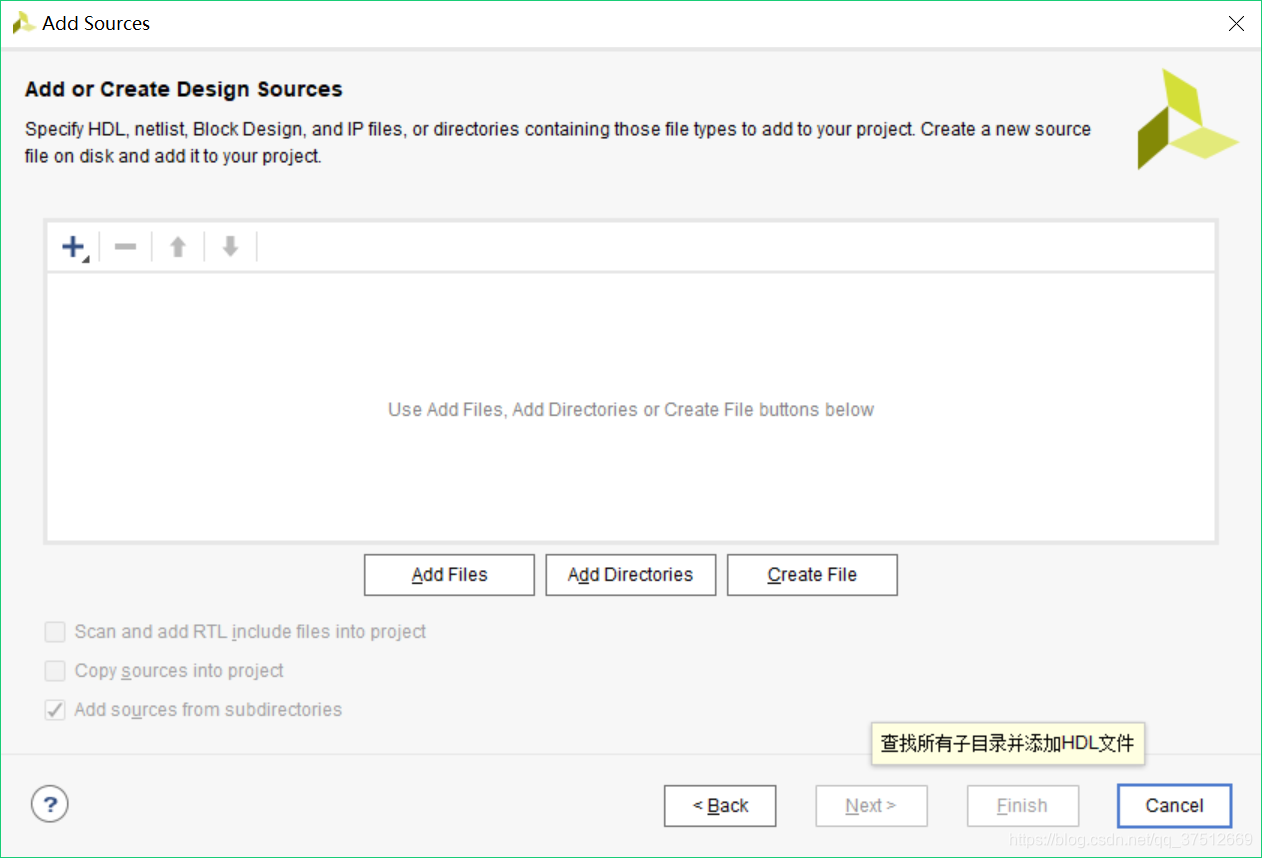

2、点击Add source或者Sources中的+号来添加或者创建一个设计源文件,点击Next。

3、点击Create File来创建一个空白的源文件,类型选择为Verilog,文件名为flowing_light。

4、点击Finish后,弹出Define Module窗口,直接OK然后Yes跳过,端口我们后续在代码中进行写入,先不定义。

4、点击Finish后,弹出Define Module窗口,直接OK然后Yes跳过,端口我们后续在代码中进行写入,先不定义。

5、在.v文件中写入流水灯源代码。

modu

本文介绍了如何使用Vivado 2017.4进行FPGA设计,通过创建名为design_test的工程,编写Verilog代码实现流水灯,并添加仿真文件进行验证。设计过程中包括创建源文件、编写模块代码、运行仿真、添加约束和生成比特流等步骤。

本文介绍了如何使用Vivado 2017.4进行FPGA设计,通过创建名为design_test的工程,编写Verilog代码实现流水灯,并添加仿真文件进行验证。设计过程中包括创建源文件、编写模块代码、运行仿真、添加约束和生成比特流等步骤。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?