D-PHY中的PHY是物理层(Physical)的意思,D是罗马数字500的意思,D-PHY的最初版本的设计目标是500Mbits/s,同理C-PHY和M-PHY中的C和M分别是罗马数字中的100和1000。

D-PHY中包含了高速模块和低功耗模块,载荷数据(图像数据)通过高速模块发送,控制和状态信息通过低功耗模块发送。低功耗模块有利于节省功耗,高速模块则有利于实现高清晰度照片质量数据信号要求的较高带宽。另外低功耗逃逸模式可以用于低速异步通信。

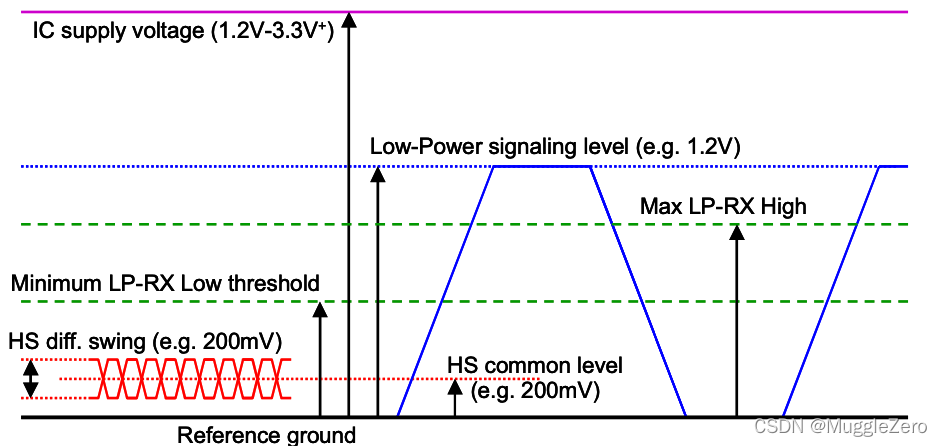

MIPI D-PHY协议定义了两种传输模式:高速模式(High Speed,HS)和低功耗模式(Low Power,LP),两种模式使用不同的传输电平和传输机制。HS模式和LP模式的电平如下图所示:

HS模式为差分信号传输,信号电平在100mV~300mV(200mV的压摆);LP模式下,为单端信号传输,信号电平在0~1.2V(1.2V压摆)。HS模式下,信号传输速度可达80Mbps~1Gbps(v1.0)或80Mbps~1.5Gbps(v1.1),采用源同步的传输方式,由主机(Master)设备向从机(Slave)设备提供DDR(Double Data Rate)时钟。LP模式下,信号传输速度为10Mbps,此时传输通道的差分线(HS模式下的)是两根独立的信号线。无论是HS模式还是LP模式,都采用LSB first,MSB last的传输方式。

HS模式下,信号传输速度较快,较低的压摆有利于提升传输速度,同时降低功耗和EMI;那么为什么LP模式下不用HS的传输机制呢?因为LP模式下,传输的信号速度较慢,较低的压摆不利于系统的稳定(如果采用100mV~300mV的电平,此时可能会有比较严重的过冲)。

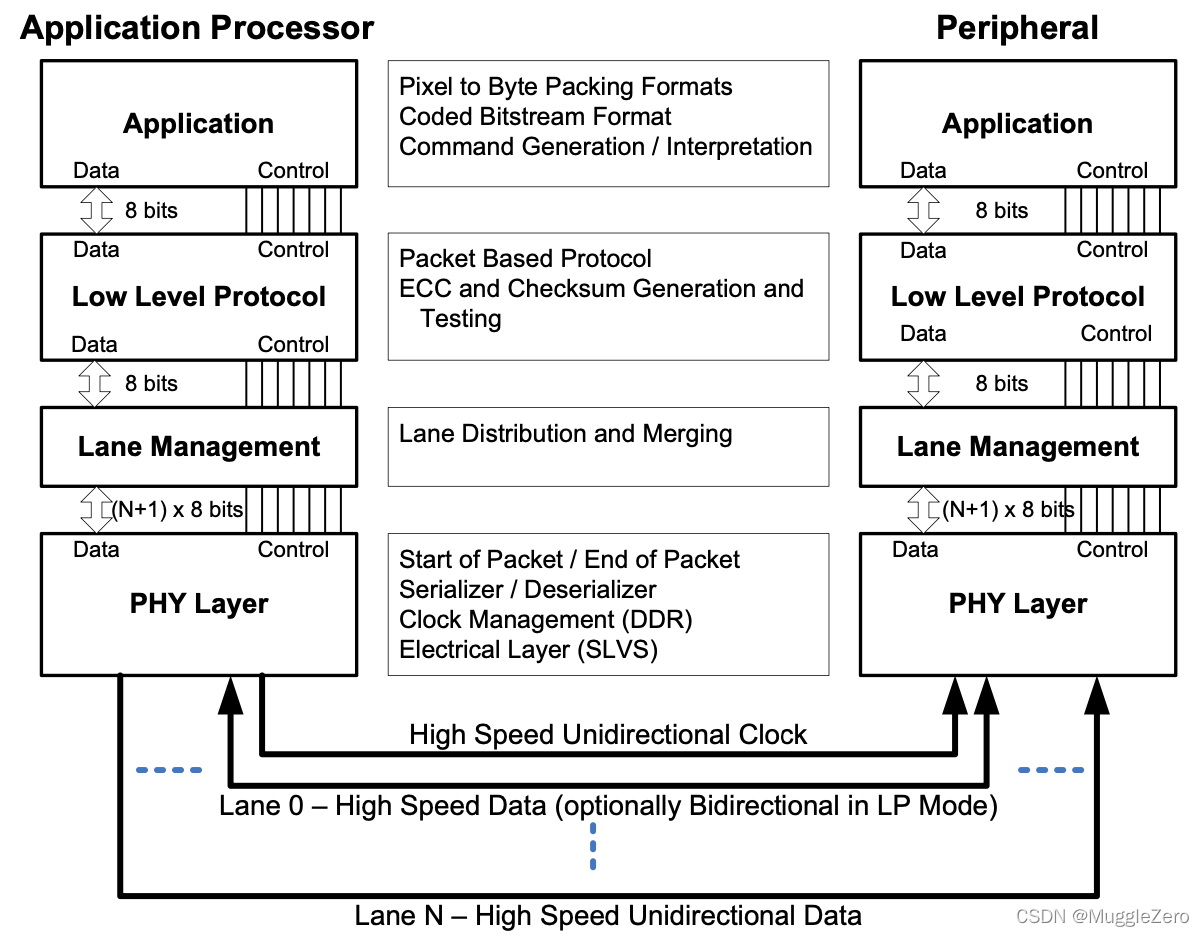

完整的MIPI的传输架构图如下:

左侧是一颗SOC的框架图,右侧是连接的外设框图。一般SOC的架构是APB总线+RGB数据->Protocol协议层->PHY物理层(Lanes)。而外设MIPI芯片,例如MIPI转接板芯片的逻辑则是PHY物理层->Protocol协议层->应用层(解析出RGB图像数据)。

D-PHY协议最多支持5个Lane(一个时钟Lane,4个数据Lane),最少需要两个Lane(一个时钟Lane,一个数据Lane)。

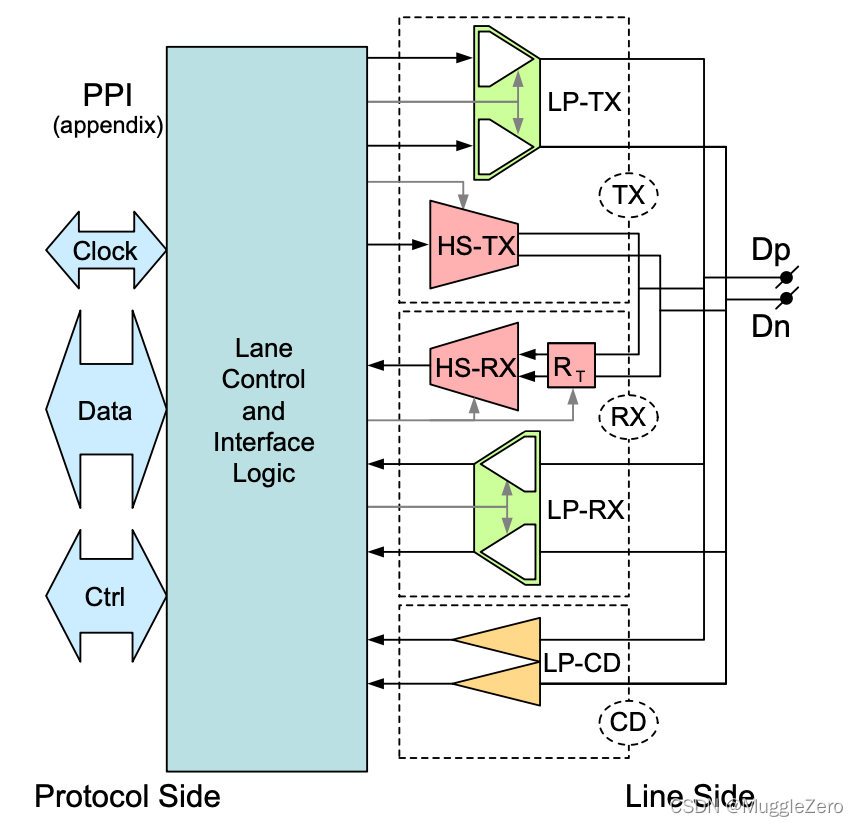

每个lane的PHY物理层配置如下图所示:

一个通用的PHY Lane中包含LP-TX、LP-RX、HS-TX、HS-RX和LP-CD模块,所有收发模块均共用同一个差分线Dp,Dn(在LP模式下,为两根单独的信号线)。整个Lane通过PPI接口(PHY Protocol Interface)与协议层相连(协议层->PHY LANE)。

LP-CD模块仅在存在于需要双向通信(Bidirectional)的系统中。

在LP模式下(包括Control Mode和Escape Mode),采用的是Spaced-One-Hot Coding机制。在该机制下,时钟可以从传输的数据中得以体现,因此不需要传输时钟。此时,用户可以根据实际需求,设置Clock Lane继续运行或者关闭以降低功耗。

LPDT模式(Low-Power Data Transmission)和ULPS模式(Ultra-Low Power State)都是Escape Mode的一种。

MIPI D-PHY协议包含高速和低功耗模块,适用于高速图像数据和低功耗控制信息传输。HS模式使用差分信号,速度可达1Gbps,而LP模式为单端信号,速度为10Mbps。协议支持HS和LP两种传输模式,HS模式利用差分信号和DDR时钟提高速度,LP模式使用Spaced-One-Hot Coding减少时钟传输。D-PHY最多支持5个Lane,最少需要2个Lane,每个Lane包含LP和HS收发模块。

MIPI D-PHY协议包含高速和低功耗模块,适用于高速图像数据和低功耗控制信息传输。HS模式使用差分信号,速度可达1Gbps,而LP模式为单端信号,速度为10Mbps。协议支持HS和LP两种传输模式,HS模式利用差分信号和DDR时钟提高速度,LP模式使用Spaced-One-Hot Coding减少时钟传输。D-PHY最多支持5个Lane,最少需要2个Lane,每个Lane包含LP和HS收发模块。

991

991

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?