tx1: 不增加TCP部分,传输有限数据

FPGA部分:

FPGA_Demo\Demo1\my_upp

初始值为2,触发后0-1024递增,

增加count变量控制UPP上传数组的个数:count<8’d66

DSP部分:(主要修改upp接收的内存大小)

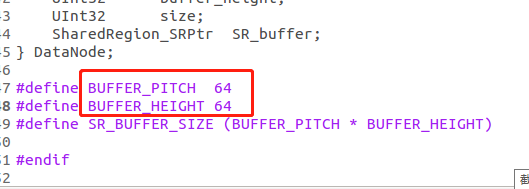

在文件 shared-protocol.h,原来是641024=64k,

现在修改大小为6464=4k

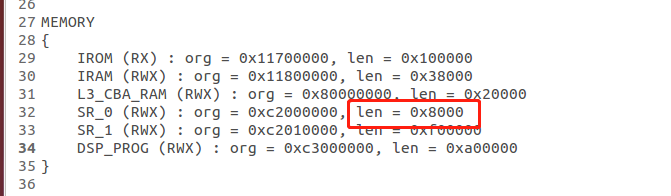

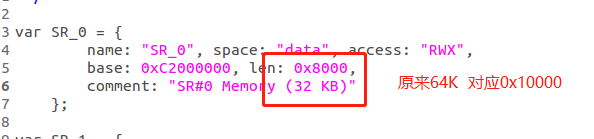

在shared- config.bld 和dsp-configuro-linker.cmd 均修改SR0

原来: SR_0 (RWX) : org = 0xc2000000, len = 0x10000

现在:32k

ARM部分:

删除了关于filesaver的部分, 在get upp data 之后增加了测试数组,用于遍历显示接收到的数据

//创建一个测试数组,遍历显示收到的数

int tst[SR_BUFFER_SIZE];

int k =0;

for(k=0;k<SR_BUFFER_SIZE;k++)

{

tst[k] = *(data+k);

printf("tst[%d]= %d\n",k,tst[k]);

}

测试结果:遍历数组为乱码,只显示4K

更改,改成FPGA数据固定的数据 FPGA传输10的时候,到ARM端打印出来是2560,十进制转化为十六进制,2560对应a00.

tx2: 加入TCP

第一步,只配置TCP,不收发,可以实现tx1的功能

第二步,加入收发,MATLAB显示0,10,0,0

更改:tx2.1

测试结果:ARM端和PC端显示的均为十进制的2560,对应十六进制的0a00

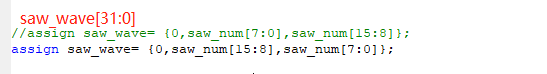

修改FPGA端的数据,发现ARM和PC机上显示数据一致,后来发现是数据特殊的原因

但是会出现FPGA数据和ARM数据不一致的现象,递增数不按递增数表示了

重新在tx1基础上更改,不改变TCP部分

tx3:恢复tx1所做的更改

shared 和dsp-configuro修改部分,

w2 : 之前传有限组数改成一直传,但是ARM端只接受其中一段,保留在数组中,直接把数组传给PC机

W1:目前为止最理想的配置,但仍然存在问题

FPGA端设置的如下:

ARM端创建的测试数组如下:(着重更改char!)

PC 端程序设置如下:

经测试发现,不管ARM端和FPGA端的数据格式如何变化,在PC端,小端打印出来的数据与ARM端打印出来的数据一致,大端“镜面对称” ,

测试结果如下:

9440

9440

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?